HEP-CCE

# Quantum Pattern Recognition for High-Luminosity Era

Illya Shapoval, Paolo Calafiura

Lawrence Berkeley National Laboratory

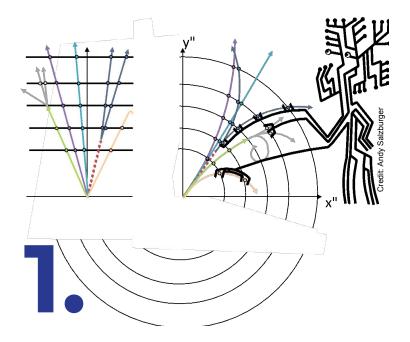

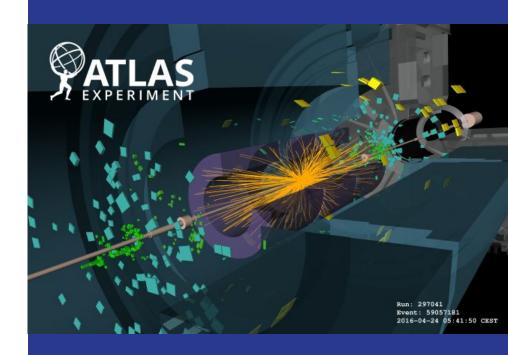

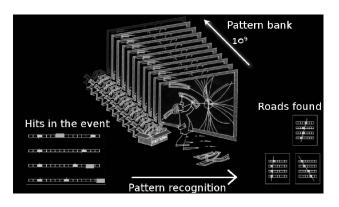

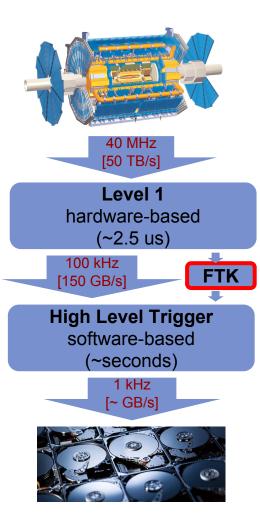

ATLAS Real-time Pattern Recognition

### **ATLAS Fast Tracker (FTK)**

LHC Run 2 (2015) - Run 3 (2023)

### A HARDWARE FOR REAL-TIME GLOBAL TRACK FINDING

### Requirements:

- ► Input: 10<sup>8</sup> channels

- ► Latency: ~100 us

- Frequency: @100 kHz

- ► Storage: 8 · 10³ AM custom ASIC chips

- Power: ~32 kW (+ cooling)

- Capacity: 10<sup>9</sup> track patterns

- ▶ Latency: average ~50 us, max ~180 us

# **Scalability of Associative Memory**

| Experiment                                         | LHC Run 2-3         |

|----------------------------------------------------|---------------------|

| LHC Luminosity (cm <sup>-2</sup> s <sup>-1</sup> ) | ~10 <sup>34</sup>   |

| Tracks/event                                       | ~500                |

| AM Capacity* (patterns)                            | 10 <sup>9</sup>     |

| AM Storage* (AM chips)                             | 8 · 10 <sup>3</sup> |

| Density* (patterns/chip)                           | 128k (65 nm)        |

<sup>\*</sup> Required by ATLAS physics and detector granularity

# **Scalability of Associative Memory**

| Experiment                                         | LHC Run 2-3         | HL-LHC (2026)                              |

|----------------------------------------------------|---------------------|--------------------------------------------|

| LHC Luminosity (cm <sup>-2</sup> s <sup>-1</sup> ) | ~10 <sup>34</sup>   | ~10 <sup>35</sup>                          |

| Tracks/event                                       | ~500                | 5000                                       |

| AM Capacity* (patterns)                            | 10 <sup>9</sup>     | [ <b>8</b> - <b>16</b> ] • 10 <sup>9</sup> |

| AM Storage* (AM chips)                             | 8 · 10 <sup>3</sup> | [2 - 4] · 8 · 10 <sup>3</sup>              |

| Density* (patterns/chip)                           | 128k (65 nm)        | ~512k (28 nm)                              |

<sup>\*</sup> Required by ATLAS physics and detector granularity

# **Scalability of Associative Memory**

| Experiment                                         | LHC Run 2-3         | HL-LHC (2026)                 | HE-LHC (2030s)    |

|----------------------------------------------------|---------------------|-------------------------------|-------------------|

| LHC Luminosity (cm <sup>-2</sup> s <sup>-1</sup> ) | ~10 <sup>34</sup>   | ~10 <sup>35</sup>             | ~10 <sup>36</sup> |

| Tracks/event                                       | ~500                |                               | ~50,000           |

| AM Capacity* (patterns)                            | 10 <sup>9</sup>     | [8 - 16] · 10 <sup>9</sup>    | ?                 |

| AM Storage* (AM chips)                             | 8 • 10 <sup>3</sup> | [2 - 4] · 8 · 10 <sup>3</sup> | ?                 |

| Density* (patterns/chip)                           | 128k (65 nm)        | ~512k (28 nm)                 | ?                 |

<sup>\*</sup> Required by ATLAS physics and detector granularity

- Location-addressable memory

- Pattern capacity: **O(N/n)**, where N is the total number of **bits**, and **n** the pattern length

- Slow recall (primitive cells and high address/word handling impedance)

- Low cost and low power dissipation

- Location-addressable memory

- Pattern capacity: **O(N/n)**, where N is the total number of **bits**, and **n** the pattern length

- Slow recall (primitive cells and high address/word handling impedance)

- Low cost and low power dissipation

- Associative memory (a.k.a content-addressable memory)

- Pattern capacity: **O(N/n)** in classical schemes

- Phopfield networks scale as O(N) (m≤kN, where 0.15≤k≤0.5)

- ► Fast recall (0(1) cycle ops) (cells with dedicated compare/combine circuits)

- High cost and high power dissipation

- Location-addressable memory

- Pattern capacity: **O(N/n)**, where N is the total number of **bits**, and **n** the pattern length

- Slow recall (primitive cells and high address/word handling impedance)

- Low cost and low power dissipation

- Associative memory (a.k.a content-addressable memory)

- ▶ Pattern capacity: **O(N/n)** in classical schemes

- Phopfield networks scale as O(N) (m≤kN, where 0.15≤k≤0.5)

- ► Fast recall (0(1) cycle ops) (cells with dedicated compare/combine circuits)

- High cost and high power dissipation

- Quantum associative memory

- Pattern capacity:  $O(2^N)$ , where N is the total number of qubits, and n the pattern length

- Parall time needs evaluation, high volatility with hardware technology

- Market costs are far from "ground state" yet, relaxation time is ~10-15 years

# 2. Quantum Associative Memory

### **Quantum Memory**

Represent pattern  $\xi^i \equiv (\xi_1, \xi_2, \dots, \xi_d)$  by a **basis state** in the Hilbert space of d quantum information units:

$$|\xi^i\rangle \equiv |\xi_1, \xi_2, \dots, \xi_d\rangle$$

▶ Represent  $\Xi$  - a set of N patterns - as **superposition** of the basis states:

$$|\Xi\rangle = \sum_{1}^{N} \alpha_i |\xi^i\rangle, \qquad \alpha_i \in \mathbb{C} \wedge \sum_{1}^{N} |\alpha_i|^2 = 1$$

# **QuAM Capacity**

QuAM features exponential storage capacity of  $2^d$  and requires  $2(d+1)^1$  qubits to operate  $2^d$ .

| Length of detector hit identifier (bits)           | 8                 | 16                | 32                |

|----------------------------------------------------|-------------------|-------------------|-------------------|

| Length of binary track pattern (bits) <sup>3</sup> | 64                | 128               | 256               |

| QuAM register (qubits)                             | 130               | 258               | 514               |

| QuAM capacity (patterns)                           | ~10 <sup>19</sup> | ~10 <sup>38</sup> | ~10 <sup>77</sup> |

<sup>&</sup>lt;sup>1</sup> C.A Trugenberger, Probabilistic Quantum Memories. Phys Rev. Lett. Vol 87, 6 (2001)

<sup>&</sup>lt;sup>2</sup> d is the pattern length

<sup>&</sup>lt;sup>3</sup>8 logical layers of the Inner Tracker

# **QuAM Capacity**

QuAM features exponential storage capacity of  $2^d$  and requires  $2(d+1)^1$  qubits to operate  $2^d$ .

| Length of detector hit identifier (bits)           | 8                 | 16                | 32                |

|----------------------------------------------------|-------------------|-------------------|-------------------|

| Length of binary track pattern (bits) <sup>3</sup> | 64                | 128               | 256               |

| QuAM register (qubits)                             | 130               | 258               | 514               |

| QuAM capacity (patterns)                           | ~10 <sup>19</sup> | ~10 <sup>38</sup> | ~10 <sup>77</sup> |

<sup>&</sup>lt;sup>1</sup> C.A Trugenberger, Probabilistic Quantum Memories. Phys Rev. Lett. Vol 87, 6 (2001)

<sup>&</sup>lt;sup>2</sup> d is the pattern length

<sup>&</sup>lt;sup>3</sup>8 logical layers of the Inner Tracker

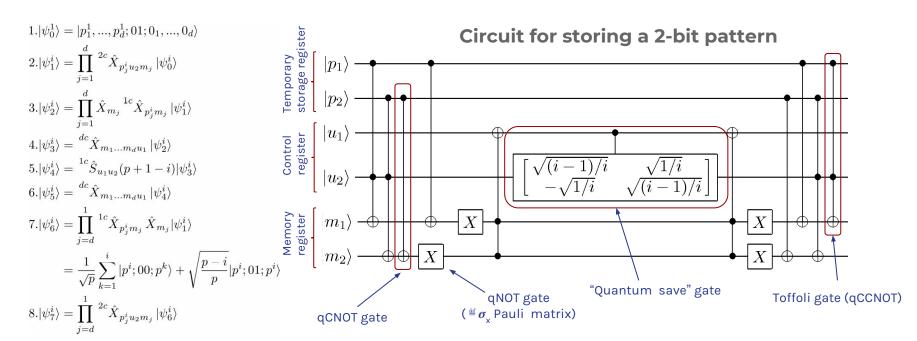

### **QuAM storage protocol**

A quantum circuit implementing iterative part of the storage protocol <sup>1</sup>.

$$\begin{aligned} 1.|\psi_{0}^{1}\rangle &= |p_{1}^{1},...,p_{d}^{1};01;0_{1},...,0_{d}\rangle \\ 2.|\psi_{1}^{i}\rangle &= \prod_{j=1}^{d} {}^{2c}\hat{X}_{p_{j}^{i}u_{2}m_{j}} |\psi_{0}^{i}\rangle \\ 3.|\psi_{2}^{i}\rangle &= \prod_{j=1}^{d} \hat{X}_{m_{j}} {}^{1c}\hat{X}_{p_{j}^{i}m_{j}} |\psi_{1}^{i}\rangle \\ 4.|\psi_{3}^{i}\rangle &= {}^{dc}\hat{X}_{m_{1}...m_{d}u_{1}} |\psi_{2}^{i}\rangle \\ 5.|\psi_{4}^{i}\rangle &= {}^{1c}\hat{S}_{u_{1}u_{2}}(p+1-i)|\psi_{3}^{i}\rangle \\ 6.|\psi_{5}^{i}\rangle &= {}^{dc}\hat{X}_{m_{1}...m_{d}u_{1}} |\psi_{4}^{i}\rangle \\ 7.|\psi_{6}^{i}\rangle &= \prod_{j=d}^{1c} \hat{X}_{p_{j}^{i}m_{j}} \hat{X}_{m_{j}} |\psi_{1}^{i}\rangle \\ &= \frac{1}{\sqrt{p}} \sum_{k=1}^{i} |p^{i};00;p^{k}\rangle + \sqrt{\frac{p-i}{p}} |p^{i};01;p^{i}\rangle \\ 8.|\psi_{7}^{i}\rangle &= \prod_{j=d}^{1} {}^{2c}\hat{X}_{p_{j}^{i}u_{2}m_{j}} |\psi_{6}^{i}\rangle \end{aligned}$$

# Circuit for storing a 2-bit pattern $|p_1\rangle$ $|p_2\rangle$ $|u_1\rangle$ $|u_2\rangle$ $|u_2\rangle$ $|u_3\rangle$ $|u_4\rangle$ $|u_5\rangle$ $|u_4\rangle$ $|u_5\rangle$ $|u_5\rangle$

<sup>&</sup>lt;sup>1</sup>C.A Trugenberger, Probabilistic Quantum Memories. Phys Rev. Lett. Vol 87, 6 (2001)

### **QuAM storage protocol**

A quantum circuit implementing iterative part of the storage protocol <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> C.A Trugenberger, Probabilistic Quantum Memories. Phys Rev. Lett. Vol 87, 6 (2001)

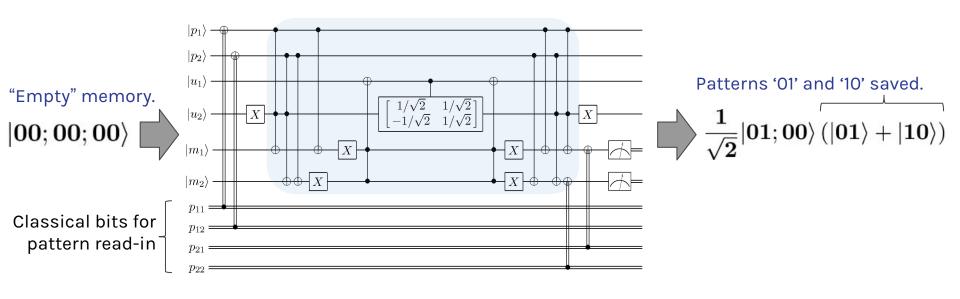

### **QuAM storage protocol**

2-bit patterns example

The end-to-end circuit for storing two 2-bit patterns: "01" and "10"

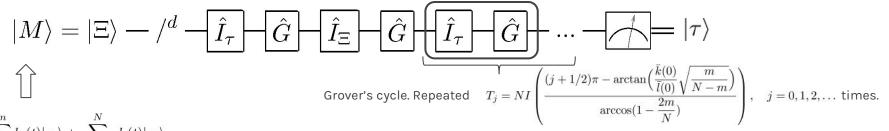

### **QuAM retrieval protocol**

### **Generalized Grover's algorithm\***

States that States that don't match the match the target

target pattern. pattern.

$\hat{I}_{ au}$  - "quantum oracle" operator. Inverts the phase of state representing the target pattern au.

$\hat{G}$  - Grover's diffusion operator. Inverts all amplitudes about the amplitudes average.

$\hat{I}_{\Xi}$  - Inverts phases of all terms originally present in memory.

### **QuAM retrieval protocol**

### **Generalized Grover's algorithm\***

$$|M

angle = |\Xi

angle - /^d - \hat{I}_{ au} - \hat{G} - \hat{I}_{\Xi} - \hat{G} + \hat{I}_{ au} - \hat{G} - \hat{I}_{\Xi} - \hat{G} + \hat{I}_{ au} - \hat{G} - \hat{I}_{ au} - \hat{I}_$$

$$\sum_{i=1}^m k_i(t)|x_i\rangle + \sum_{i=m+1}^N l_i(t)|x_i\rangle$$

States that State match the matc target pattern. State

States that don't match the target pattern.

#

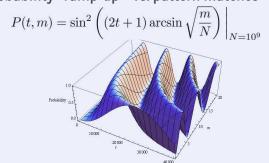

### Probability "ramp-up" vs. pattern matches

Peak probability vs. pattern matches and memory capacity

$$P(m,N) = \sin^2\left((2t+1)\arcsin\sqrt{\frac{m}{N}}\right)\Big|_{t=T_j}$$

$$m = 1, N = 10^9 : T_0 = 24836, P_{max} = 0.99999999999955568$$

$m = 20, N = 10^9 : T_0 = 5553, P_{max} = 0.9999999991404647$

Note: neither quantum noise, nor probabilistic memory cloning operations, are taken into account here.

$<sup>\</sup>hat{I}_{ au}$  - "quantum oracle" operator. Inverts the phase of state representing the target pattern au.

$<sup>\</sup>hat{G}\,$  - Grover's diffusion operator. Inverts all amplitudes about the amplitudes average.

$I_{\Xi}$  - Inverts phases of all terms originally present in memory.

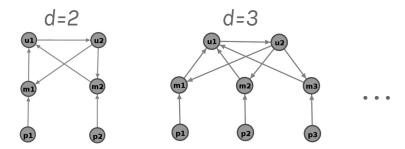

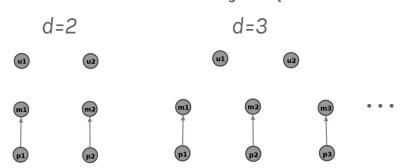

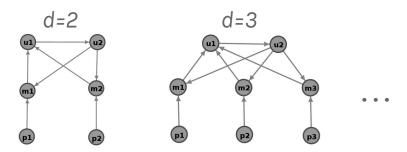

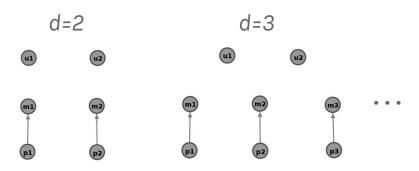

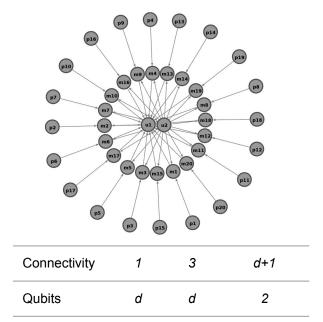

# Topological complexity of QuAM<sup>1</sup>

Storage connectivity requirements

Retrieval connectivity requirements

<sup>&</sup>lt;sup>1</sup> **(p)**, **(u)** and **(m)** nodes represent qubits from temporary storage, control and memory registers. **d** - pattern length

# Topological complexity of QuAM<sup>1</sup>

Storage connectivity requirements

Retrieval connectivity requirements

<sup>&</sup>lt;sup>1</sup> (p), (u) and (m) nodes represent qubits from temporary storage, control and memory registers. d - pattern length

# Topological complexity of QuAM<sup>1</sup>

Storage connectivity requirements

Retrieval connectivity requirements

### **Cumulative** QuAM requirements

d=20 (~ current pattern length in ATLAS)

<sup>&</sup>lt;sup>1</sup> **(p)**, **(u)** and **(m)** nodes represent qubits from temporary storage, control and memory registers. **d** - pattern length

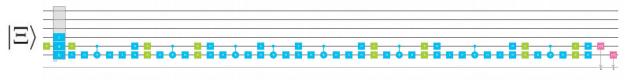

### **QuAM on QISKit**

### **QISKit** - Quantum Information Software Kit

An open source project comprising Python SDK, API and OpenQASM for implementing quantum algorithms on **IBM Quantum Experience (QE)** hardware and simulators.

### Supported backends:

- ► IBM QE cloud-based quantum chips [5Q Sparrow/Raven, 16Q Albatross, 20Q]

- Local/remote simulators [with realistic noise models]

### **QuAM on QISKit**

### **QISKit** - Quantum Information Software Kit

An open source project comprising Python SDK, API and OpenQASM for implementing quantum algorithms on **IBM Quantum Experience (QE)** hardware and simulators.

### Supported backends:

- IBM QE cloud-based quantum chips [5Q Sparrow/Raven, 16Q Albatross, 20Q]

- Local/remote simulators [with realistic noise models]

QuAM storage circuit generator [implemented]

Ex.: complete circuit for encoding three 2-bit patterns

QuAM retrieval circuit generator [being tested]

Ex.: complete circuit for retrieving one 2-bit pattern

Storage QASM

### Retrieval QASM

# **3**.

**Challenges and Opportunities**

# Challenges and Opportunities

### Hardware

QuAM demonstrated on

- NMR systems

- Optical systems

- D-Wave system

for low-order patterns.

High-order patterns require higher qubits connectivity and compliant processor topology.

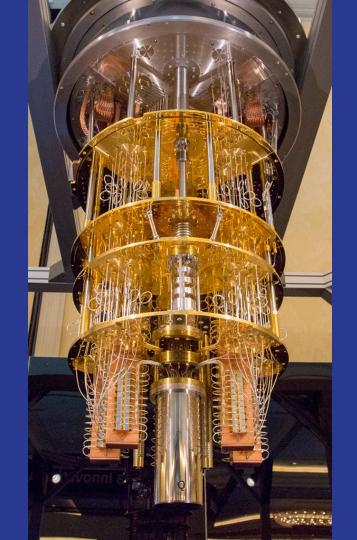

# **Emerging Quantum Technologies**

| Qua                                                                  | antum Chip | Qubits | Announced       | Qubit Archetype                     | Computing<br>Model   |

|----------------------------------------------------------------------|------------|--------|-----------------|-------------------------------------|----------------------|

| D-Wave 2000Q                                                         | D. Craw    | 2048   | 01/2017         | Superconducting <b>flux</b> qubits  | Quantum<br>annealing |

| IBMO IBMO                                                            | ISMQ       | 20     | 11/2017         | Superconducting transmon qubits     | Quantum              |

| IBM 20Q and 50Q                                                      |            | 50     | 11/2017 (tests) |                                     | circuits             |

| Rigetti 19Q                                                          |            | 19     | 12/2017         | Superconducting transmon qubits     | Quantum<br>circuits  |

| Intel Tangle Lake                                                    |            | 49     | 01/2018 (tests) | Superconducting qubits <sup>1</sup> | Quantum<br>circuits  |

| $\langle \mathbf{G}   \mathbf{oogl}   \mathbf{e}  angle$ Bristlecone |            | 72     | 03/2018 (tests) | Superconducting transmon qubits     | Quantum<br>circuits  |

| UC Berkeley QNL                                                      | ralay ONII | 4 (8)  | 2017            | Superconducting                     | Quantum<br>circuits  |

|                                                                      |            | 64     | 2022 ?          | transmon qubits                     | Circuits             |

<sup>&</sup>lt;sup>1</sup> Archetype of superconducting qubits is not disclosed. Also investing in spin qubits in silicon.

# **Emerging Quantum Technologies**

| Qua                                                                  | antum Chip | Qubits | Announced       | Qubit Archetype                     | Computing<br>Model   |

|----------------------------------------------------------------------|------------|--------|-----------------|-------------------------------------|----------------------|

| D-Wave 2000Q                                                         | DIAMENA    | 2048   | 01/2017         | Superconducting <b>flux</b> qubits  | Quantum<br>annealing |

| IBM 20Q and 50Q                                                      | IBMQ       | 20     | 11/2017         | Superconducting transmon qubits     | Quantum<br>circuits  |

| IDIVI ZUQ AITU JUQ                                                   |            | 50     | 11/2017 (tests) |                                     | Circuits             |

| Rigetti 19Q                                                          |            | 19     | 12/2017         | Superconducting transmon qubits     | Quantum<br>circuits  |

| Intel Tangle Lake                                                    |            | 49     | 01/2018 (tests) | Superconducting qubits <sup>1</sup> | Quantum<br>circuits  |

| $\langle \mathbf{G}   \mathbf{oogl}   \mathbf{e}  angle$ Bristlecone |            | 72     | 03/2018 (tests) | Superconducting transmon qubits     | Quantum<br>circuits  |

| UC Berkeley QNL                                                      |            | 4 (8)  | 2017            | Superconducting                     | Quantum<br>circuits  |

|                                                                      |            | 64     | 2022 ?          | transmon qubits                     | Circuits             |

<sup>&</sup>lt;sup>1</sup> Archetype of superconducting qubits is not disclosed. Also investing in spin qubits in silicon.

# **Challenges and Opportunities**

### Hardware

Functional trade-offs

QuAM demonstrated on

- NMR systems

- Optical systems

- ► D-Wave system for low-order patterns. High-order patterns require higher qubits connectivity and compliant processor topology.

AM generates, completes, and validates track patterns:

QuAM completes and validates track patterns:

# **Challenges and Opportunities**

### Hardware

Functional trade-offs

Memory persistence

QuAM demonstrated on

- NMR systems

- Optical systems

- ► D-Wave system for low-order patterns. High-order patterns require higher qubits connectivity and compliant processor topology.

AM generates, completes, and validates track patterns:

QuAM completes and validates track patterns:

Memory state collapses with each query.

Repetitive re-initialization is a show stopper. A possible solution may employ probabilistic cloning of memory reducing efficiency.

### Summary

- QC paradigm can yield asymmetrical advantages in handling certain challenges of HL/HE HEP real-time track pattern recognition

- QuAM features:

- Exponential storage capacity

- Optimal QA for pattern recall

- Current status:

- Theoretical analysis of QuAM properties completed

- Memory initialization iterations

- Recall probability bounds

- Topological complexity analysis

- Storage/retrieval quantum circuit generators implemented in QISKit

- Ready to run on real quantum hardware

- Coming soon:

- QuAM on the latest quantum hardware (targeting IBM QE chips)

- QuAM performance tests (timing, efficiency)