# Superconductor Electronics Fabrication Process with MoN<sub>x</sub> Kinetic Inductors and Self-Shunted Josephson Junctions

Sergey K. Tolpygo, Vladimir Bolkhovsky, Daniel E. Oates, Ravi Rastogi, Scott Zarr, Alexandra L. Day, Terence J. Weir, Alex Wynn, and Leonard M. Johnson

21 September 2017

#### **Outline**

- Introduction

- MIT LL superconductor electronics fabrication

- Current SFQ5ee process node

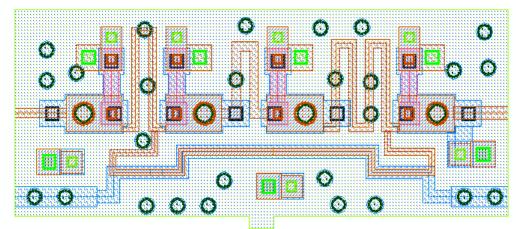

- Benchmark circuits at 10<sup>6</sup> JJ scale

- Very Large Scale Integration (VLSI) and scaling limiters

- Resistively shunted junctions

- Geometrical (magnetic) inductors

- Process development directions

- Self-shunted high- $J_c$  junctions

- Kinetic inductors

- Linewidth reduction to 250 nm and below

- Conclusion

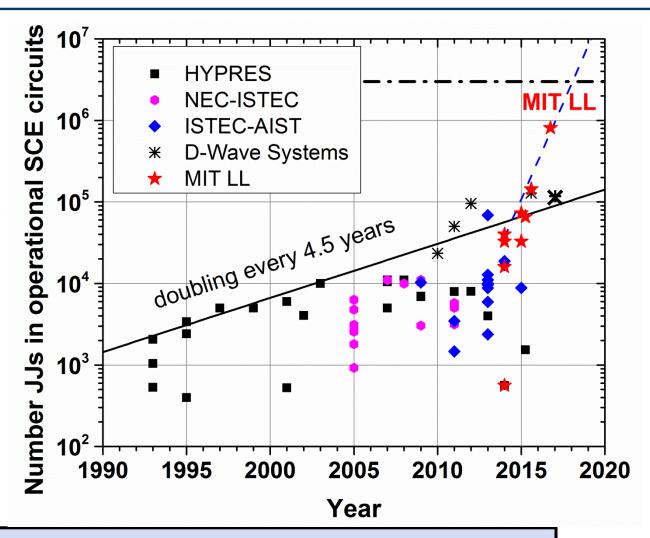

# **Superconducting Electronics Scaling Trend**

- JJ count number of JJs in demonstrated circuits is a good metric of progress

- MIT LL/Stony Brook U. circuits with 810k resistively shunted Josephson junctions and JJ density of 1.33·10<sup>6</sup> cm<sup>-2</sup> is the current World Record

- 80x increase in integration scale during four years demonstrated

- The maximum JJ density in the current technology nodes is ~ 3×10<sup>6</sup> JJs/cm<sup>2</sup>

- New technology developments are required to go beyond 10M JJs

MIT LL technology enables very large scale integration of superconducting circuits

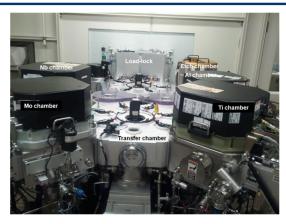

#### MIT LL Microelectronics Laboratory SCE Foundry

SCE Fab Leverages Facilities and Toolset of 90-nm CMOS Foundry in Microelectronics Lab

- Photolithography

- 248-nm stepper (Canon) current process nodes

- 193-nm scanner (ASML) for future nodes

- Photoresist processing and wafer cleaning tools

- Metal and dielectric deposition and etching tools

- Chemical-mechanical polishing

- Metrology tools: SEMs; film thickness, resistivity, and film stress mapping tools, etc.

Dedicated Tools Added to Enhance 200-mm SCE Fab Processing and Capabilities

- Sputter deposition tools for Nb, Mo, MoN<sub>x</sub>, NbTiN<sub>x</sub>

- High-density plasma (HDP) metal and dielectric etchers

- Low-temperature dielectric deposition tools

- HDP gap fill and interlayer dielectric deposition

- PECVD dielectric

- KLA-Tencor Altair defect inspection tool

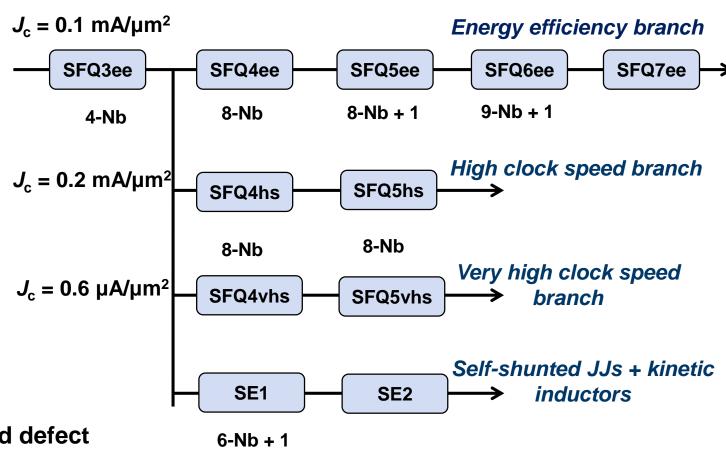

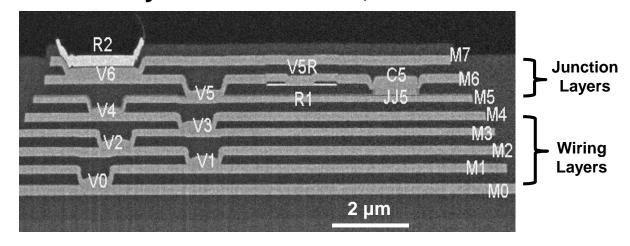

### MIT LL Current Technology Node SFQ5ee

#### **Process Features**

Junctions: Nb/AlO<sub>x</sub>-Al/Nb; J<sub>c</sub> = 0.1 and 0.2 mA/μm<sup>2</sup>

Min JJ size: 700 nm

Superconducting layers: 9

8 niobium wiring layers

1 layer of MoN<sub>x</sub> (kinetic inductors)

Resistors: 2 Ω/sq or 6 Ω/sq

Min wiring linewidth: 350 nm

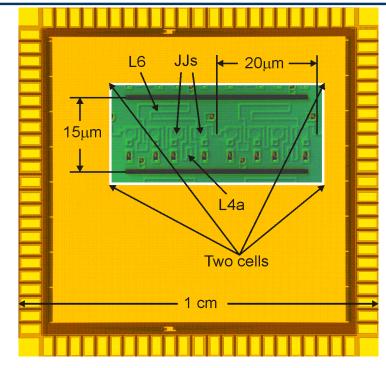

- AC-biased shift register: 202,280 bits

- 809,120 resistively shunted 1.25-µm² Josephson junctions – World record in JJ count

- Over 4 million inductors

- Fully operational; margins of all bit cells measured

- Integration scale: ≈ Intel's Pentium II, 0.8-µm process,

3.1M transistors on 294 mm² chip

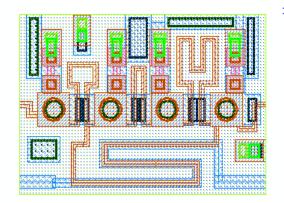

# SFQ6ee Process Node (1st Run Completed in Aug. 2017)

10 superconducting layers: 9 niobium + 1  $MoN_x$  (kinetic inductors) Pairs of stacked vias; smaller linewidth, surround, and spacing

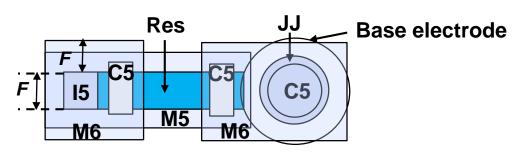

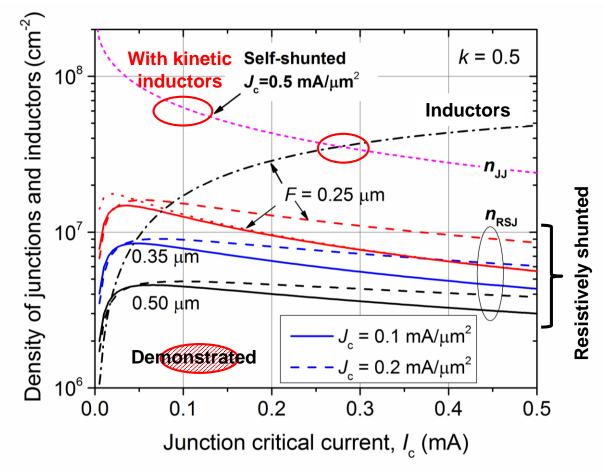

#### **SFQ Circuit Density Limiters: Junctions**

- The maximum circuit density is currently determined by the area of resistively shunted Nb/AlO<sub>x</sub>-Al/Nb Josephson junctions (RSJ) and inductors

- Resistor area:  $A_R \sim (R_s/R_{sq})F^2 + 27F^2$ , where F is the minimum feature size

- Inductor area:  $A_L = 2F(L/\ell) + 18F^2$ , where  $\ell$  is inductance per unit length

- Implementing self-shunted (high- $J_c$ ) junctions can increase JJ density by ~ 2× over the current 350-nm technology node with RSJs and by ~4× in 250-nm node

- Technology node with two layers of Josephson junctions has been developed at MIT LL

Resistively shunted junction

#### Shift Register Bit: 17 µm x 40 µm = 680 µm<sup>2</sup> in Gen 1

Gen 2

15  $\mu$ m x 20  $\mu$ m = 300  $\mu$ m<sup>2</sup>

Gen 3

Self-shunted JJs with  $J_c$  = 0.5 mA/ $\mu$ m<sup>2</sup> 10  $\mu$ m x 15  $\mu$ m = 150  $\mu$ m<sup>2</sup> Linewidth: 350 nm

Density: 2.7×10<sup>6</sup> JJ/cm<sup>2</sup>

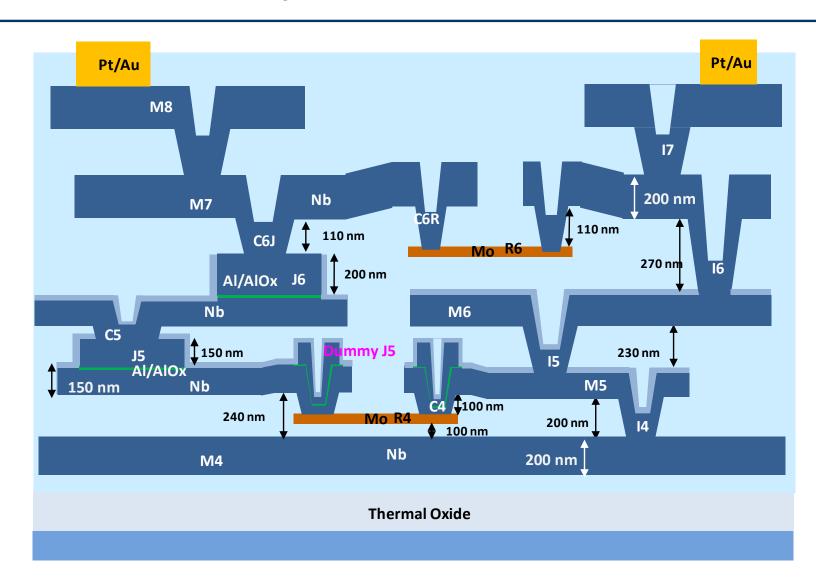

## MIT LL Process With Two Layers of Junctions

#### **Process SE1**

- Two layers of Nb/AlO<sub>x</sub>-Al/Nb junctions (J5 and J6)

- Two layers of shunt resistors (R4 and R6): 2 Ω/sq and/or 6 Ω/sq

- Five planarized Nb layers

- First wafer lot completed in Sept. 2017

- Plan to add more Nb layers and bias kinetic inductors

- Provides 2x increase in circuit density

### **SFQ Circuit Density Limiters: Junctions and Inductors**

- Each JJ needs an inductor  $L \sim \frac{\beta_L \Phi_0}{2\pi I_c}$ , where  $\beta_L \sim$

- 2 3 is the cell design parameter

- Inductor area  $A_{L} = 2F(L/\ell) + 18F^{2}$ , where  $\ell$  is inductance per unit length,  $\ell < 1$  pH/ $\mu$ m

- Max circuit density is achieved when inductor density matches JJ density,  $n_L \sim n_{JJ}$

- Two or three layers of inductors can be used

- Limits on minimum spacing and # of layers due to cross talk

- With self-shunted JJs, max circuit density becomes limited by the area of cell inductors

- Solution: replace geometrical (magnetic) inductors with low ℓ by compact kinetic inductors with L<sub>¬</sub>~ 4 pH/sq

- Implementation of self-shunted JJs and kinetic inductors can increase circuit density by more than 10x over the current 350-nm technology node

F – minimum feature size  $I_c$  range of JJs used: 0.05 mA to 0.25 mA Most often used:  $I_c$  ~ 0.125 mA

#### **Process Development Directions**

- Reduction of the linewidth to 250 nm and below

- Nb and NbTiN wiring

- Mo and MoN<sub>x</sub> resistors

- Kinetic inductors

- MoN<sub>x</sub> and NbTiN

- Self-shunted high-J<sub>c</sub> junctions

- Nb/AlO<sub>x</sub>-Al/Nb

- Nb/Si:Nb/Nb

- Multiple (two) layers of junctions

- Stud vias and Damascene process

- Etched Nb pillars

- PECVD and PEALD: NbN<sub>x</sub>, NbTiN<sub>x</sub>, MoN<sub>x</sub>

- Investigation of defects, circuit yield, and defect reduction

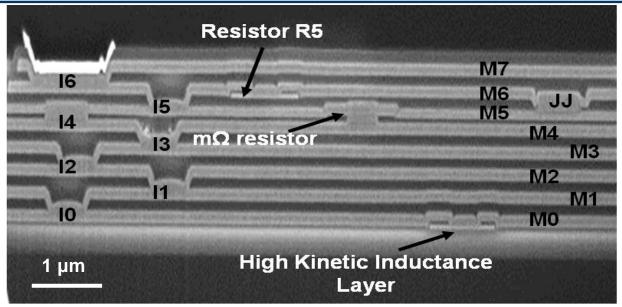

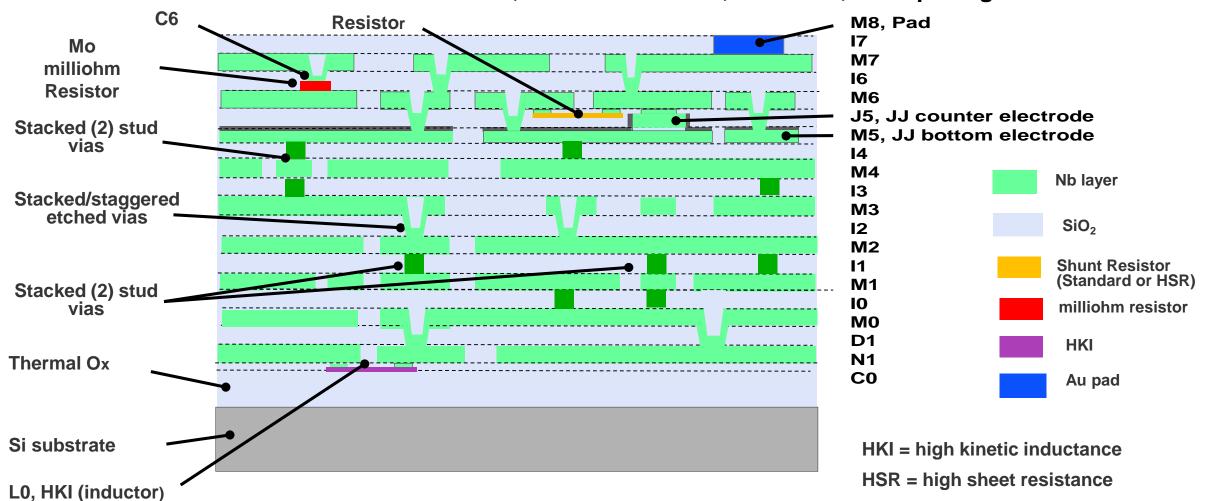

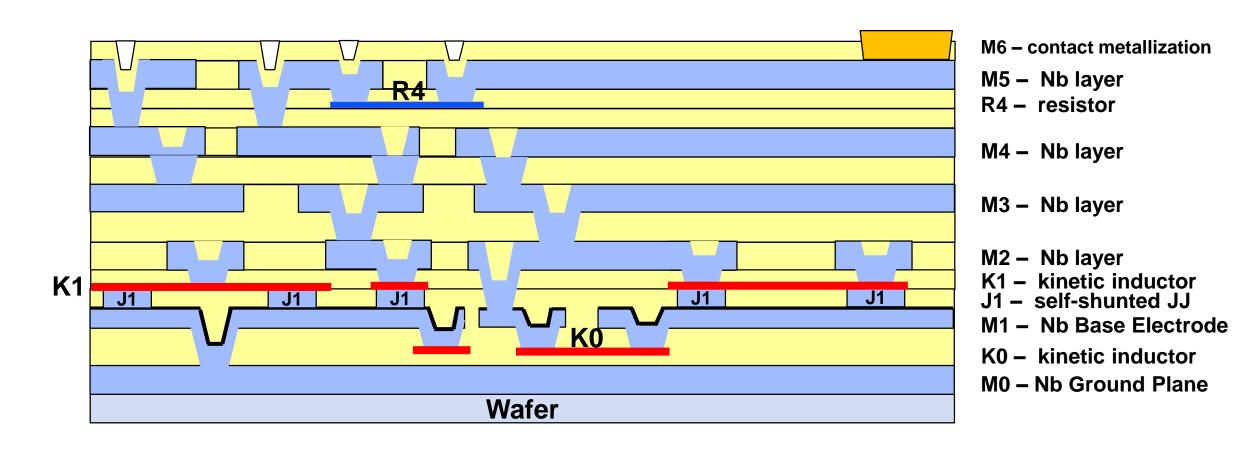

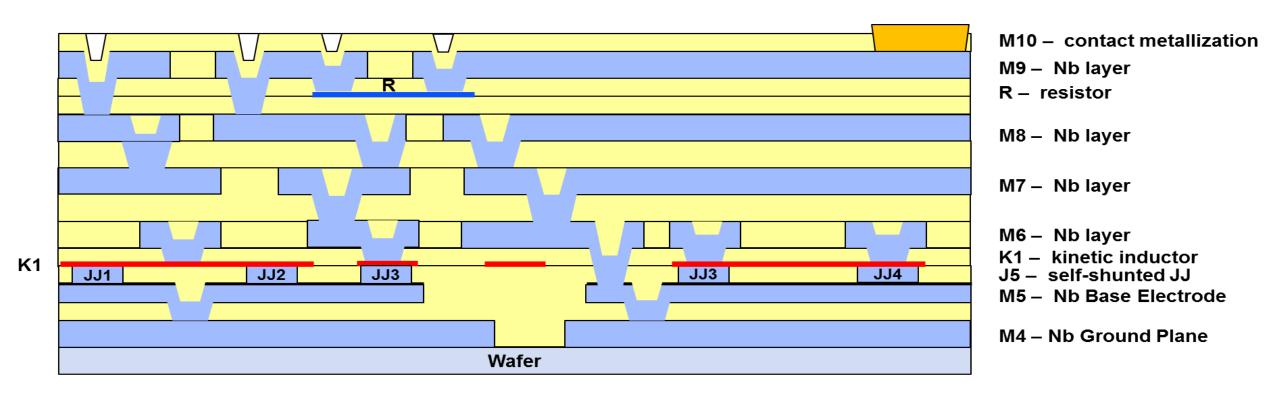

#### **Process Cross Section**

Process SE2: 1 layer of self-shunted JJs, 1 or 2 layers of kinetic inductors, six Nb layers, 1 layers of resistors

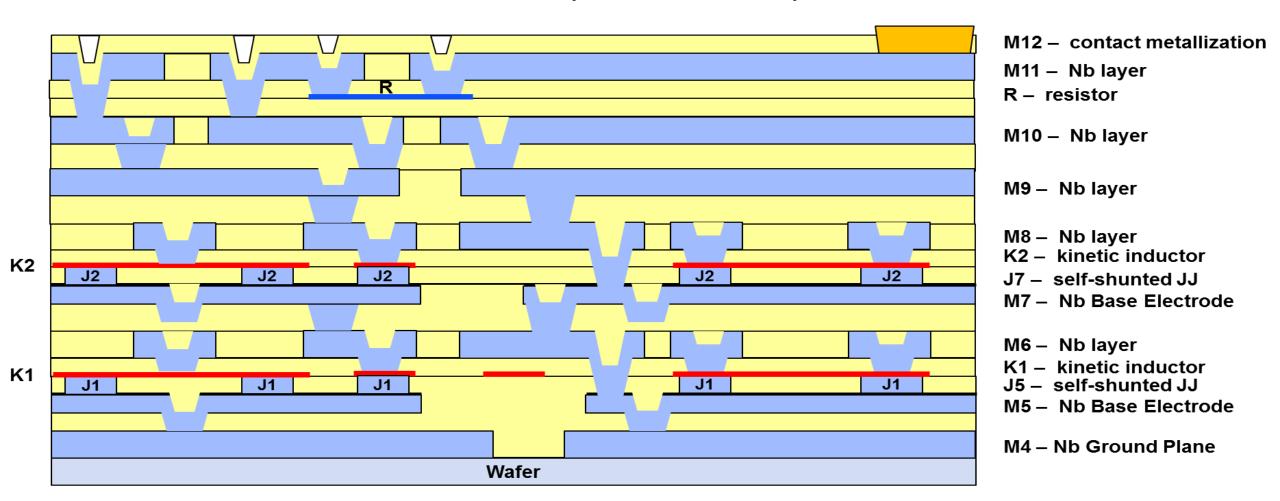

#### **Target Process Cross Section**

2 layer of self-shunted JJs, eight Nb layers, 2 layers of kinetic inductors, 1 layer of resistor (or bias inductors)

# Self-Shunted High-J<sub>c</sub> Junctions

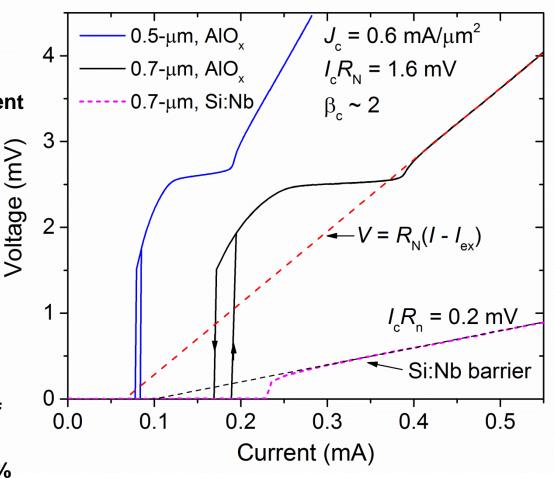

- At  $J_c \approx 0.6 \text{ mA/}\mu\text{m}^2$ , Nb/AlO<sub>x</sub>-Al/Nb tunnel junctions become self-shunted

- $-V_c \sim 1.6 \text{ mV}$

- $-\beta_c \sim 2$

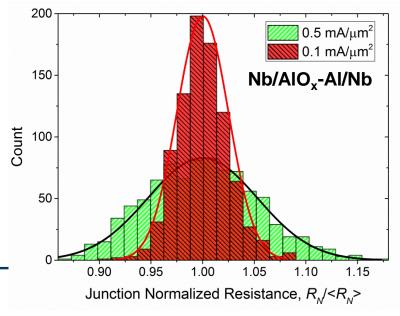

- 1σ<sub>Ic</sub> ~ 5% for 0.5-μm dia JJs ( $I_c$  ≈ 85 μA) needs improvement

- Self-shunted Nb/Si<sub>1-x</sub>Nb<sub>x</sub>/Nb junctions, x = 0.1

- $V_c = 0.2$  mV, a factor of 8 lower max clock frequency

- $-\beta_{\rm c}\sim 1$

- No advantages over the tunnel junctions found so far

On-wafer distribution of 0.7-µm JJs

$$J_{\rm c} = 0.1 \text{ mA/}\mu\text{m}^2$$

;  $1\sigma = 2.3\%$

$J_c = 0.5 \text{ mA/}\mu\text{m}^2$ ;  $1\sigma = 5.3\%$

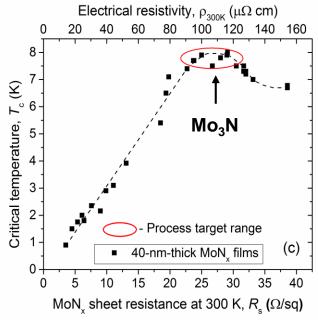

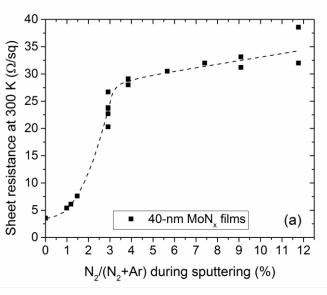

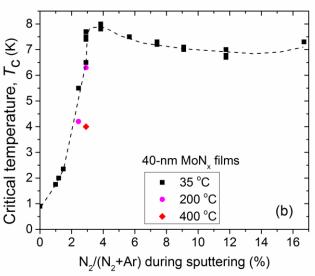

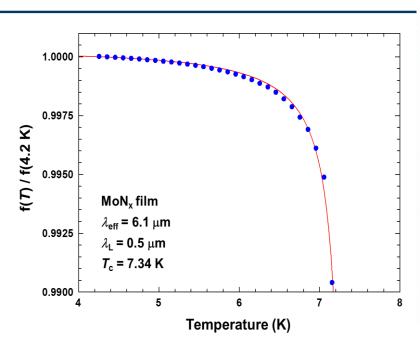

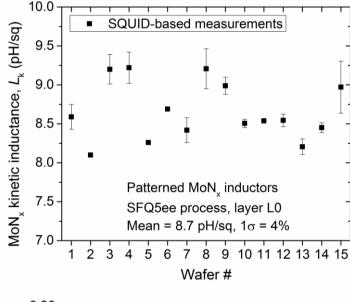

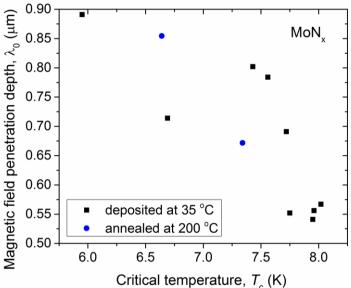

# Fabrication and Properties of MoN<sub>x</sub> Films

#### Amorphous MoN<sub>x</sub> films

- Highest  $T_c \sim 8 \text{ K}$

- Optimal composition for inductors  $x \approx 0.33$

- $J_c = 4.10^6 \text{ A cm}^{-2}$

- Reactive sputtering of Mo in N<sub>2</sub>/Ar

- Room-*T* deposition

- 200 mm wafers

- Thickness uniformity  $1\sigma = 2\%$

- Optimum resistivity 110 μΩ cm

- Ti/MoN<sub>x</sub>/Ti inductors

- London penetration depth at 4.2 K: 510 nm

- Sheet inductance: 8 pH/sq at 40 nm

- On-wafer uniformity  $1\sigma = 2.7\%$

- Wafer-to-wafer inductance variation 1σ = 4%

- Kinetic inductor flux storage per unit length:

$LI_c \approx 4.4\Phi_0/\mu m$

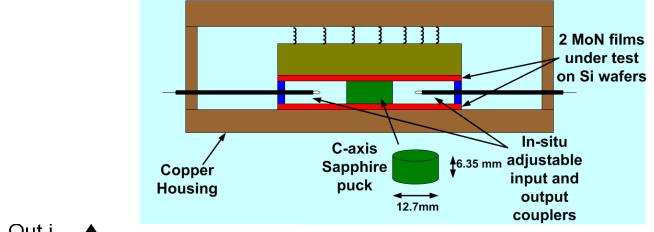

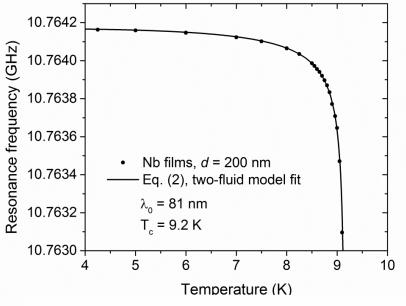

# London Penetration Depth and Kinetic Inductance of MoN<sub>x</sub> Films

#### **Measurement Techniques**

- Sapphire dielectric resonator technique

- $f_{\rm r} = 9.7 \, {\rm GHz}$

- Q > 30,000

$$f_r(T)/f_r(4.2K) = 1 - 2g \cdot [\lambda_{\text{eff}}(T) - \lambda_{\text{eff}}(4.2K)]$$

$$\lambda_{\rm eff} = \lambda \coth(d/\lambda)$$

$$\lambda(T) = \lambda_0/[1 - (T/T_c)^4]^{1/2}$$

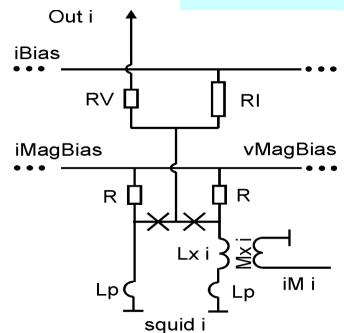

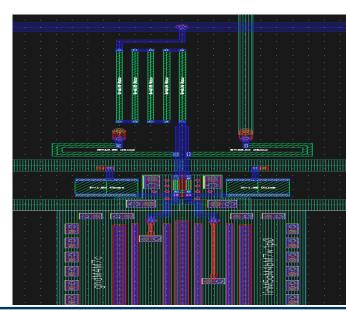

- dc-SQUIDs with patterned MoN<sub>x</sub> inductors

- Sheet inductance from the modulation period

- Inductor widths from 0.5 μm to 2 μm

- Inverted microstrip and unshielded strips

- Multiple SQUIDs per chip can be measured

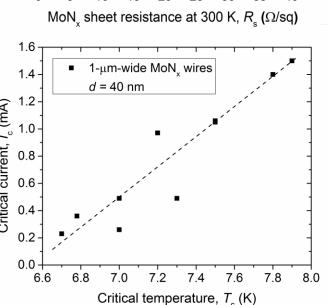

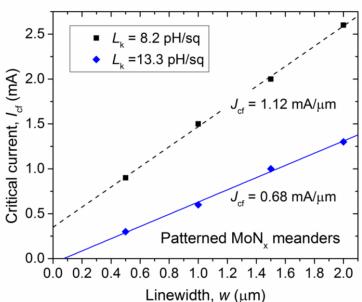

# Results on λ<sub>L</sub> and Kinetic Inductance of MoN<sub>x</sub> Films

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

• Critical current  $I_c \sim 1/L_k$  $I_{GL}L_k = \Phi_0 w/(3\sqrt{3}\xi)$

- In thin MoN<sub>0.33</sub> films,  $L_k I_c / w$ product is ≈ 9.1 pH·mA/μm or 4.4Φ<sub>0</sub>/μm

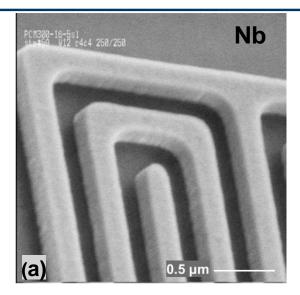

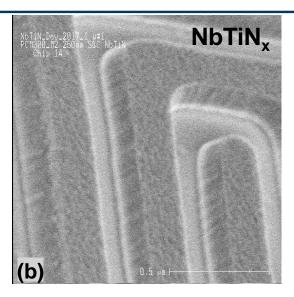

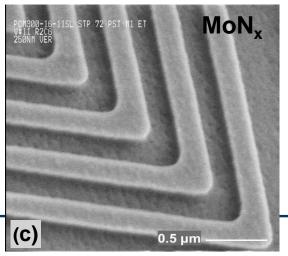

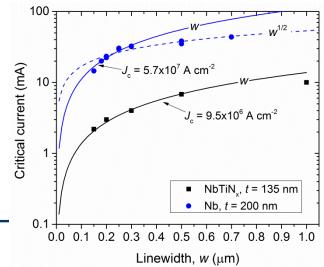

# 250-nm Nb and NbTiN Inductors and MoN<sub>x</sub> Resistors

- 250-nm Nb wiring

- On-wafer uniformity  $1\sigma = 3.9\%$

- Wafer-to-wafer variation  $1\sigma = 4.2\%$

- $I_c = 25 \text{ mA}$

- 250-nm NbTiN (reactive sputtering)

- $T_c = 14.5 \text{ K}$

- $I_c$  ≈ 3.5 mA (needs improvement)

- $J_c = 9.5 \times 10^6 \text{ A/cm}^2 (95 \text{ mA/}\mu\text{m}^2)$

- 250-nm Ti/MoN<sub>x</sub>/Ti resistors

- Thickness 40 nm for 6  $\Omega$ /sq

- On-wafer uniformity  $1\sigma = 2.7\%$

- Wafer-to-wafer variation  $1\sigma = 2.6\%$

- PEALD NbTiN for 250-nm via Damascene process

- $T_{c} = 9.7 \text{ K}$

- $J_c = 2 \times 10^5 \text{ A/cm}^2$  (needs improvement)

SEM images of the etched features with 250-nm width and 250-nm spacing. Note difference in surface roughness of NbTiN.

#### **Summary**

- We have made substantial progress breaking into VLSI and demonstrating SFQ circuits with ~ 1M JJs

- Superconductor electronics fabrication requires further innovations to grow the integration scale

- We have implemented high- $J_c$  self-shunted Nb/AlO<sub>x</sub>-Al/Nb junctions ( $J_c = 0.6$ -mA/ $\mu$ m<sup>2</sup>)

- We have developed and implemented in the fab processes

- Two layers of Josephson junctions

- 250-nm Nb wiring

- MoN<sub>x</sub> kinetic inductors

- 250-nm features Mo and MoN<sub>x</sub> resistors

- We continue working on

- Process with two JJ layers: different  $J_c$ s

- Investigation of Nb:Si barrier junctions

- Full integration of kinetic inductors into SFQ logic/memory cells

- CVD-filled interlayer vias

- Defect reduction and circuit yield improvements

# Thank you very much for your attention

**Questions?**

### **Process Cross Section (v. 1)**

1 layer of self-shunted JJs, six Nb layers, 1 layer of kinetic inductors, 1 layer of resistor (or bias inductors)

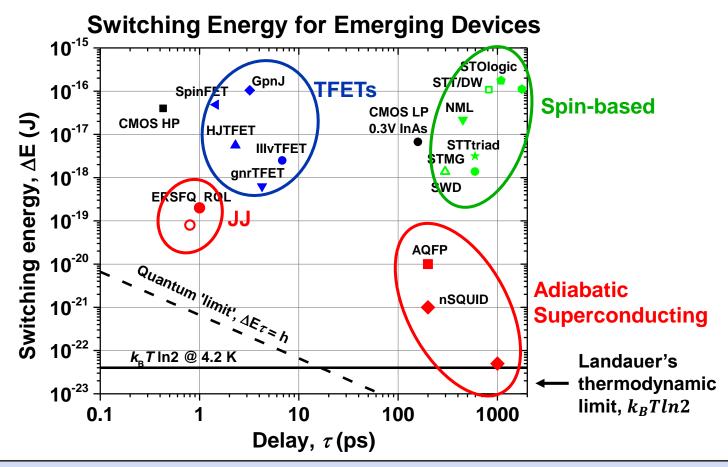

#### **Beyond CMOS Technologies**

Superconducting electronics based on Josephson junctions has demonstrated the lowest energy per operation (~ 10<sup>-22</sup> J), the highest clock speeds (up to 770 GHz), and is more mature than other beyond-CMOS technologies

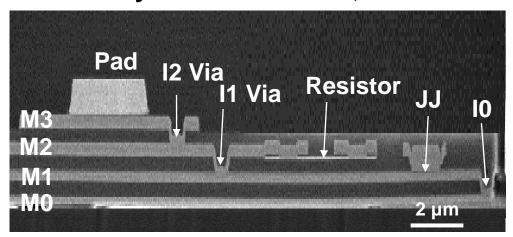

### MIT LL Superconducting Electronics Fabrication

#### 4-layer node SFQ3ee, 2012

Wafer size: 200 mm

Number of Nb layers: 4

Resistors: Pt, 2 Ω/sq, lift-off

Min JJ size: 700 nm

Min wiring size: 700 nm

Min spacing: 1000 nm

#### 8-layer node SFQ4ee, 2014

Wafer size: 200 mm

Number of Nb layers: 8

Resistors: Mo, 2 Ω/sq, etched

Min JJ size: 700 nm

Min wiring size: 500 nm

Min spacing: 700 nm