# **CRU Simulation and Verification**

Ola Grøttvik – August 23<sup>rd</sup>, 2017

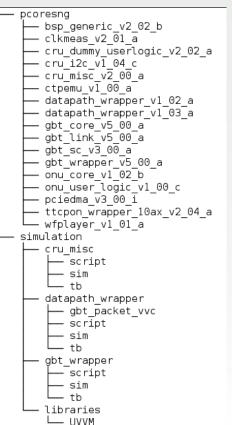

- Currently 3 simulation setups

- cru misc

- gbt\_wrapper

- datapath\_wrapper

- Usage of Bitvis UVVM for randomization and concurrency

- Especially useful for testing multiple interfaces at once

- Produces log with all necessary information

- Control of verbosity

- Current version reflects internal release v20170820 + bugfix

400

- Simulation folder must be placed with the core-folder to function

- All simulation runs are automated by tcl-scripts

- Howto for run is found in each simulations README.md

- Updating core versions must be reflected in common.ini which serves as the basis for all created prerequisites for the simulations

```

[structure]

cores_folder=pcoresng

[core_versions]

cru_misc=cru_misc_v2_00_a

clkmeas=clkmeas_v2_01_a

datapath_wrapper=datapath_wrapper_v1_03_a

gbt_core=gbt_core_v5_00_a

gbt_link=gbt_link_v5_00_a

gbt_sc=gbt_sc_v3_00_a

gbt_wrapper=gbt_wrapper_v5_00_a

```

- cru\_misc

- Targets the Avalon IC Module

- Multiple Avalon VVC for concurrency

- Multiple levels of ICs and slaves

- Default checks. Read/write access.

- Randomization of data

- Randomization of timing

### cru\_misc from README.md

\$ cd ./sim

\$ vsim -do ../script/compile\_all\_and\_sim\_cru\_misc\_tb.do

### Example log message

```

ID_BFM 125447.5 ns AVALON_MM_VVC,0 avalon_mm_check_response(A:x"9005000E",x"7A6CA16A")=>

OK, received data = x"7A6CA16A". 'Check reg'

```

- gbt\_wrapper

- Targets the gbt\_wrapper module

- Register read/write via Avalon VVC

- Check GBT data transmission

- GBT frame

- Wide frame

- Raw

- Currently only one link, but will be upgraded

## gbt\_wrapper from README.md

- \$ cd ./sim

- \$ quartus\_sh -t ../script/generate\_ips.tcl

- \$ vsim -do ../script/compile\_all\_and\_sim\_gbt\_wrapper\_tb.do

- datapath\_wrapper

- Check packetized GBT data transmissions to the datapath\_wrapper

- Register read/write via Avalon VVC

- Multiple concurrent links via GBT Packet VVCs

- Randomized packet length, data, idle words

- Check for link ID, packet length, packet drops, etc

## datapath\_wrapper from README.md

- \$ cd ./sim

- \$ quartus\_sh -t ../script/generate\_ips.tcl

- \$ vsim -do ../script/compile\_all\_and\_sim\_tb.do

- Status: Work in progress

- Currently in private gitlab repository

- https://gitlab.cern.ch/ogrottvi/cru\_simulation

- Request access: ola.slettevoll.grottvik@cern.ch