# APV25 VME based readout system for a Jlab GEM tracker

Paolo Musico

INFN Genova

- The Detector

- Front End Electronics

- \* Read Out Electronics

### The Detector (1)

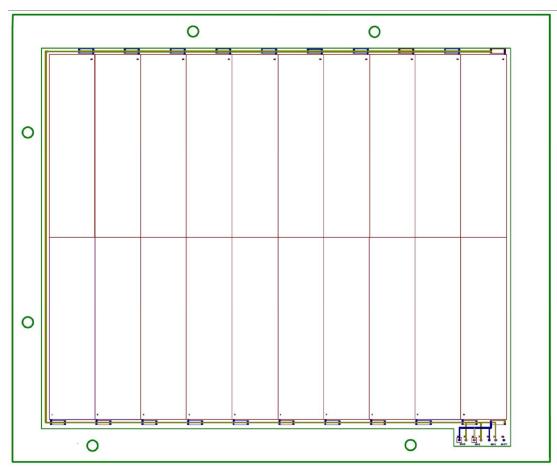

Jefferson LAB upgrade to 12 GeV framework program.

HALL-A SBS front tracker GEM based

6 planes X-Y (+ U-V?)

Area:  $\approx 40 \times 50 \text{ cm}^2$

Gem foils divided in 20 sectors  $20 \times 5 \text{ cm}^2$

Each sector connected to HV through a SMD resistor placed along the frame (long sides).

Design and production by Rui De Oliveira.

### The Detector (2)

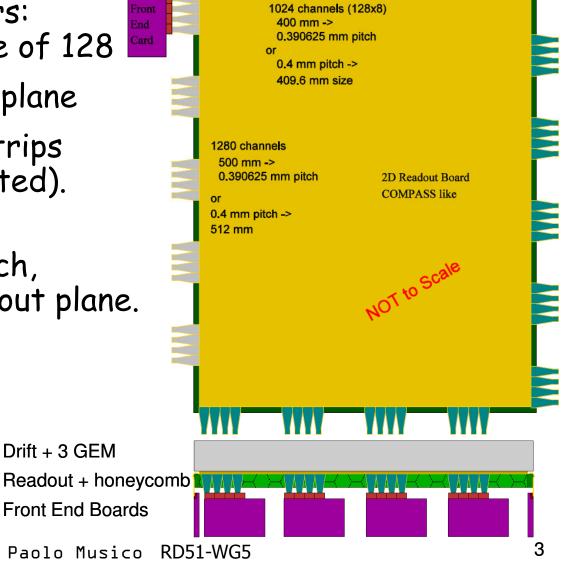

2D readout strips layers: pitch = 0.4 mm, multiple of 128

1024 + 1280 strips per plane

In total about 14000 strips (x 2 if U-V option adopted).

Use of Panasonic FPC connectors, 0.3 mm pitch, avoid soldering on readout plane.

Readout on both sides, interleaved.

Drift + 3 GEM

### Front End (1)

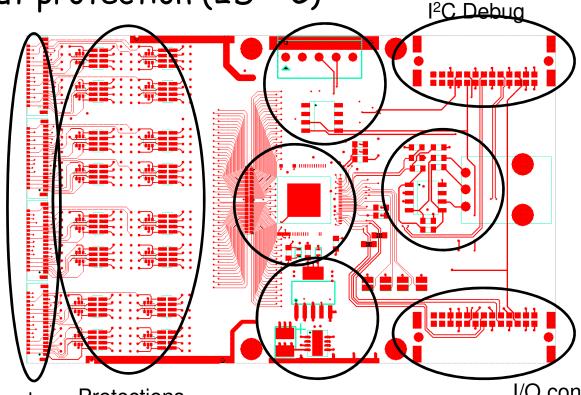

Based on APV25 chip. We bought ≈ 600 naked chips.

128 channels per card (1 APV). Dimensions:  $50 \times 80 \text{ mm}^2$

Discrete input protection (2D + C)

Panasonic FPC connectors Protections

APV25 PSL I/O connectors

Analog output buffer

### Front End (2)

Design finished.

Some issues regarding output analog signal transmission and radiation tolerance (quite hot zone). Testing needed.

PCB ready for production: we are waiting quotations.

Double check with GEM readout plane needed.

SMD assembly using external fab.

APV wire bonding using internal facility (ATLAS pixel modules).

Standard assembly (through hole) in house, after wire bonding.

First prototype ready in 2 months (hope earlier!).

### Readout (1)

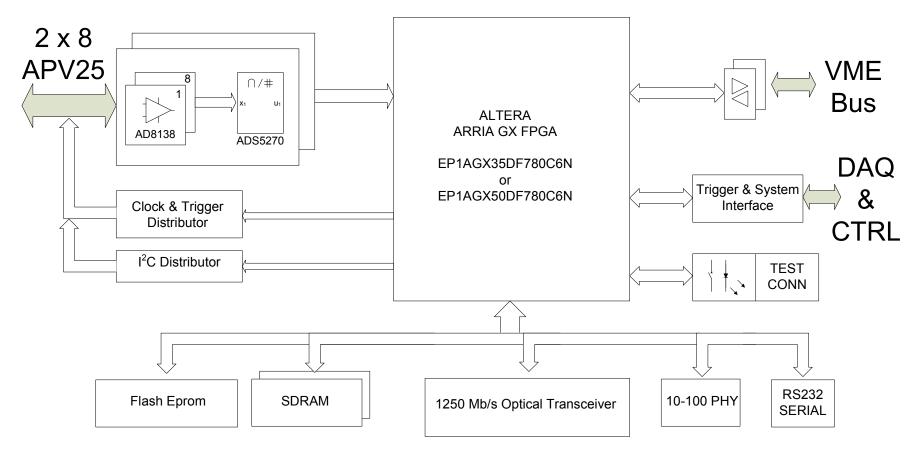

#### Main features:

- Digitization of 16 APVs (2048 channels)

- APV serial stream decoding

- Zero suppression

- o Big memory buffer, multi event

- Possibility to implement SOC:

- Flash, Ethernet, Serial

- Remote logic reconfiguration, hot swappable

- o Dual configuration:

- goal: VME64x compliant

- backup: Stand Alone (with optical link)

## Readout (2)

Power Supply

Clock Generator

Live Insertion & Remote Configuration

### Readout (3)

#### Status:

- Almost all components chosen

- FPGA: Altera Arria GX

- ADC: Texas ADS5270

- Schematic drawing almost done

- Some details still missing (i.e. trigger & DAQ if)

- PCB design will start very soon

- Footprint checking in progress

- Quotation for manufacturing already asked

- > Ready for production in 2 months

### **Conclusions**

The design of the system is in advanced phase.

Front end prototypes testing will teach a lot regarding output analog signal integrity and radiation tolerance.

A big effort is needed to develop the FPGA code:

- APV deserialization and decoding

- VME interface

- □ I<sup>2</sup>C controller

- Trigger handling

- High speed serial interface (optical)