# Signal levels and bus standards past, present and future

#### Zhen-An LIU TrigLab/IHEP Beijing, China

IEEE NPSS International School for Real Time Systems in Particle Physics 2018

7-17 July 2018 iThemba, Cape Town, SA

### Outline

- Overview in a physics experiment

- Standardization is a must

- Standard in signal levels

- Only those in instrumentation(not those in FPGA)

- BUS Standards in instrumentation

- NIM,CAMAC,VME

- New standard

- xTCA for Physics, AMC, ATCA, MTCA

- Some examples

- Summary

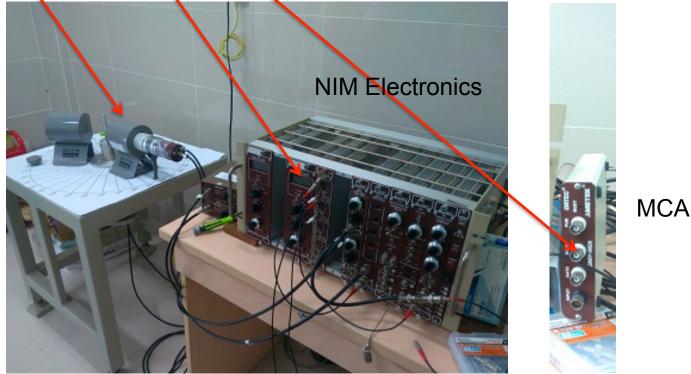

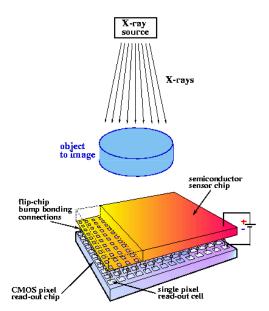

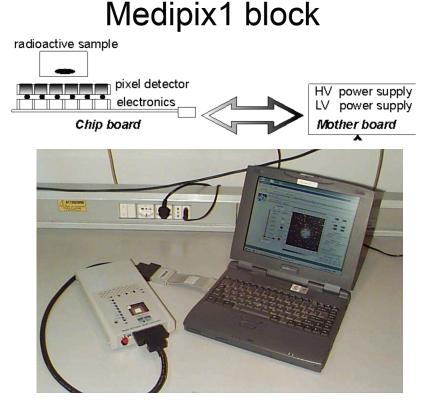

### Instrumentation

- Detector: for signal detection

- Electronics: signal processing

- Processor: data processing and display

Compton Scattering Setup in NTLab VNU-HCMUS, School on RT System 2016

Jul 7-17 2018,iThemba

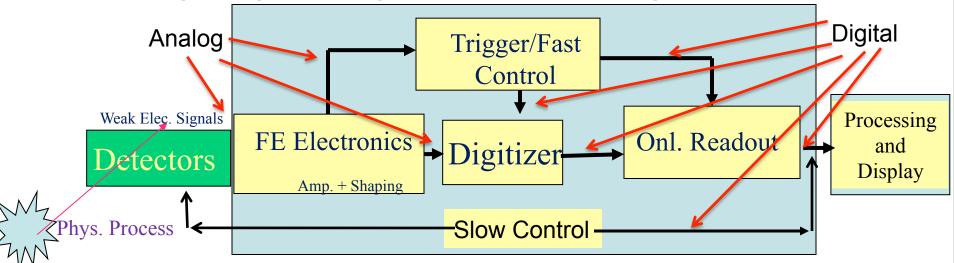

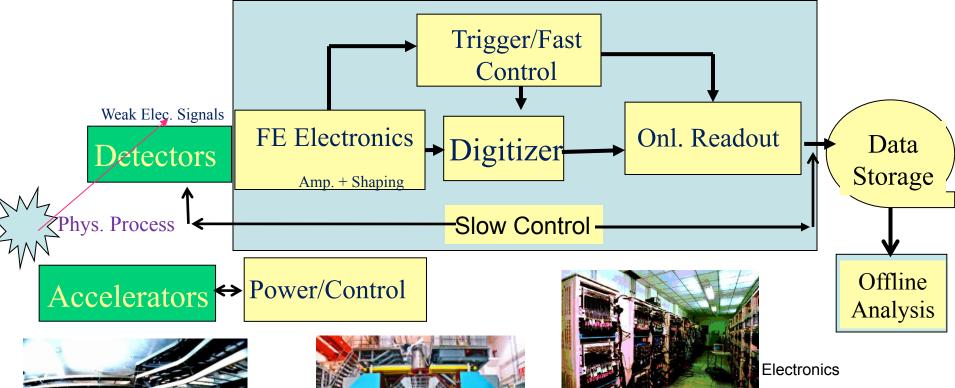

### **Signal Processing and Control**

Analog/Digital signal processing

- Pre-Amplifier: amplify weak signal

- Main Amplifier: amplify small signal

- Digitizer: convert analog to digital

- Readout: collect data

- Processor: data analysis and display

Digital signal standardization

### Trend direction 1: Instrumentations minimization: Lower signal level and Faster data link

• Full system into small box

PMT(left),TOF( middle, right) exercise setup for RT School 2016Jul 7-17 2018,iThembaZ.A.LIU Intl. School on RT System 2018

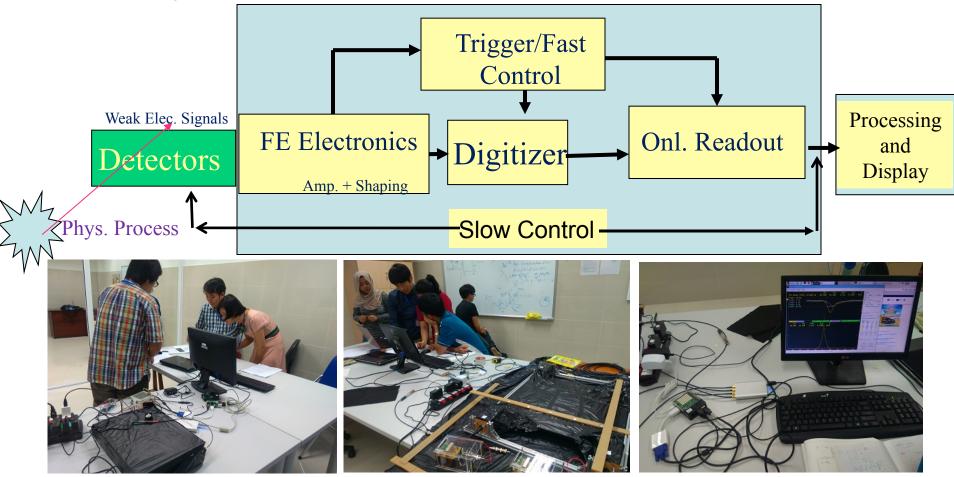

### Question

- What can be used as Digitizer?

- Why you can borrow a USB line to connect your Mobile Phone to your notebook?

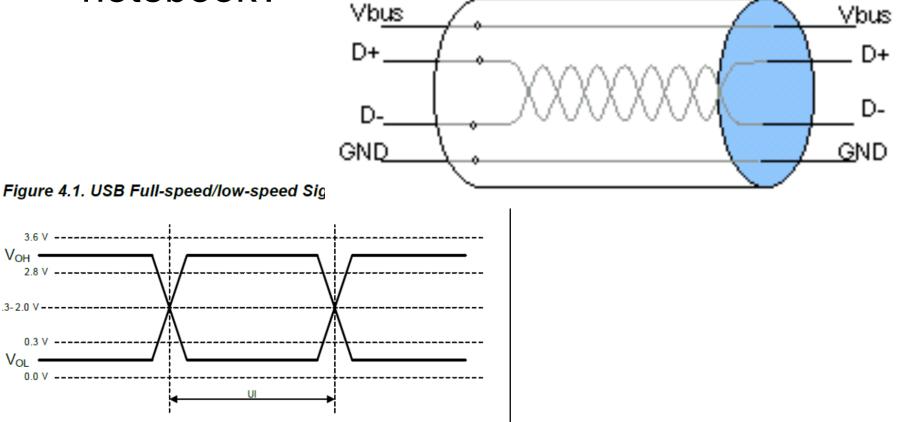

### **USB** standard

Why you can borrow a USB line to connect your Mobile Phone to your notebook?

Trend direction 1: Compact Instrumentations: Lower signal level and Faster data link

- Or even handy meters

- ASICs: Application Specific Integrate Circuits

- FPGA: Field Programmable Gate Array

- System on Chip

- Experiment on Chip

Jul 7-17 2018,iThemba

# Trend direction 2: Experiment needs Instrumentations for Signal Processing and Control in Larger scale

Huge amount of different instruments

Accelerators

Jul 7-17 2018,iThemba

Detectors

•Control and Data Readout •Standardized Signal levels •Standardized Crates •Standardized Modules

### Questions

- In digital world, what is the logic 1? And Logic 0?

- What are the names representing different digital levels? Their voltages of level 1? And level 0?

- You know USB line already, what else?

Mini-USB, Micro-USB

- Boundary Scan/JTAG

. . . . . .

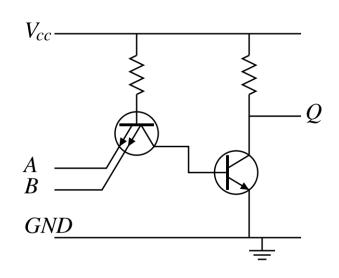

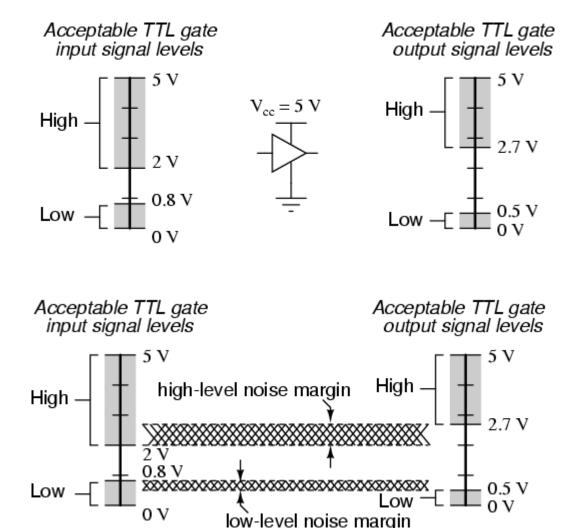

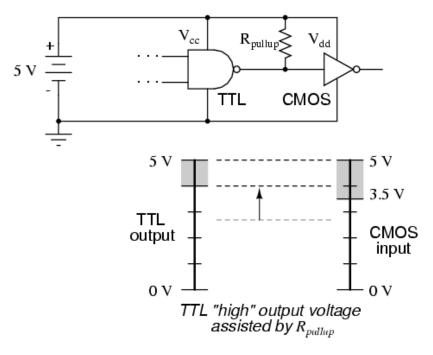

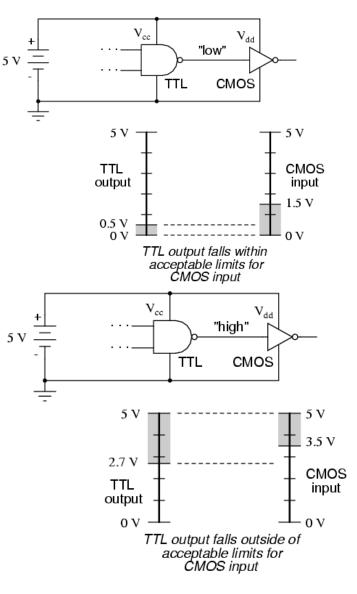

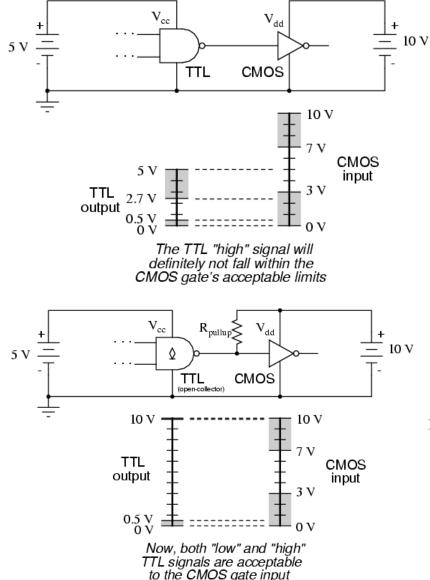

## TTL Logic

- TTL: Transistor-Transistor Logic

- invented in 1961 by James L. Buie of <u>TRW</u>

Company

- Logic 1(high): >2V

- Logic 0(low): < 0.8V</p>

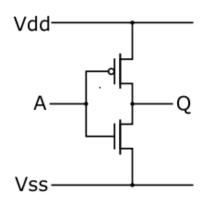

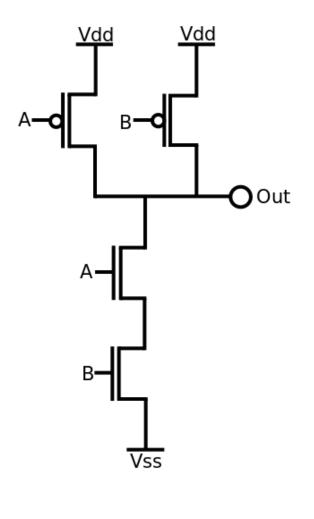

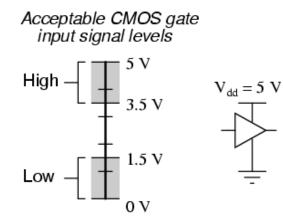

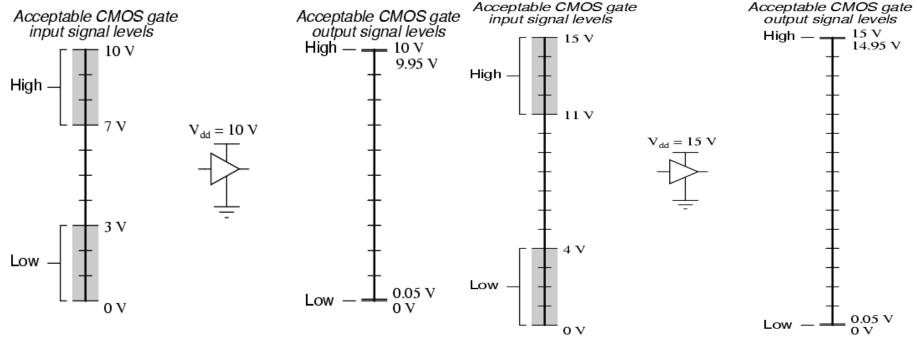

### CMOS Logic

- CMOS (Complementary metal –oxide–semiconductor) is a technology for constructing integrated circuits.

- Frank Wanlass patented CMOS in 1963

- high noise immunity and low static power consumption

- V<sub>DD</sub> = supply voltage

- VSS=Ground

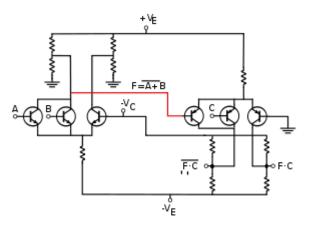

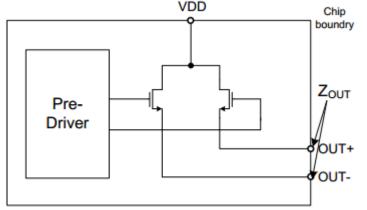

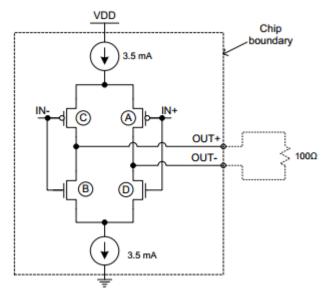

### ECL/PECL/LVPECL Logic

- ECL (emitter-coupled logic) is a high-speed integrated circuit bipolar transistor logic family

- ECL was invented in August 1956 at IBM by Hannon S. Yourke

- PECL: Positive powered.

- LVPECL: 3.3V PECL

| Differential-amplifier<br>input and logic section | Internal temperature and<br>voltage compensated<br>bias network section<br>(one supplies several<br>differential amplifiers) | Emitter-follower<br>output section                   |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 220 245                                           | V <sub>CC2</sub> 0 V<br>907 ≹                                                                                                |                                                      |

|                                                   | 04<br>-1.29 V<br>at 25°C<br>6.1 k 4.98                                                                                       | (A+B)<br>~(A+B)<br>MECL 10K series<br>2-input OR/NOR |

| Туре   | V <sub>ee</sub> | V <sub>low</sub> | $V_{high}$ | V <sub>cc</sub> | V <sub>cm</sub> |

|--------|-----------------|------------------|------------|-----------------|-----------------|

| PECL   | GND             | 3.4 V            | 4.2 V      | 5.0 V           |                 |

| LVPECL | GND             | 1.6 V            | 2.4 V      | 3.3 V           | 2.0 V           |

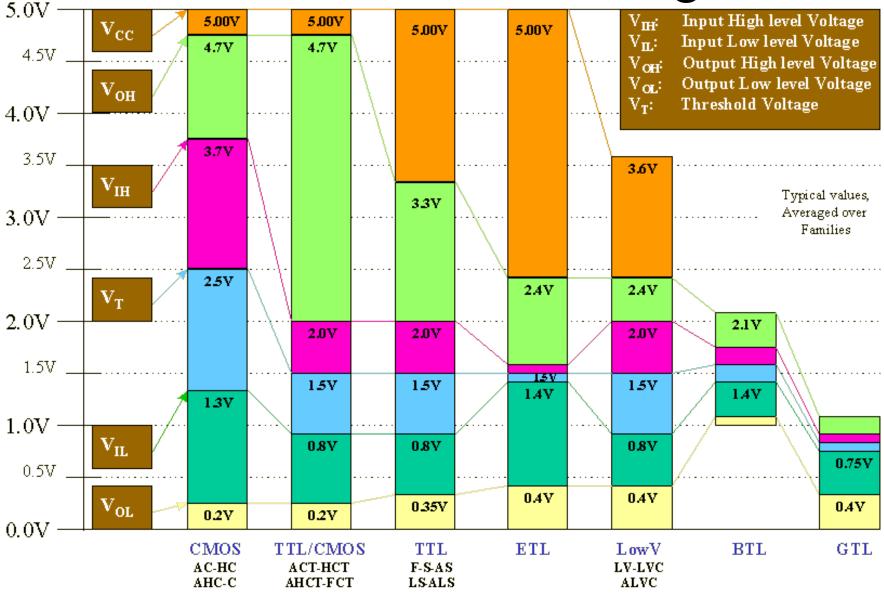

### Examples of binary logic levels

| Technology  | L voltage                   | H voltage                | Notes                                                                       |

|-------------|-----------------------------|--------------------------|-----------------------------------------------------------------------------|

| <u>CMOS</u> | 0 V to V <sub>DD</sub> /2-a | $V_{DD}/2+a$ to $V_{DD}$ | V <sub>DD</sub> = <u>supply voltage</u> ,<br>a=1,2,3.5V for<br>VDD=5,10,15V |

| TTL         | 0 V to 0.8 V                | 2 V to $V_{cc}$          | V <sub>CC</sub> is 4.75 V to<br>5.25 V                                      |

| <u>ECL</u>  | -1.175 V to $V_{EE}$        | 0.75 V to 0 V            | $V_{EE}$ is about -5.2 V. $V_{CC}$ =Ground                                  |

| NIM         | -0.8V                       | 0V                       | $V_{EE}$ is about -5.2 V. $V_{CC}$ =Ground                                  |

NIM logic: levels are defined by current ranges on 50 ohm input/out impedances, correspond to voltages of 0 V and -0.8 V for logic 0 and 1 respectively

Jul 7-17 2018,iThemba

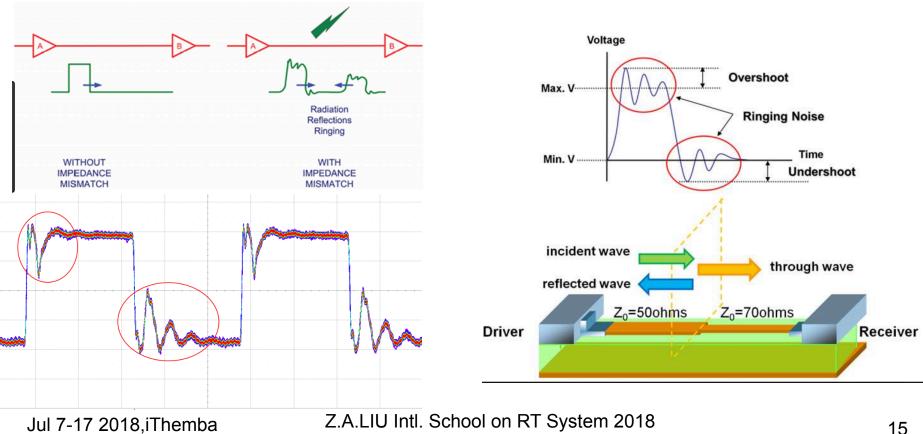

### Signal Integration

- Termination

- Twix Pair lines

- Shielding

### What standard means

- Forbidden Range

- Range different for input and output for noise tolerance

- Limited noise margin

### What standard means(2)

- Good noise margin

- High power comsumption

Jul 7-17 2018,iThemba

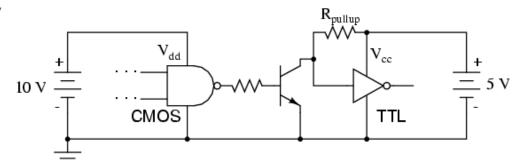

### What standard means(3)

- No direct connection btw devices of different standards

- Level shifting necessary

- By circuit between, or

- By commercial device

Jul 7-17 2018,iThemba

### What standard means(4)

Jul 7-17 2018, iThemba

- In 10V CMOS case

- No direct inter-usage

- Level shifting necessary

### Some of the level ranges

Jul 7-17 2018, iThemba

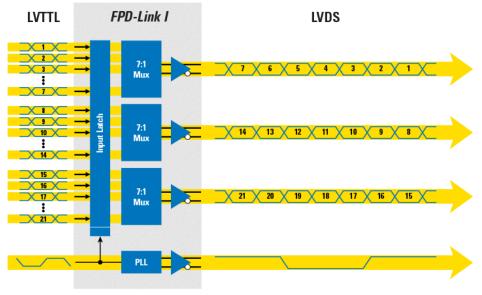

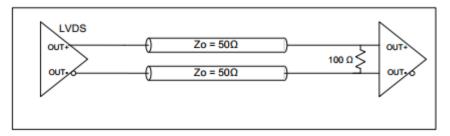

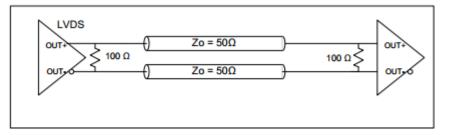

# LVDS

- LVDS(Low-voltage differential signaling)/ TIA /EIA-644, a technical standard that specifies electrical characteristics of a differential, serial communication protocol

- low power, very high speeds with inexpensive twisted-pair copper cables

- was introduced in 1994

- Point to point

| V <sub>ee</sub> | V <sub>OL</sub> | V <sub>OH</sub> | V <sub>cc</sub> | V <sub>CMO</sub> |

|-----------------|-----------------|-----------------|-----------------|------------------|

| GND             | 1.0 V           | 1.4 V           | 2.5–<br>3.3 V   | 1.2 V            |

Jul 7-17 2018,iThemba

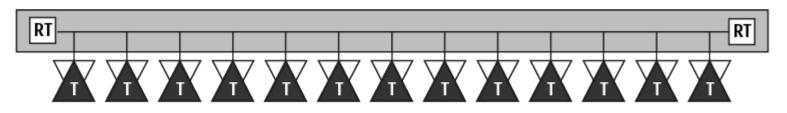

### Multipoint LVDS/MLVDS/BLVDS

- Bus LVDS and LVDM (by TI) are <u>de facto</u> multipoint LVDS standards

- Multipoint LVDS (MLVDS) is the <u>TIA</u> standard (TIA-899). The <u>AdvancedTCA</u> standard specified MLVDS for clock distribution across the backplane to each of the computing module boards in the system

Note - the receivers shown must not have internal terminations.

|      | Ou          | Input                 |        |  |

|------|-------------|-----------------------|--------|--|

|      | Common mode | Common mode Amplitude |        |  |

| Min. | 0.3 V       | 0.480 V               | -1.4 V |  |

| Max. | 2.1 V       | 0.650 V               | 3.8 V  |  |

Jul 7-17 2018, iThemba

### Termination, Reflection, Signal Integration

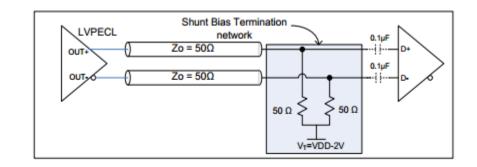

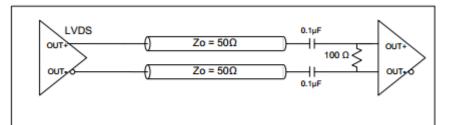

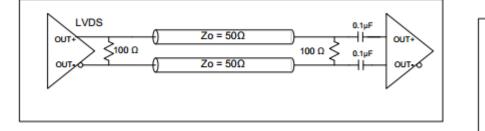

### Coupling

- DC coupled in low speed

- AC coupled in high speed

- ECL/LVPECL

Jul 7-17 2018,iThemba

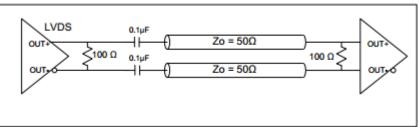

### **Termination 2**

• LVDS

Jul 7-17 2018,iThemba

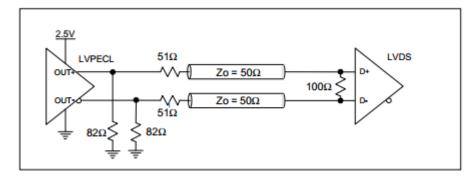

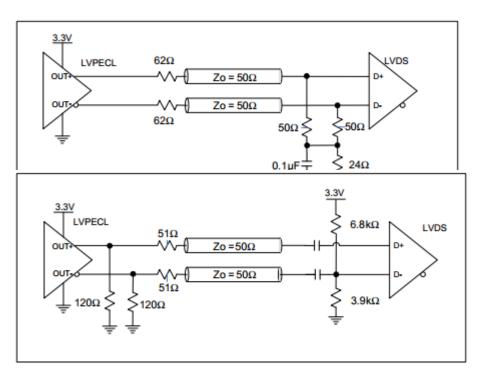

### LVPECL-LVDS Level shift

Jul 7-17 2018,iThemba

Z.A.LIU Intl. School on RT System 2018

25

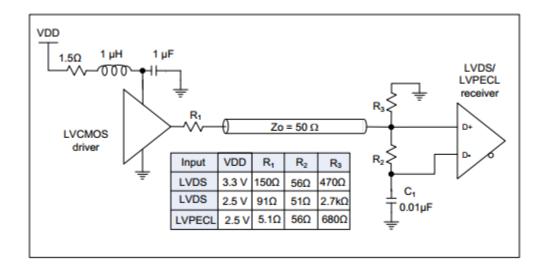

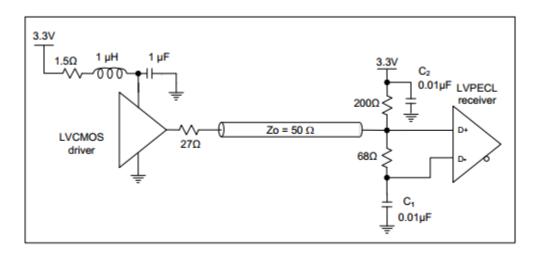

### LVCMOS-LVPECL/LVDS Level shift

Jul 7-17 2018,iThemba

### **BUS Standards for Nuclear Instrumentation**

- 1960's

- Nuclear Electronics Standard in British Rutherford Lab

- Same time also in CERN and American Labs

- NIM: American Standard Beurea and NIM Module Committee

- 70-80's CAMAC, FASTBUS, widely used

- Nuclear Spectrum Measurement, Particle Physics, Medical Physics, Accelerator Instrument, Accelerator Control, Aerospace, Industrial control.

- 90's VME from Industry

- 2000 CPCI

#### Still in use, BUT limited

Jul 7-17 2018,iThemba

# NIM

- **NIM**(Nuclear Instrumentation Module ) standard defines

- mechanical and electrical specifications

- for electronics modules

- used in experimental particle and nuclear physics

- Crate

- Power: ± 6/±12/±24V DC from 220/110V

- No data BUS

- 12 Modules

NIM standard module connector pin assignments (required by DOE/ER-0457T)

| Pin # | Function           | Pin # | Function            |

|-------|--------------------|-------|---------------------|

| 1     | Reserved [+3 V]    | 2     | Reserved [-3 V]     |

| 3     | Spare Bus          | 4     | Reserved Bus        |

| 5     | Coaxial            | 6     | Coaxial             |

| 7     | Coaxial            | 8     | 200 V DC            |

| 9     | Spare              | 10    | +6 V                |

| 11    | -6 V               | 12    | Reserved Bus        |

| 13    | Spare              | 14    | Spare               |

| 15    | Reserved           | 16    | +12 V               |

| 17    | -12 V              | 18    | Spare Bus           |

| 19    | Reserved Bus       | 20    | Spare               |

| 21    | Spare              | 22    | Reserved            |

| 23    | Reserved           | 24    | Reserved            |

| 25    | Reserved           | 26    | Spare               |

| 27    | Spare              | 28    | +24 V               |

| 29    | -24 V              | 30    | Spare Bus           |

| 31    | Spare              | 32    | Spare               |

| 33    | 117 V AC (hot)     | 34    | Power Return<br>Gnd |

| 35    | Reset (scaler)     | 36    | Gate                |

| 37    | Reset (aux)        | 38    | Coaxial             |

| 39    | Coaxial            | 40    | Coaxial             |

| 41    | 117 V AC (neutral) | 42    | High Quality Gnd    |

| G     | Gnd Guide Pin      |       |                     |

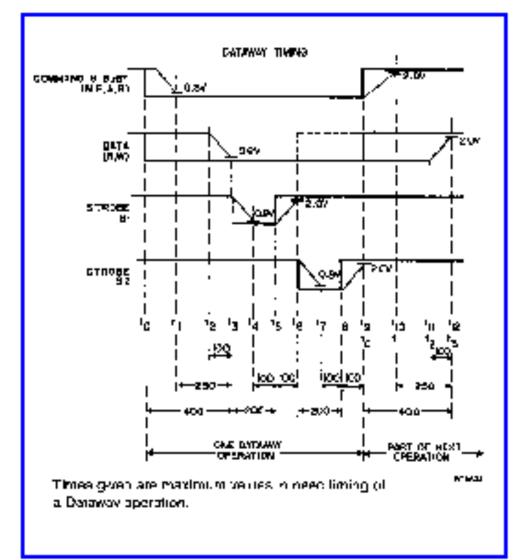

### CAMAC

CAMAC: Computer Automated Measurement And Control

| MAXIMUM CURRENT LOADS                      |                                  |                                     |                            |  |  |  |  |

|--------------------------------------------|----------------------------------|-------------------------------------|----------------------------|--|--|--|--|

| SUPPLY<br>Voltage                          | VOLTAGE<br>Tolerance             | IN THE PLUG-IN<br>(PER UNIT WIDTH)* | IN THE CRATE **            |  |  |  |  |

| Mandatory                                  |                                  |                                     |                            |  |  |  |  |

| +24 V DC<br>+6 V DC<br>-6 V DC<br>-24 V DC | ±0.5%<br>±2.5%<br>±2.5%<br>±0.5% | 1 A<br>2 A<br>2 A<br>1 A            | 6 A<br>25 A<br>25 A<br>6 A |  |  |  |  |

| Additional (                               | as required)                     |                                     |                            |  |  |  |  |

| +12 V DC<br>-12 V DC                       | ±0.5%<br>±0.5%                   |                                     |                            |  |  |  |  |

| " See Notes Fand 3.<br>"" See Note 2.      |                                  |                                     |                            |  |  |  |  |

Table 2

- ESONE Committee: standard EUR 4100 in 1972

- Crate:

- Data bus:24b

- Power

- Control

- 24+1 station

- Controller on 25th

Jul 7-17 2018,iThemba

Z.A.LIU Intl. School on RT System 2018

WRITE LINES

V

TIMING STRODES

2,1,0

B

F,A

COMMON CONTROLS

0

OMMAND LINES

0

NORMAL STATION 1

NORMAL STATION 2

NORMAL STATION 1

NORMAL STATION 2

R

Q,X

R

### Pin assignments

- Data Way(W24,R24)

- Interrupt:L24

- Station:N24+1

- FA:5+4

- Power:6

- Control:S1S2 ZICB QX

| TITLE               | DESIGNATION | COL-<br>TACTS | USE AT A MODULE                                                        | TITLE                | DESIGNATION | COL-<br>LACTS | USE AT A MODULE                                               |

|---------------------|-------------|---------------|------------------------------------------------------------------------|----------------------|-------------|---------------|---------------------------------------------------------------|

| Command             |             |               |                                                                        |                      |             |               |                                                               |

| Station Numl        | ber N       | 1             | Selects the module (individual<br>line from control station).          | Common Contro        | bis         |               | Operate on all stations conne<br>to them , no command require |

| Sub-Address         | ×1,2,4,8    | 4             | Selects a section of the module.                                       | Initalize            | z           | 1             | Sets module to a defined stat<br>(accompanied by S2 and B).   |

| Function            | F1,2,4,8,16 | 5             | Defines the function to be perform ed in the module.                   | Inhibit              | I           | ł             | Disables teatures for duration<br>of signal.                  |

| Timing              |             |               |                                                                        | Clear                | с           | ł             | Clears registers (accompanie<br>by 52 and B).                 |

| Strobe I            | 51          | 1             | Controls first phase of operation.<br>(Dataway signals may change.)    |                      |             |               | -,,                                                           |

|                     |             |               | •                                                                      | Non-Standard C       | onnectors   |               |                                                               |

| Strobe 2            | 52          | 1             | Controls second phase.<br>(Dataway signals may change.)                | Free bus-lines       | P1, P2      | 2             | For specified uses .                                          |

| Cata                |             |               |                                                                        | Patch Contact        | s P3-P5     | 3             | For unspecified interconnection No Dataway lines .            |

|                     |             |               |                                                                        |                      |             |               | r                                                             |

| Write               | W1-W24      | 24            | Bring information to them odule.                                       |                      |             |               |                                                               |

| Read                | R1-R24      | 24            | Take information from the                                              | Mandatory Pow        | er Lines    |               |                                                               |

| news                | 111121      |               | module.                                                                | +24 V DC             | +24         | 1             |                                                               |

|                     |             |               |                                                                        | +6 V DC              | +6          | 1             |                                                               |

|                     |             |               |                                                                        | -6 V DC              | -6          | 1             |                                                               |

| Status              |             |               |                                                                        | -24 VDC<br>0 V       | -24         | 2             | Power return.                                                 |

| Look-a‡Me           | L           | ł             | indicates request for service<br>(individual line to control station). | 04                   | 0           | 2             | Powerre un.                                                   |

|                     |             |               | (nanasinic evana sarah).                                               | Additional Powe      | rtines      |               |                                                               |

| Busy                | в           | 1             | Indicates that a Dataway                                               |                      |             |               |                                                               |

|                     |             |               | operation is in progress.                                              | UON DO               |             |               | Lines are reserved for the<br>this work of personal sectors   |

|                     |             |               | -                                                                      | +12 V DC<br>-12 V DC | +12<br>- 12 | 1             | toilowing power supplies.<br>Low current for indicators, ef   |

| Response            | a           | 1             | Indicates status of feature<br>selected by command.                    | Clean Earth          | E           | ł             | Reference for circuits requirir<br>clean earth.               |

|                     |             |               |                                                                        | Reserved YH, Y2      | 2 2         |               | Reserved for future allocation                                |

| Command<br>Accepted | х           | 1             | Indicates that module is able to<br>perform action required by the     | 1999 1999 11, 18     |             |               |                                                               |

command.

CTANDADD DATAWAY IN AOD

Jul 7-17 2018, iThemba

### Pin assignment

#### P N ALLOCATION AT NORMAL STATION (view from front of case)

#### (STATIONS 1-21)

| Bus line         | Free Bus line                     | P1         | в       | Вьсу        | Bus line          |

|------------------|-----------------------------------|------------|---------|-------------|-------------------|

| Bus line         | Free Bus line                     | P2         | F16     | Function    | Bus line          |

| Individual pat   | ch contact                        | P3         | F8      | Function    | Bus line          |

| Individual pat   | ch contact                        | м          | F4      | Function    | Bus line          |

| Individual pat   | ch contact                        | P5 -       | F2      | Function    | Bus line          |

| Bus line         | Command Accepted                  | х          | Fi      | Function    | Bus line          |

| Bus line         | Inhibit                           | I -        | A8      | Subaddress  | Bus line          |

| Bus line         | Clear                             | с          | A4      | Subaddress  | Bus line          |

| Individual line  | Station Number                    | N          | A2 -    | Subaddress  | Bus line          |

| Individual line  | Look-at-Me                        | L          | A4 -    | Subaddress  | Bus line          |

| Bus line         | Strobe 1                          | 51         | z       | hitaize     | Bus line          |

| Bus line         | Strobe 2                          | 52         | a       | Response    | Bus line          |

|                  |                                   | W24        | W23     |             |                   |

|                  |                                   | W22        | W21     |             |                   |

|                  |                                   | W20        | W19     |             |                   |

|                  |                                   | W18        | W17     |             |                   |

| 24 Write Bus     | Lines                             | W16        | Wis     |             |                   |

| W1=LSB           |                                   | W14        | W13     |             |                   |

| W24 <b>≓M5</b> 8 |                                   | W12        | WH      |             |                   |

|                  |                                   | W10        | W9      |             |                   |

|                  |                                   | <b>W</b> 8 | W7      |             |                   |

|                  |                                   | W6         | WS.     |             |                   |

|                  |                                   | W4         | W3      |             |                   |

|                  |                                   | W2         | W1      |             |                   |

|                  |                                   | R24        | R23     |             |                   |

|                  |                                   | R22        | R21     |             |                   |

|                  |                                   | R20        | R 19    |             |                   |

|                  |                                   | R 18       | B17     |             |                   |

| 24 Read Bus      | Lines                             | R 16       | R 15    |             |                   |

| R1=L58           |                                   | R 14       | R13     |             |                   |

| R24 <b>≓M</b> 5B |                                   | R12        | R11     |             |                   |

|                  |                                   | R 10       | R9      |             |                   |

|                  |                                   | R8         | 87      |             |                   |

|                  |                                   | R6         | RS      |             |                   |

|                  |                                   | R4         | R3      |             |                   |

|                  |                                   | R2         | R1      |             |                   |

|                  | -12 V DC                          | -12        | -24     | -24 V DC    |                   |

|                  |                                   | NC         | -6      | -6VDC       |                   |

|                  |                                   | NC         | NC      | 0,400       |                   |

| Power            | Auxiliary-6 V supply              |            | E       | Clean Earth | Power             |

| Bus lines        | -12 VDC                           | +12        | -       | 424 VDC     | roma<br>Bus lines |

|                  | - 12 VLC<br>Auxiliary +6 V supply |            |         | +6VDC       | ous nines         |

|                  | OV/Power Return)                  | 12<br>0    | +0<br>0 | OV/Power R  | ot mo             |

|                  | ov(roma kadinj                    | 0          | 0       | ov (romer k | e on ij           |

Normal Module station

| PIN ALLOCATION<br>AT CONTROL STATION |                        |            |            |                   |           |

|--------------------------------------|------------------------|------------|------------|-------------------|-----------|

|                                      | (5)                    | IA TIOI    | 3          |                   |           |

| Individual                           | patch contact          | М          | в          | Вьсу              | Bus line  |

| Individual                           | patch contact          | P2         | F16        | Function          | Bus line  |

| Individual                           | patch contact          | P3         | F8         | Function          | Bus line  |

| Individual                           | patch contact          | м          | F4         | Function          | Bus line  |

| Individual                           | patch contact          | PS         | F2         | Function          | Bus line  |

| Bus line                             | Command Accepted       | х          | F1         | Function          | Bus line  |

| Bus line                             | Inhibit                | I.         | <b>A</b> 8 | Subaddress        |           |

| Bus line                             | Clear                  | С          | M          | Subaddress        | Bus line  |

| Individual                           | patch contact          | P6         | A2         | Subaddress        | Bus line  |

|                                      | patch contact          | P7         | A1         | Subaddress        |           |

|                                      | Strobe 1               | 51         | z          | hitaize           | Bus line  |

| Bus line                             | Strobe 2               | <b>5</b> 2 | a          | Response          | Bus line  |

|                                      |                        | L24        |            |                   |           |

|                                      |                        | L23        |            |                   |           |

|                                      |                        | L22        |            |                   |           |

|                                      |                        | L21        |            |                   |           |

|                                      |                        | L20        |            |                   |           |

|                                      |                        | L 19       |            |                   |           |

|                                      |                        | L 18       |            |                   |           |

|                                      |                        | L 17       |            |                   |           |

|                                      |                        | L 16       |            |                   |           |

|                                      |                        | L 15       |            |                   |           |

|                                      |                        | L 14       |            |                   |           |

|                                      |                        | L 13       |            |                   |           |

|                                      | ual Look-at-Me Lines   | L 12       |            |                   |           |

| Lintom S                             | tation 1, etc.         | L11        |            |                   |           |

|                                      |                        | L 10       |            | N1 to Station     | il,etc.   |

|                                      |                        | L9         | N9         |                   |           |

|                                      |                        | L8         | N8         |                   |           |

|                                      |                        | 17         | N7         |                   |           |

|                                      |                        | L6         | N6         |                   |           |

|                                      |                        | LS         | NS         |                   |           |

|                                      |                        | L4         | N4         |                   |           |

|                                      |                        | L3<br>L2   | N3<br>N2   |                   |           |

|                                      |                        | 12         | N2<br>N1   |                   |           |

|                                      | - 12 V DC              | -12        | N1<br>-24  | -24 V DC          |           |

|                                      | -12 V DC               | -12<br>NC  | -24<br>-6  | -24 VDC<br>-6 VDC |           |

|                                      |                        | NC         | NC         | -0.400            |           |

| Power                                | Auxiliary - 6 V supply | YE         |            | Clean Earth       | Power     |

|                                      | -12 V DC               |            | +24        | 424 VIDC          | Bus line  |

| 200 10 10                            | Auxiliary +6 V supply  | Y2         | тел<br>+6  | +6 V DC           | 2-22 m PC |

|                                      | OV(Power Return)       | 0          | 0          | OV/Power R        | et mó     |

|                                      | (rona nearly           | •          | -          |                   |           |

|                                      |                        |            |            |                   |           |

#### Z.A.LIU Intl. School on RT System 2018

Control

Module

station

Table 3a

### Timing and data rate

- Data Cycle: 1us

- Data width

:24b=3B

- Rate:24bps=3Bps

### Fastbus

You should know this even I skip this as rarely seen nowadays

### VMEbus

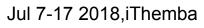

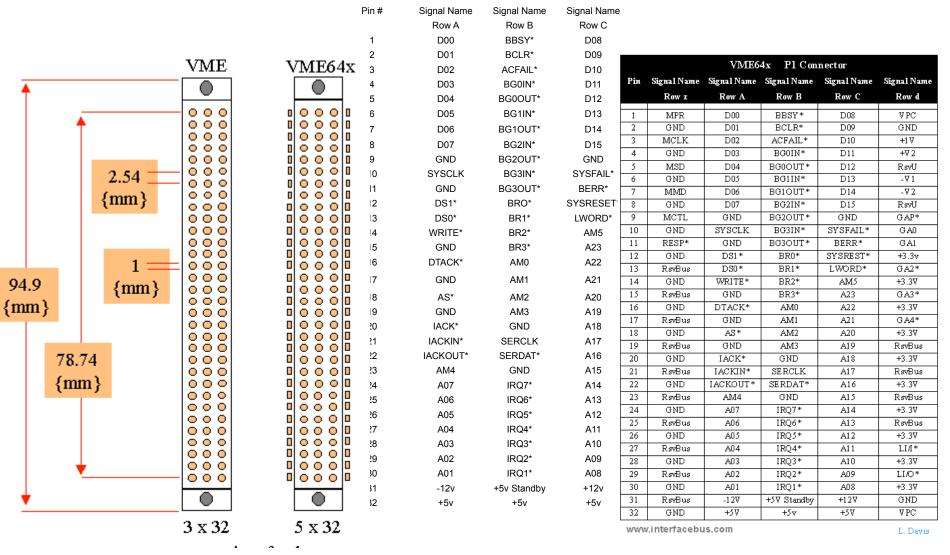

- VMEbus(Versa Module Europa bus)

- a computer bus standard, originally fo the Motorola 68000 CPUs,

- standardized by the <u>IEC</u> as <u>ANSI</u>

/<u>IEEE</u> 1014-1987

- Crate:

- 1-21 stations

- Controller on 1<sup>st</sup>

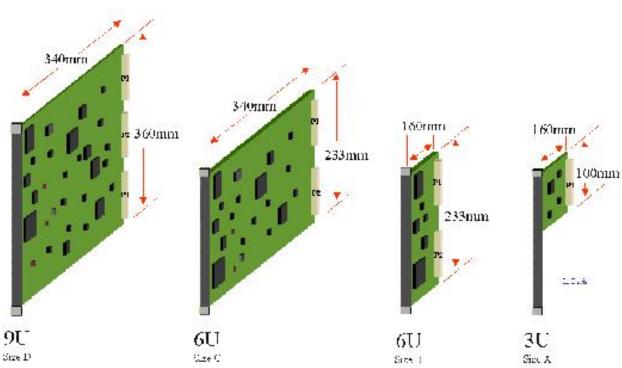

- Modules

- 3U,6U and 9U

- Power:

- VME32: +5volt,and +/-12volt supply;

VME64a 3.3volt supply

### Module types

- Controller

- Master

- Slave

| Evolution of VME               |      |            |                             |  |  |  |  |

|--------------------------------|------|------------|-----------------------------|--|--|--|--|

| Topology                       | Year | Bus Cycle  | Maximum Speed (Mbyte / Sec) |  |  |  |  |

| VMEbus32 Parallel Bus<br>Rev A | 1981 | <u>BLT</u> | 40                          |  |  |  |  |

| VMEbus IEEE-1014               | 1987 | <u>BLT</u> | 40                          |  |  |  |  |

| VME64                          | 1994 | MBLT       | 80                          |  |  |  |  |

| VME64x                         | 1997 | 2eVME      | 160                         |  |  |  |  |

| <u>VME320</u>                  | 1997 | 2eSST      | 320                         |  |  |  |  |

Jul 7-17 2018, iThemba

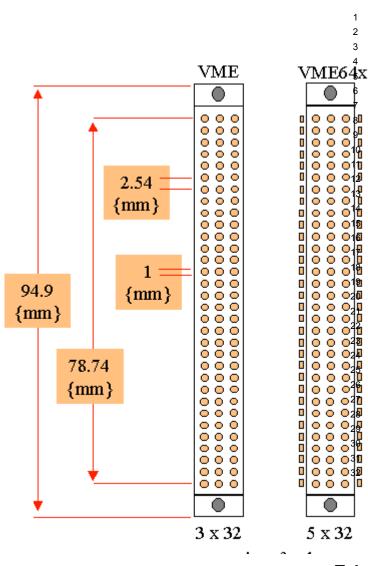

### Module types

- Types

- 3U

- 160×100mm

- P1

- 6U

- 160×233mm

- 340×233mm

- P1 + P2

- 9U

- 340×366mm

- 400×366mm

- P1+P2+P3

- Data/Addr space:

- 8/16/32/64b

Jul 7-17 2018,iThemba

### VMEbus and VME64 P1 Connectors

Jul 7-17 2018, iThemba

### VMEbus and VME64 P2 Connectors

Signal Name Row C

Pin #

1 2 3

$\circ$

$\circ$

$\circ$

$\odot$

$\odot$

$\odot$

$\mathbf{O}^{1}$

Ο.

$\odot$

$\circ$

$\odot$

Ο,

$\odot$

$\odot$

$\bigcirc$

0

$\bigcirc$

$^{\circ}$

$\odot$

$\circ$

030

Oda

⊇do

016

**○**12

្រា

| Signal Name  | Signal Name |

|--------------|-------------|

| Row A        | Row B       |

|              | +5v         |

|              | GND         |

|              | RETRY       |

|              | A24         |

|              | A25         |

|              | A26         |

|              | A27         |

|              | A28         |

|              | A29         |

|              | A30         |

|              | A31         |

|              | GND         |

|              | +5v         |

|              | D16         |

|              | D17         |

| User Defined | D18         |

| User Denned  | D19         |

|              | D20         |

|              | D21         |

|              | D22         |

|              | D23         |

|              | GND         |

|              | D24         |

|              | D25         |

|              | D26         |

|              | D27         |

|              | D28         |

|              | D29         |

|              | D30         |

|              | D31         |

|              | GND         |

|              | +5V         |

|              |             |

|              |             |

|              |             |

|              |             |

|              |             |

|                | VME64x P2 Connector |             |             |             |             |            |  |  |

|----------------|---------------------|-------------|-------------|-------------|-------------|------------|--|--|

|                | Pin                 | Signal Name | Signal Name | Signal Name | Signal Name | Signal Nam |  |  |

|                |                     | Row z       | Row A       | Row B       | Row C       | Row d      |  |  |

|                | 1                   | UsrDef      | UsrDef      | +5V         | UsrDef      | UsrDef     |  |  |

|                | 2                   | GND         | UsrDef      | GND         | UsrDef      | UsrDef     |  |  |

|                | 3                   | UsrDef      | UsrDef      | RETRY       | UsrDef      | UsrDef     |  |  |

|                | 4                   | GND         | UsrDef      | A24         | UstDef      | UsrDef     |  |  |

|                | 5                   | UsrDef      | UsrDef      | A25         | UsrDef      | UsrDef     |  |  |

|                | 6                   | GND         | UsrDef      | A26         | UsrDef      | UsrDef     |  |  |

|                | 7                   | UsrDef      | UstrDef     | A27         | UsrDef      | UsrDef     |  |  |

|                | 8                   | GND         | UsrDef      | A28         | UsrDef      | UsrDef     |  |  |

|                | 9                   | UsrDef      | UsrDef      | A29         | UsrDef      | UsrDef     |  |  |

|                | 10                  | GND         | UsrDef      | A30         | UsrDef      | UsrDef     |  |  |

| fined          | 11                  | UsrDef      | UsrDef      | A31         | UsrDef      | UsrDef     |  |  |

|                | 12                  | GND         | UsrDef      | GND         | UsrDef      | UsrDef     |  |  |

|                | 13                  | UsrDef      | UsrDef      | +5∀         | UsrDef      | UsrDef     |  |  |

| 14<br>15<br>16 | 14                  | GND         | UsrDef      | D16         | UsrDef      | UsrDef     |  |  |

|                | 15                  | UsrDef      | UsrDef      | D17         | UsrDef      | UsrDef     |  |  |

|                | 16                  | GND         | UsrDef      | D18         | UsrDef      | UsrDef     |  |  |

|                | 17                  | UsrDef      | UsrDef      | D19         | UsrDef      | UsrDef     |  |  |

|                | 18                  | GND         | UsrDef      | D20         | UsrDef      | UsrDef     |  |  |

|                | 19                  | UsrDef      | UsrDef      | D21         | UsrDef      | UsrDef     |  |  |

|                | 20                  | GND         | UsrDef      | D22         | UsrDef      | UsrDef     |  |  |

|                | 21                  | UsrDef      | UsrDef      | D23         | UsrDef      | UsrDef     |  |  |

|                | 22                  | GND         | UsrDef      | GND         | UsrDef      | UsrDef     |  |  |

|                | 23                  | UsrDef      | UsrDef      | D24         | UsrDef      | UsrDef     |  |  |

| 24<br>25       | 24                  | GND         | UsrDef      | D25         | UsrDef      | UsrDef     |  |  |

|                | 25                  | UsrDef      | UsrDef      | D26         | UsrDef      | UsrDef     |  |  |

|                | 26                  | GND         | UsrDef      | D27         | UsrDef      | UsrDef     |  |  |

| 27             | 27                  | UsrDef      | UsrDef      | D28         | UsrDef      | UsrDef     |  |  |

|                | 28                  | GND         | UsrDef      | D29         | UsrDef      | UsrDef     |  |  |

| 29<br>30<br>31 | 29                  | UsrDef      | UsrDef      | D30         | UsrDef      | UsrDef     |  |  |

|                | 30                  | GND         | UsrDef      | D31         | UsrDef      | UsrDef     |  |  |

|                | 31                  | UsrDef      | UsrDef      | GND         | UsrDef      | GND        |  |  |

|                | 32                  | GND         | UsrDef      | +5v         | UsrDef      | V PC       |  |  |

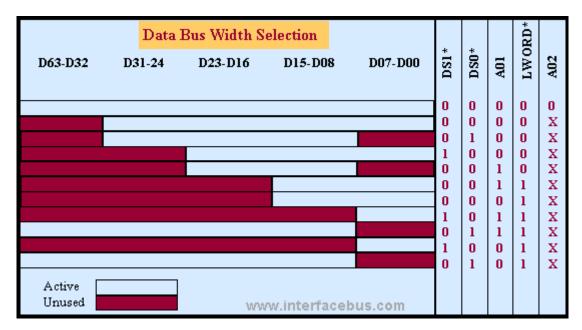

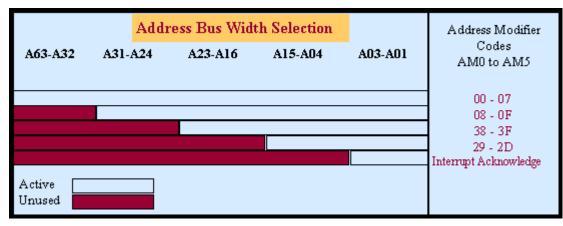

# Data Width and Adr. Width

- Data Width:

8-64bits

- Addr Width

8-64bits

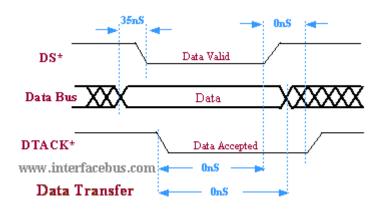

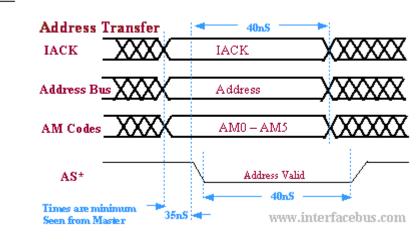

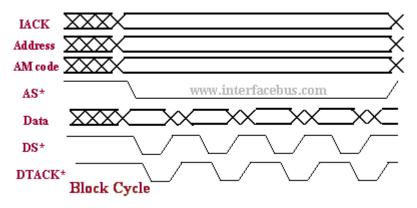

# Timing

0nS

(XXXXX

- Strobe

- As

- DTACK

- Block

35nS

DS\*

DTACK\*

Data Bus XXX

www.interfacebus.com

Data Transfer

Data Valid

Data

0nS

0nS

Data Accepted

Jul 7-17 2018,iThemba

### **New Standard**

Jul 7-17 2018,iThemba

### Problem with BUSed crate?

• Beijing Traffic. The Rings(BUSs) make problem!

### Good solution like Cape Town Routes

Point to point direct or via limited routing

Jul 7-17 2018,iThemba

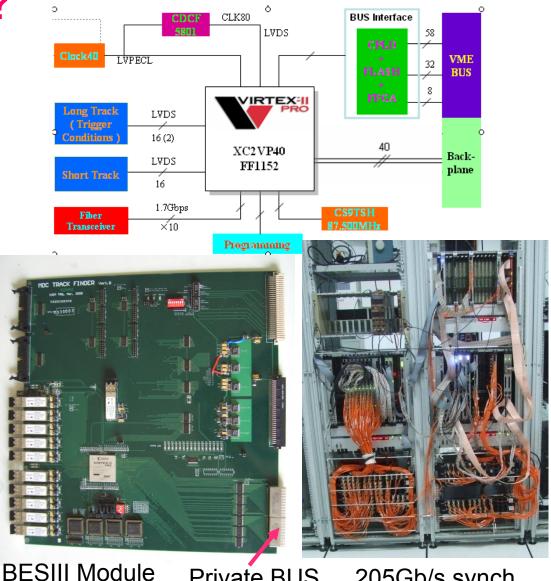

### We did meet BUS Problems! New

### Standard again?

- VME (2003/4) Not satisfactory

- Higher samples/s

- Powerful FPGA

- >3Gbps transmission

- reconfiguration

- Problem

- Bus bandwidth too low

- No serial interconnection

- No Intelligence

- New standard is needed

Z.A.LIU Intl. School on RT System 2018

205Gb/s synch trans. In BESIII 44

Jul 7-17 2018, iThemba

8,iThemba Z.A.

# Pre-xTCA workshops

- At same time, ongoing International Linear Collider, XFEL workshops

- 2004 ATCA, MTCA intro paper NSS-MIC, Rome

- 2005 ILC Snowmass Conference + Availability

Workshop @ Grömitz on ATCA for *high availability*

- 2007 1<sup>st</sup> ATCA workshop, IEEE RT2007 Fermilab

- 2008 2<sup>nd</sup> ATCA workshop, IEEE NSS-MIC

Dresden

### What is the new standard?

- ATCA

- Advantages

- High speedIO and 10Gb/s interconnections

- HA ~99.999%

- IP management

- MicroTCA (MTCA)

- Advantages of ATCA

- Half height, compact system

Should we adopt industrial standard again as VME?

Good idea!

- AdvancedMC (AMC)

- Modular design

Jul 7-17 2018,iThemba

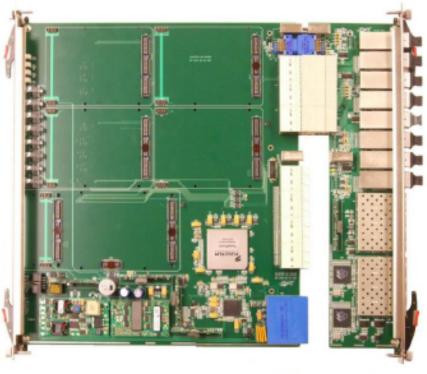

### Why xTCA for Physics

- ATCA shortages

- Height 8U, not suitable for machine control

- No rear transition board yet

- No control signals >>>

- MTCA shortages

- No rear transition board yet (HA)

- No control sysnals …

- AMC shortages

- Inter connection?

- Control signals?

- pin signal difinition

Compute Node designed by IHEP

New standard: xTCA for Physics

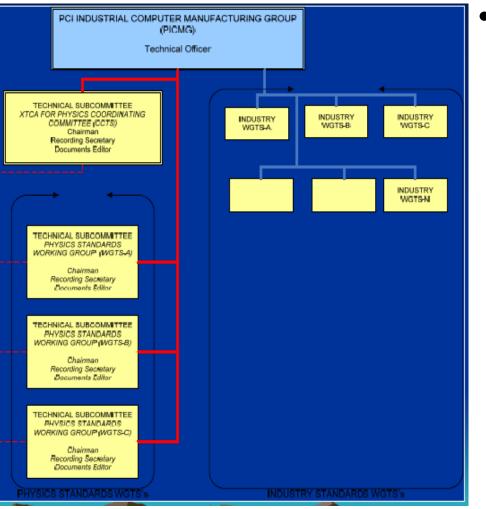

# It is possible to have a direct link!

- YES! That ATCA/xTCA

- 2009 –xTCA for Physics subcommittees formed under PICMG open source telecom standards ~200 vendors

- 2009 First xTCA Workshops at Beijing

### **xTCA for Physics CCTS**

- Founded Mar. 10 2009

under PICMG

- IHEP, SLAC, FNAL, DESY

- >40 companies

- Officers

- Chair: SLAC Ray Larsen

- Secretory: TriCircle Augustus Lowell

- Doc Editor: IHEP Z.A.Liu

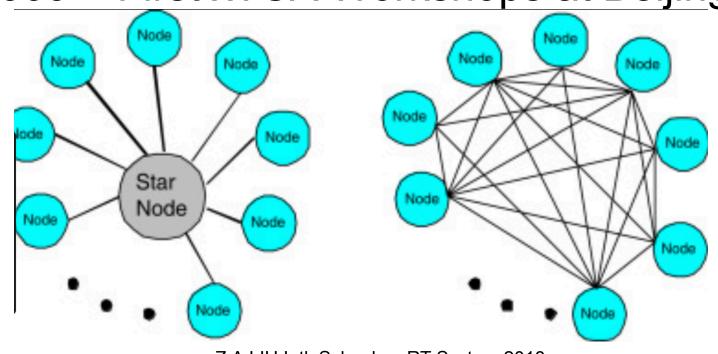

# **xTCA** features

- ATCA & MicroTCA Unique Features

- ATCA board, shelf is first modular computer architecture with completely serial multi-Gbps backplane

- Serial ports are bidirectional pairs in star or mesh topology

- Serial bit rate of one port at 2.5 Gbps exceeds data rate of parallel bus backplanes, e.g. VME 32/64 bit word at 10 MHz => 320/640 Mbps (*now 2.5G*=>10G=> 40 G)

- Architecture based on FPGAs with imbedded SERDES Tx-Rx, LVDS balanced logic

- High processing power of single ATCA card (Blade)

- MCH enables module to any other module communication

- Special low jitter switches for clocks

- Dual redundancy MCH, Processor, Power Units optional

Jul 7-17 2018,iThemba

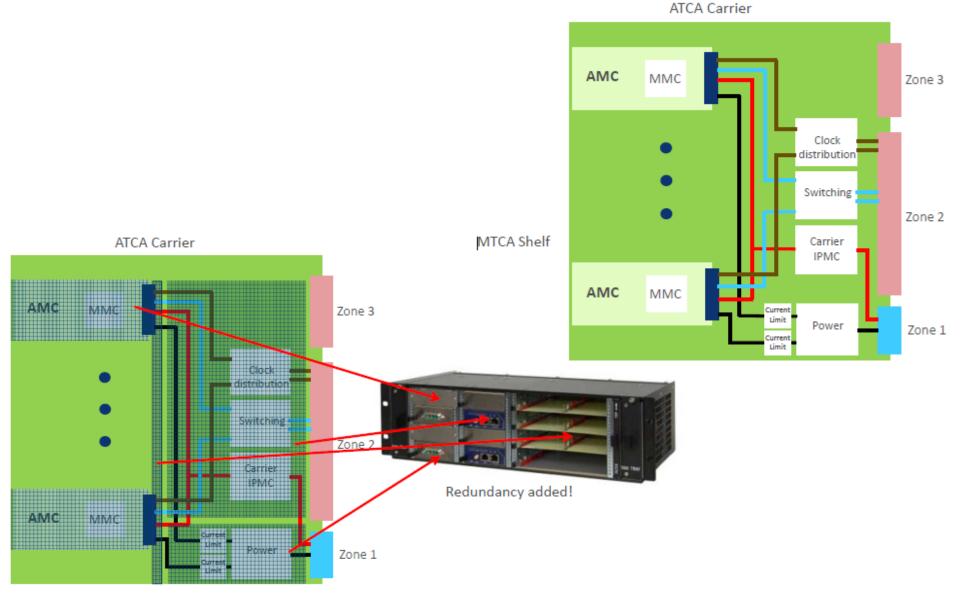

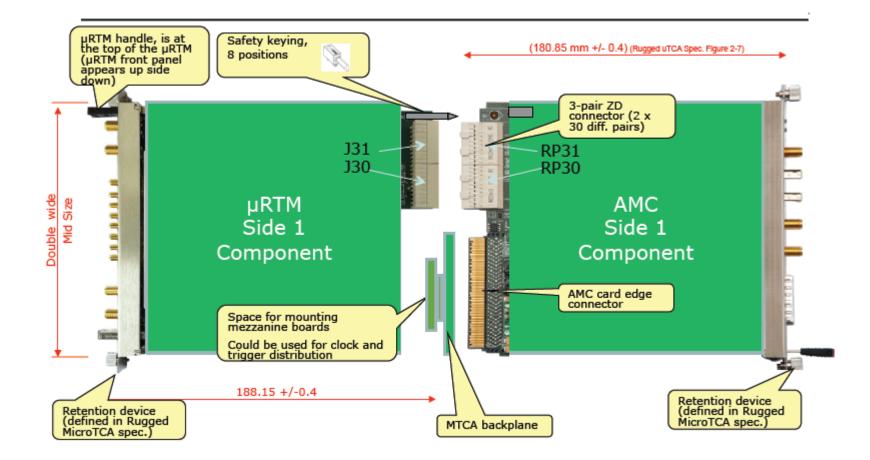

### **xTCA Standards – Hardware Extensions**

- Rear Transition Modules

- ATCA Card => PICMG 3.8

- Zone 3 area defined but interface left to discretion of vendors

- Severely limits interoperability of vendor modules

- Physics developed ATCA Standard RTM Interface

- Fabric, power, JTAG, IPMI, managed from ATCA

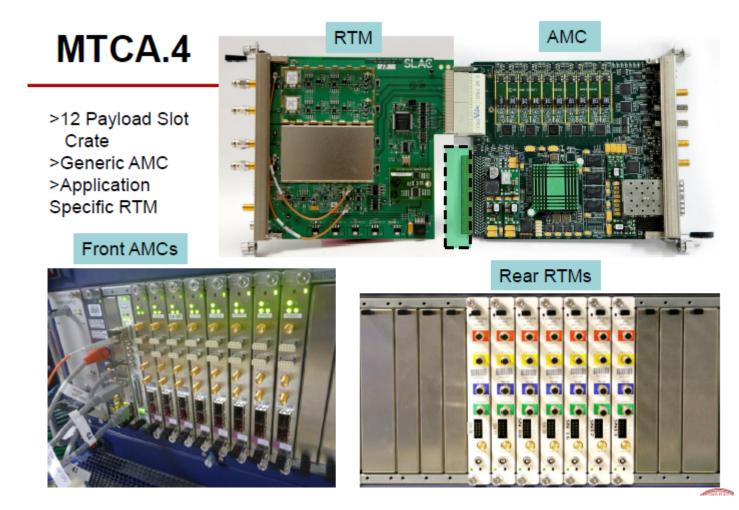

- MicroTCA Double-Wide Card => MTCA.4

- MTCA.0 defined double-wide AMC but not Zone 3 or RTM mechanics

- MTCA.4 developed new crate, RTM, interface, cooling

- Fabric, power, JTAG, IPMI, managed from AMC

- RTM hot-swappable

### **xTCA Physics Extensions to PICMG Standards**

# xTCA Extn: Physics Design Guide ATCA

Physics Design Guide for Clocks, Gates & Triggers in Instrumentation

> PDG.0 R0.8 19 March 2013

# xTCA further Extension: MTCA.4.1 for RTM backplane

Jul 7-17 2018, iThemba

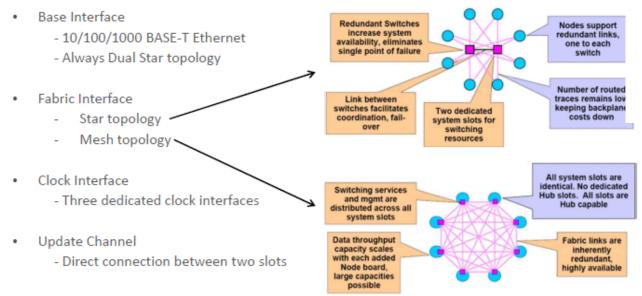

### ATCA

#### ATCA Interfaces

#### Zone 2 Backplane Interfaces

#### Point to Point Link speed: 10Gbps

# AMC/ATCA/MTCA.0

- AMC: Advanced Mezzanine

Card

- Initially developed as function extension for ATCA Boards

- Fully integrated into the ATCA IPMI management structure

- Plugged into a so called ATCA Carrier

- Hot Swap capability

MTCA

ATCA

Jul 7-17 2018,iThemba

### ATCA Carrier/MTCA.0

Jul 7-17 2018, iThemba

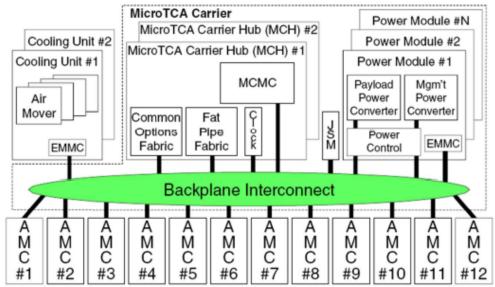

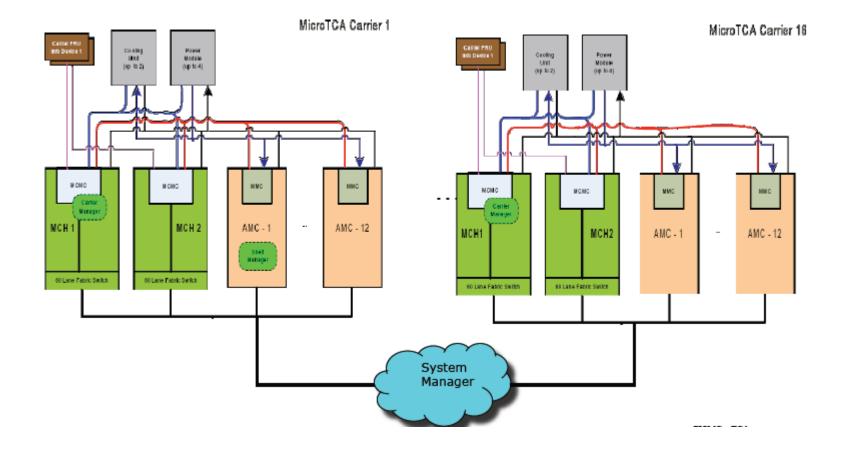

# MTCA.0

#### **Terms and Acronyms**

- MCH MicroTCA Carrier Hub

- · This is the complete module you can buy from a vendor

- MCMC MicroTCA Carrier Management Controller

- · This is the physical IPMI controller on the MCH

- MMC Module Management Controller

- · This is the physical IPMI controller on an AMC

- EMMC Enhanced MicroTCA Carrier Management Controller

- This is the physical IPMI controller on a Cooling Unit and on Power Module

- IPMB-0 Intelligent Platform Management Bus 0

- Logical IPMB, physically divided into redundant IPMB-A and IPMB-B

- IPMB-L IPMB-Local

- IPMI link between MCH and AMCs

#### Jul 7-17 2018,iThemba

Z.A.LIU Intl. School on RT System 2018

#### MicroTCA block diagram

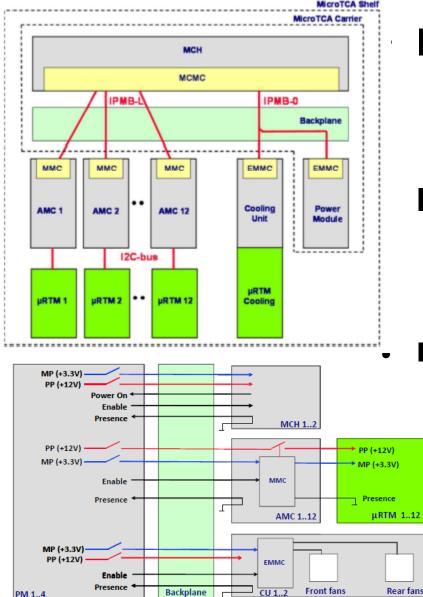

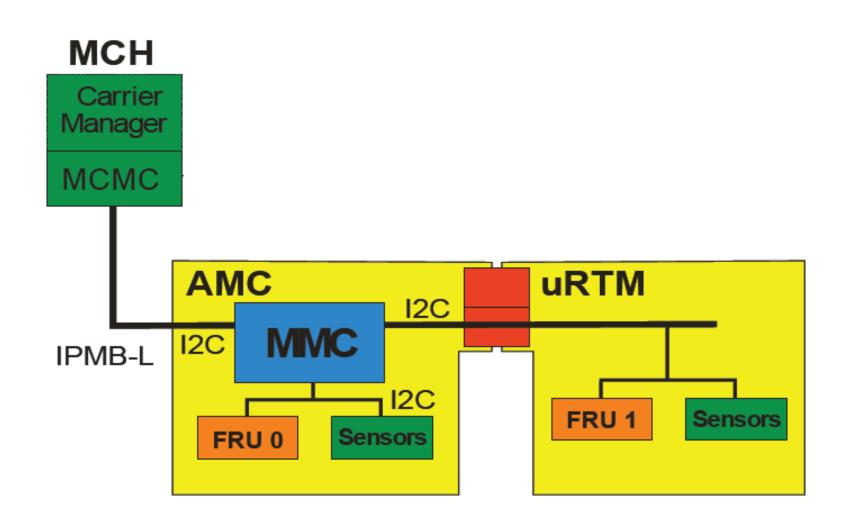

### Management extensions in MTCA.4

Jul 7-17 2018.iThemba

### IPMB-L

- Connects the MCMC on the MCH to the MMC on the AMC Modules

- Radial architecture

### IPMB-0

- Connects the MCMC on the MCH to the EMMC on the PM and CU

- Bused architecture

### I2C-Bus

- Connects the AMC to the  $\mu$ RTM

- The  $\mu$ RTM is treated as managed

- FRU of the AMC

Z.A.LIU Intl. School on RT System 2018

59

## MTCA.4 (xTCA for Physics) AMC and uRTM

Jul 7-17 2018, iThemba

### A lot progress in hardware development

• At DESY, SLAC, IHEP (see later)

### MTCA.4 – Hardware Management

### MCH Functionality:Management

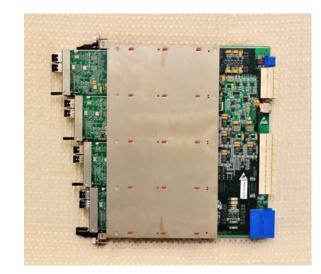

# Examples at TrigLab/IHEP AMC/ATCA

for PANDA

### Examples at TrigLab/IHEP

Ľ

BelleII/Belle2link

BelleII/

PXD/DAQ

# Examples at TrigLab/IHEP

- CMS Trigger Upgrade

- Inputs:

- 10 Gbps/ch, 36 Chs

- Outputs:

- 10Gbps, 12 chs

- Concentration, PreProcessing and Fanout

# Summary

- Signal Levels and BUS standards are introduced

- Please refer to PICMG 3.8, MTCA.4, PDG .0 MTCA.4.1 and some more to be developed.

- Standardization is not only in Physics Experiment, but anywhere as you see.

- Start following the standard will save you a lot.

### Backups

Jul 7-17 2018,iThemba