# First results on irradiated OVERMOS1 HR CMOS for HEP applications

<u>E. G. Villani</u> <u>STFC Rutherford Appleton Laboratory</u> on behalf of OVERMOS project collaboration

# Overview

- OVERMOS1 description

- First test results of irradiated / non –irradiated OVERMOS1

- (Some) TCAD simulation

- Conclusions and next steps

## **OVERMOS** description

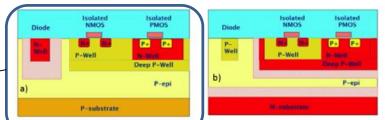

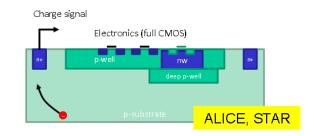

OVERMOS features DPW originally // proposed for ILC

MAPS imagers / detectors normally suffer from poor radiation tolerance due to slow charge collection OVERMOS is a MAPS project demonstrator fabricated using TJ 180 nm Hi-res

Electronics outside charge collection well

- Very small sensor capacitance  $\rightarrow$  low power

- Potentially less rad. hard (longer drift lengths)

- Full CMOS with additional deep-p implant

# **OVERMOS1** description

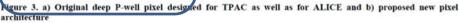

- The OVERMOS1 ASIC was fabricated using TowerJazz HR CMOS 180 nm P-type wafer, 18 um epitaxial layer

- Current OVERMOS1 addresses some previous issues found in OVERMOS

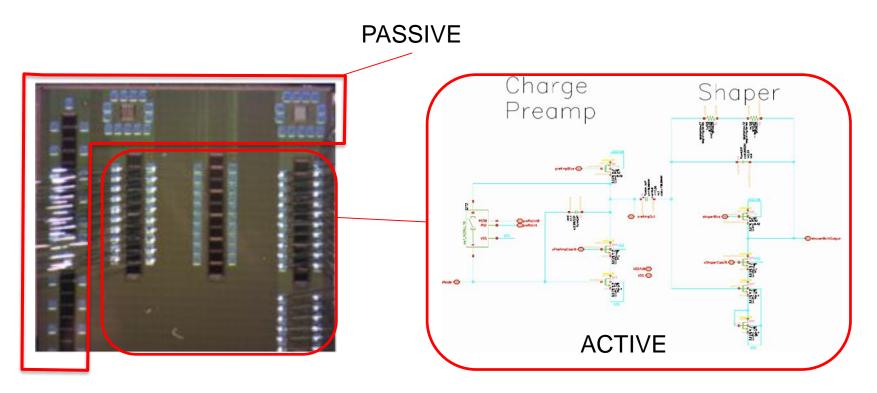

- The ASIC logically consists of PASSIVE and ACTIVE pixels, i.e. without and with in-pixel electronics respectively;

## **OVERMOS1** description

Pixel Types:

- Basic Passive: Basic diode (40u x 40u). 5x5 array. No in-pixel electronics. Inner 9 pixels individually accessible. Outer 14 jointly connected.

- Basic Active: Basic diode (40u x 40u).. 5x5 array. In-pixel electronics. Inner 9 pixels individually accessible. Outer 14 jointly connected.

- Basic Active AC: Basic diode (40u x 40u).. 5x5 array. In-pixel electronics. Inner 9 pixels individually accessible. Outer 14 jointly connected. Diode AC coupled to electronics with independent diode biasing.

- Symmetric Passive: Symmetric diode (40u x 40u).. 5x5 array. No in-pixel electronics. Inner 9

pixels individually accessible. Outer 14 jointly connected.

- Basic Passive Large: Basic diode (40u x 400u). 5x5 array. No in-pixel electronics. Inner 9

pixels individually accessible. Outer 14 jointly connected.

- Basic Active Large: Basic diode (40u x 400u). 5x5 array. In-pixel electronics. Inner 9 pixels individually accessible. Outer 14 jointly connected.

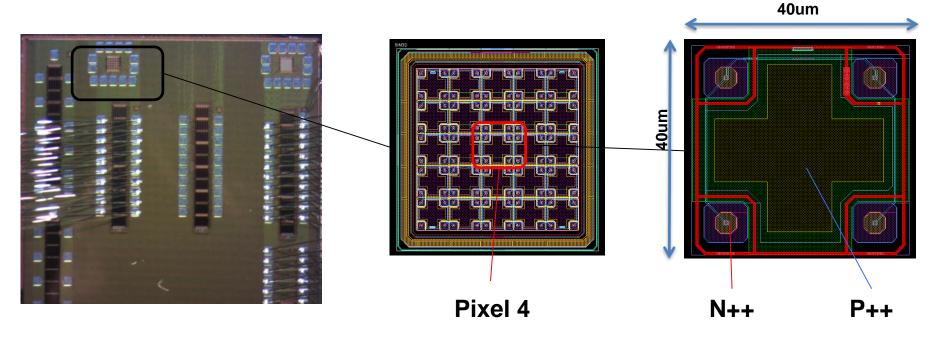

### **OVERMOS1** description

- All the pixels in the OVERMOS1 include an p++ region around each diode to isolate them from neighbouring ones, an issue that plagued the previous version of OVERMOS

- Diodes size 4.5 x 4.5 um2

- The OVERMOS1 ASIC 'basic passive' has been tested before and after n-irradiation for DC and charge collection

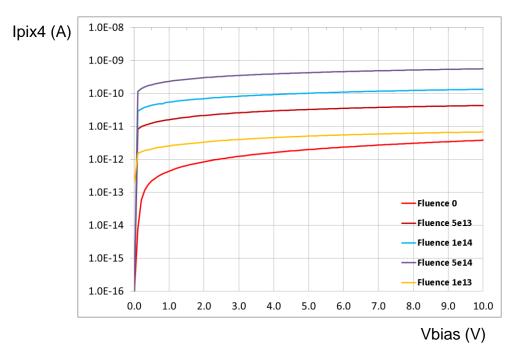

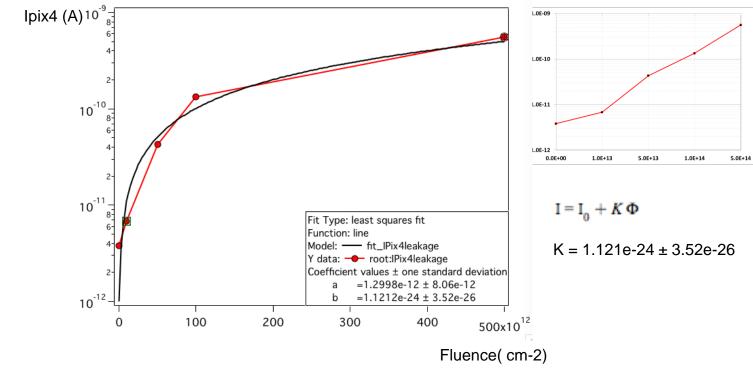

### Single pixel leakage currents

- OVERMOS1 irradiated at Ljubljana in October 2017

- 1E13, 5E13,1E14 and 5E14 n fluence

- The OVERMOS was glued onto a carrier and wirebonded

- Leakage currents test results of single pixel 4 with substrate and other pixels floating

#### Single pixel leakage currents

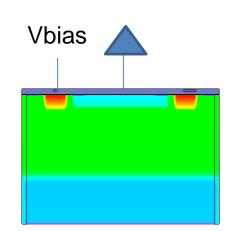

$I_{leak}$  vs. Fluence @  $V_{bias}$  = 10 V

#### (Substrate floating, all other pixels left floating)

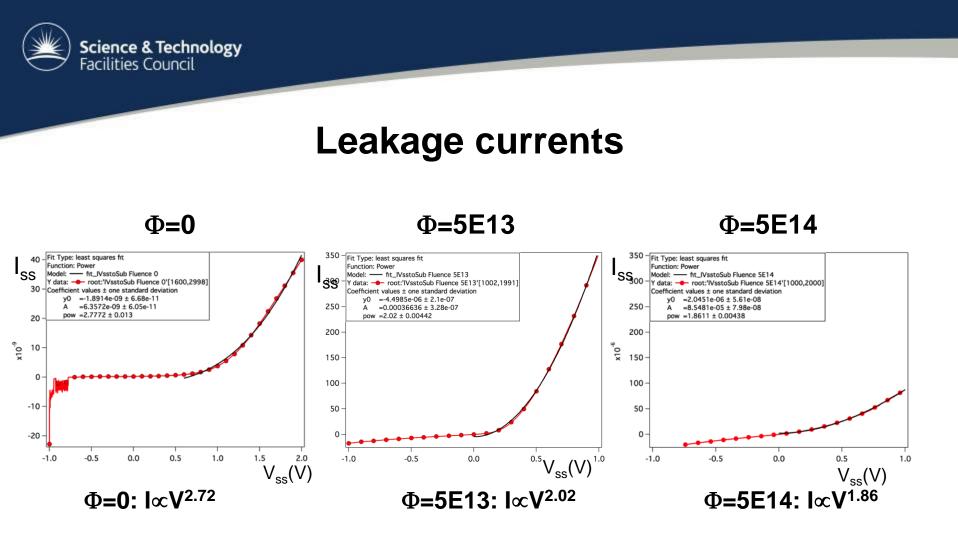

Fitting @ 5E13 shows a nearly ideal V^2 dependence The power coefficient depends on the fitting Only one device/ each radiation level Asymmetry w.r.t. Vss may be due to conductive glue at the substrate

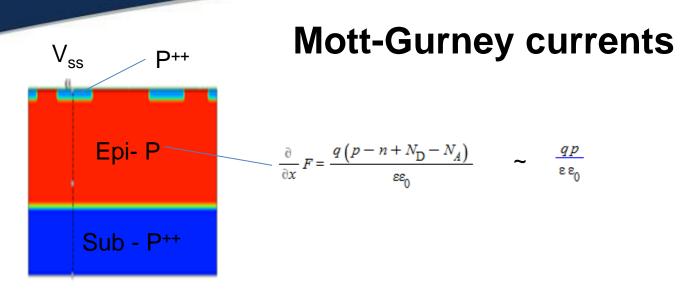

Leakage current is measured between P wells (top and substrate) For constant current and assuming only drift component

$j = q p \mu_p F \longrightarrow p = \frac{j}{q \mu_p F} \longrightarrow \frac{\partial}{\partial x} F = \frac{j}{\varepsilon \varepsilon_0 \mu_p F}$  $\int_0^x F \left(\frac{\partial}{\partial z} F\right) dz = \int_0^x \frac{2j}{\varepsilon \varepsilon_0 \mu_p} dz \longrightarrow F^2 = \frac{2jx}{\varepsilon \varepsilon_0 \mu_p}$  $-\left(\int_0^{Z_{epi}} F dx\right) = V_{SS} \longrightarrow j = \frac{9}{8} \frac{\varepsilon \varepsilon_0 \mu_p V_{SS}^2}{Z_{epi}^3}$

#### **Charge collection**

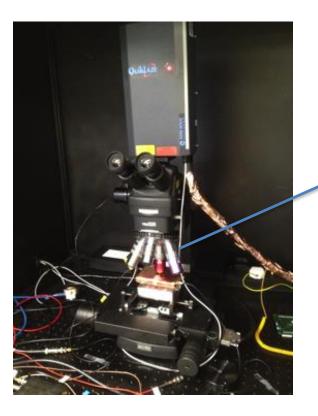

Charge collection studies performed using Laser injection:

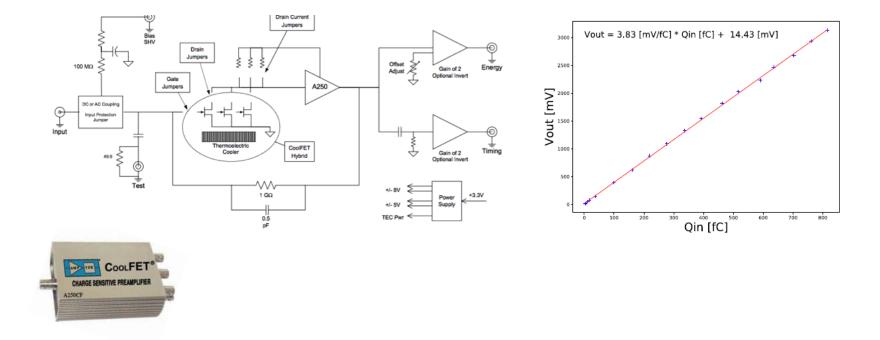

1:Amptek A250CF calibrated using mV voltage pulses injected through (measured) 1.2 pF capacitor to get V(Q). RMS Noise  $\approx$  76 e- @ OVERMOS capacitance

#### **Charge collection**

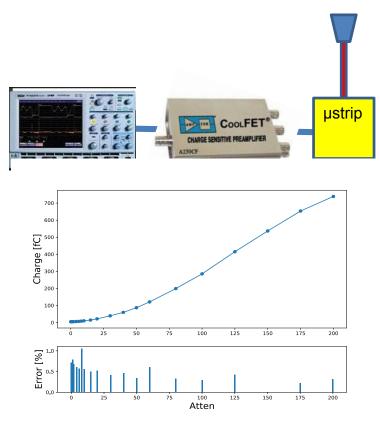

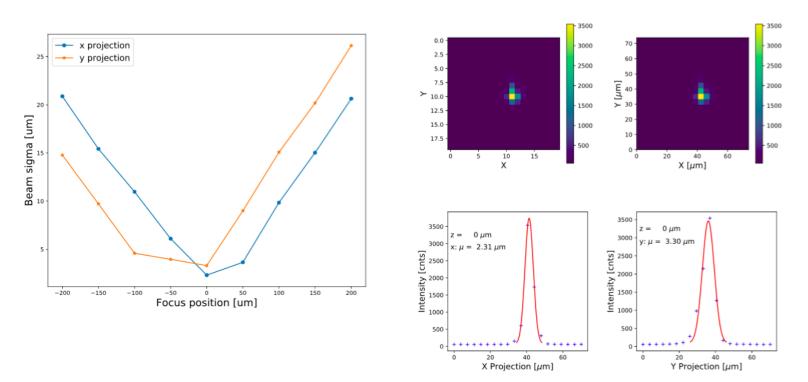

2: Trilite Laser 1064 nm calibration using a 300 um Si sensor, 1um top passivation. Laser beam size 5 x 5 um2 (measured with beam profiler), 4.1 ns FWHM (measured with FEMTO 2 GHz optoreceiver), 50 Hz repetition rate. Up to 5 points measured on sensor to calculate average injected charge

#### **Charge collection**

OVERMOS In metal box to reduce EMP noise

3: the calibrated Laser was used to inject <Q injected> = 541.66 or 1.805 fC/um (corresponding to  $\approx$  150 Laser attenuation, which gave the minimum error %) (not taking into account IR reflection on ASIC's top)

#### **Collected charge**

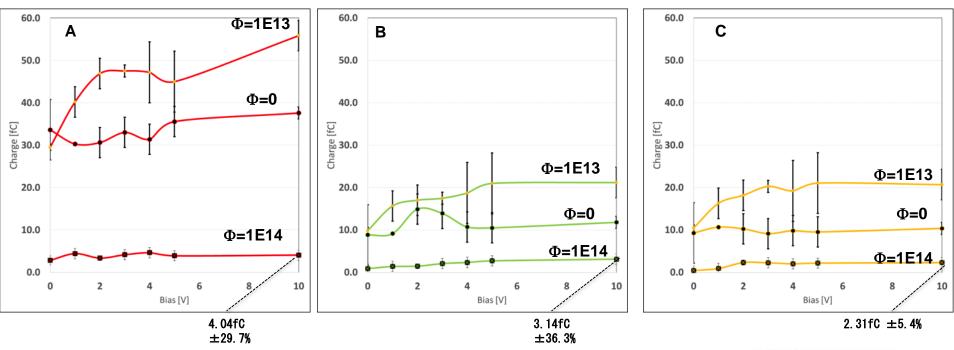

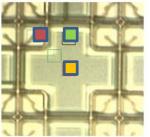

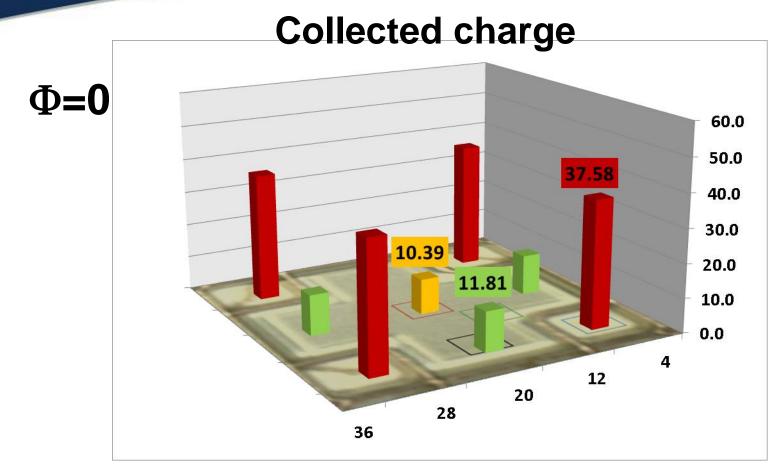

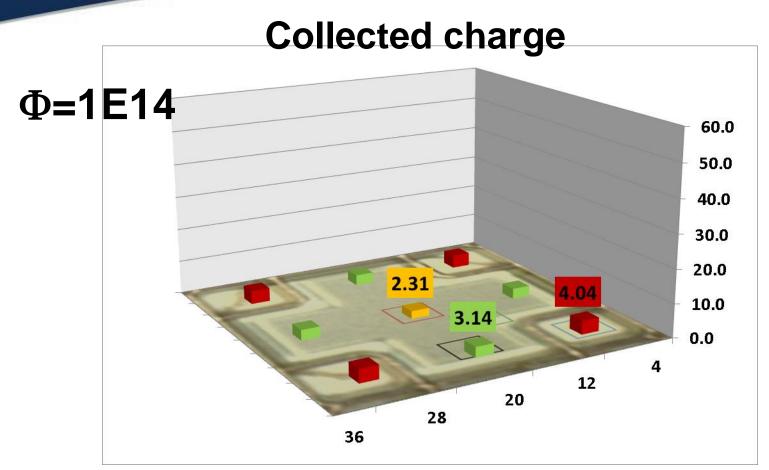

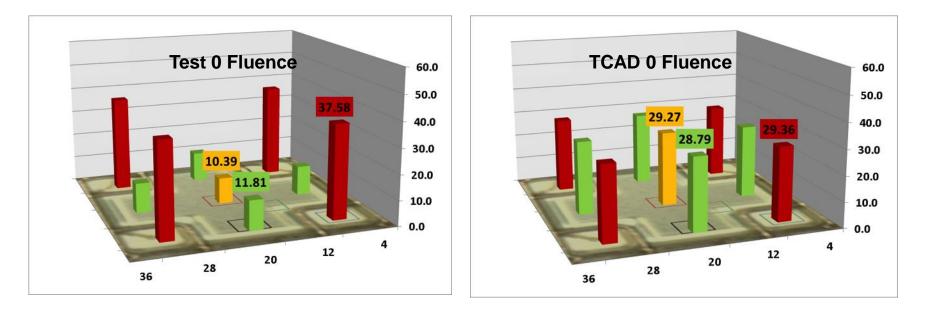

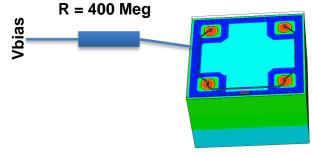

Total collected charge vs. Vbias , points A,B,C. Integration time 400 ns <Q injected> = 1.805 fC/um HVbias provided through the A250CF, via a 400 Meg resistor chain

Laser injection test results (1064 nm, 5 x 5 um2 beam size) Vbias = 10V <Q injected> = 1.805 fC/um

Laser injection test results (1064 nm, 5 x 5 um2 beam size) Vbias = 10V <Q injected> = 1.805 fC/um

Laser injection test results (1064 nm, 5 x 5 um2 beam size) Vbias = 10V <Q injected> = 1.805 fC/um

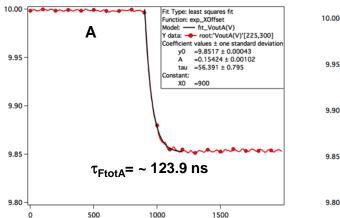

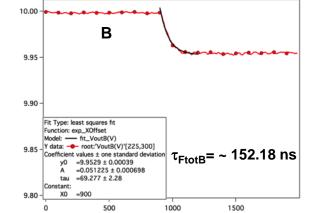

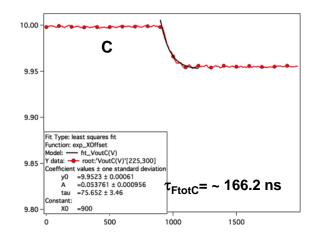

### **Collected charge transient**

Collected charge vs. time, points A,B,C Vbias = 10V,  $\Phi = 0$ <Q injected> = 1.805 fC/um

AMPTEK A250CF  $\tau_{RAMP}$ = 15 ns

$$\tau_{Fs} \sim sqrt((\tau_{Ftot})^2 - (\tau_{RAMP})^2) \sim$$

A: 123 ns B: 151.4 ns C: 165.5 ns

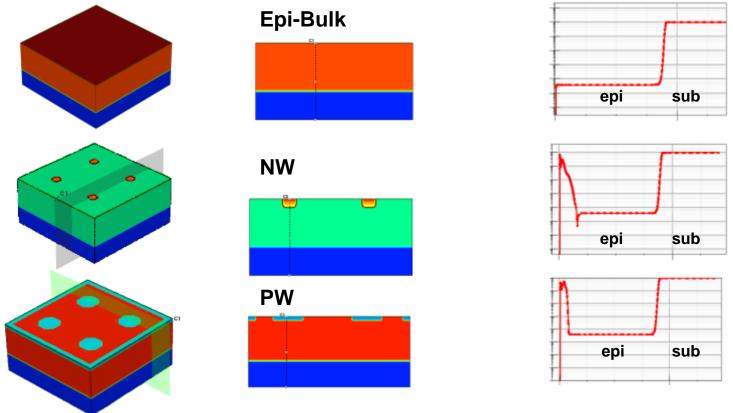

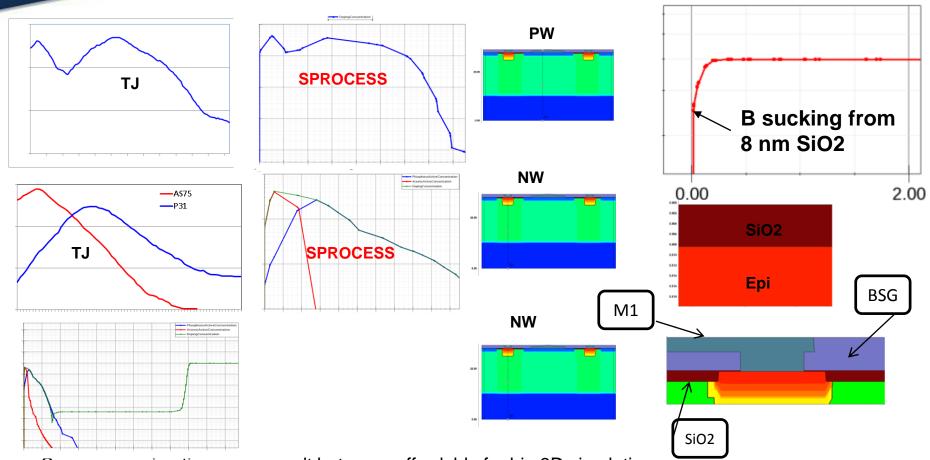

#### **TCAD** simulations

- Individual doping profiles for OVERMOS/DECAL were obtained using SPROCESS, to simulate a (simplified) CMOS fabrication by TowerJazz

- These (1D) doping profiles were then implemented in SDE

- Huge reduction in mesh size and computation time

- Some approximations as a result but more affordable for big 3D simulations:

- No B sucking

- No lateral spread doping information

- Coarser doping profiles

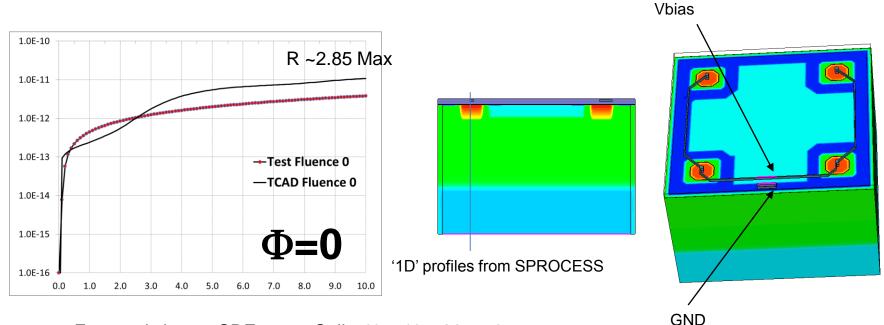

# TCAD simulation results Leakage currents

From .gds layout SDE to get Cell : 40 x 40 x 29 um3

Mesh size: 340974 points SRV 1e4

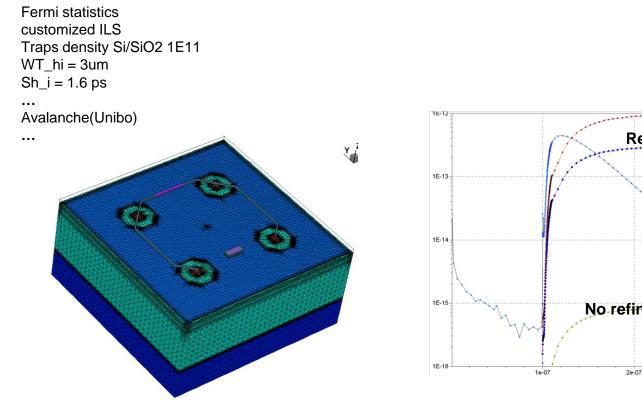

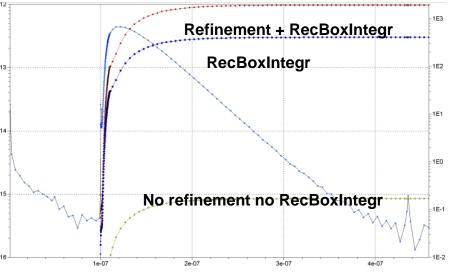

# TCAD simulation results Transient simulation

Initial Charge collection simulation with SRH disabled, to optimize temporal/spatial meshing Refinement along the hit track, with refinement that depends on the Debye length~ 1 x Debye length (Epi), ~ 10's x Debye length (Sub)

# TCAD simulation results Collected charge

TCAD 0 Fluence Heavy Ion statement 1.805e-3 pC/um Vbias = 10V provided through R = 400 Meg

# Conclusions and next steps

- First test results of OVERMOS basic flavor were presented: DC tests showed expected leakage increase with n-fluence and initial increase in charge collection, measured with Laser injection

- Charge collection drops by tenfold at  $\Phi = 1e14$

- Next: to fully characterise the remaining sensors and TCAD simulations

#### BACKUP

Laser beam size vs. focusing – Measured beam size with beam profiler