# TCT for the characterization of silicon interfaces obtained by CMOS compatible wafer bonding

#### Jacopo Bronuzzi, jacopo.bronuzzi@cern.ch

Alessandro Mapelli<sup>1</sup>, Michael Moll<sup>1</sup>, Luciano Musa<sup>1</sup>, Walter Snoeys<sup>1</sup>, Petra Riedler<sup>1</sup>, Eric Rouchouze<sup>3</sup>, Catherine Charrier<sup>3</sup>, Frank Fournel<sup>3</sup>, Jean-Michel Sallese<sup>2</sup> <sup>1</sup>Detector Technologies Group, EP Department, CERN, <sup>2</sup>Group of Electron Device Modeling an Technology, EDLAB, EPFL, <sup>3</sup>Silicon Platform, CEA-LETI

<sup>1</sup><u>https://ep-dep-dt.web.cern.ch/</u> <sup>2</sup><u>http://www.leti-cea.fr/cea-tech/leti/Pages/innovation-industrielle/innover-avec-le-Leti/LETI-3S.aspx</u> <sup>3</sup>https://edlab.epfl.ch/

### Outline

- CMOS compatible wafer bonding

- Bonded Monolithic Active Silicon Sensors

- TCT for bonding interface characterization

- Analytical modeling of TCT for bonding interface characterization

- Fabrication of test structure for TCT bonding interface characterization

- Electrical injection TCT

- Working principle

- Clean room fabrication of test structures

- Measurements setup description

- Measurements and proof of principle

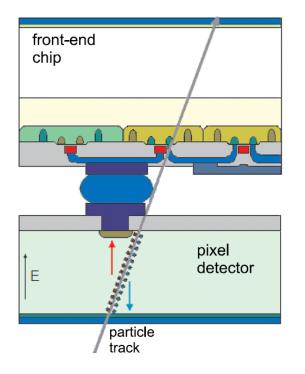

### **Pixel detectors**

Hybrid silicon pixel detector

Petra Riedler, Monolithic silicon pixel sensors and technology challenges of the alice its, 2015. L. Rossi et al., Pixel Detectors: From Fundamentals to Applications, *Springer*, 2006.

### Monolithic Active Pixel Sensor (MAPS)

- Robust

- Thin detectors

- Low parasitic capacitance

- No need for expensive bump bonding

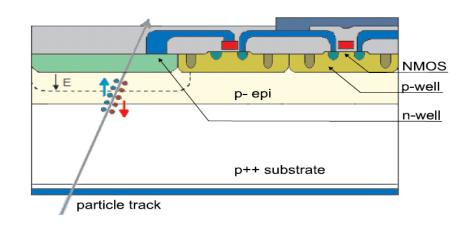

### Fabrication of monolithic pixel detectors

### **Electronics driven**

- Low resistivity silicon

- High performance electronics

- Low performance sensing (small depletion region)

### Sensor driven

- High resistivity silicon

- Difficult electronics design

- High performance sensing (large depletion region)

L. Rossi et al., Pixel Detectors: From Fundamentals to Applications, Springer, 2006.

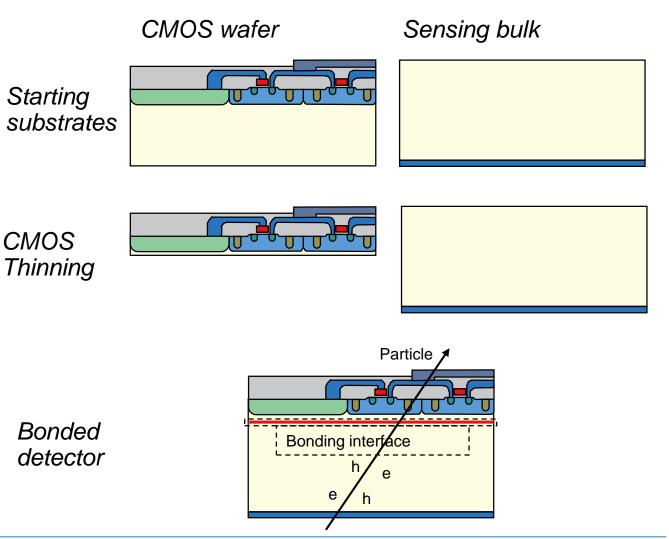

### Bonded monolithic detectors

# Monolithic Active Pixel Sensors fabrication

- Bonding of sensing bulk on the back side of CMOS circuitry

- Monolithic silicon detectors with optimized characteristics:

- CMOS on low resistivity silicon

- Sensing bulk on high resistivity silicon

- Bonding interface electrical properties to be studied

cea

**EP-DT**

**Detector Technologies**

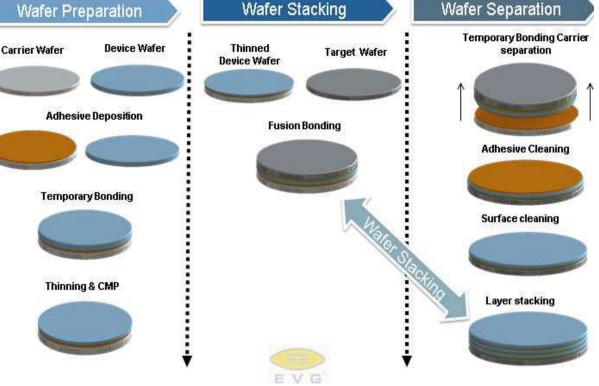

# CMOS compatible wafer bonding

#### **Process**

- Complete process in vacuum (EVG®580) ComBond®)

- Dry etching of native SiO<sub>2</sub>

- Bonding at 200°C for 60 min, with an applied pressure of 0.06MPa

- Possibility of thin wafers stacking

### **Results**

- Si bulk fracture strength reached (2.5  $J/m^2$ )

- Oxide-free amorphous silicon interface (3 nm)

. 64, no. 5, pp. 103–110, 2014.

s. vol. 64, no. 5, pp. 95–101, 2014.

$$20$$

November 6

2017

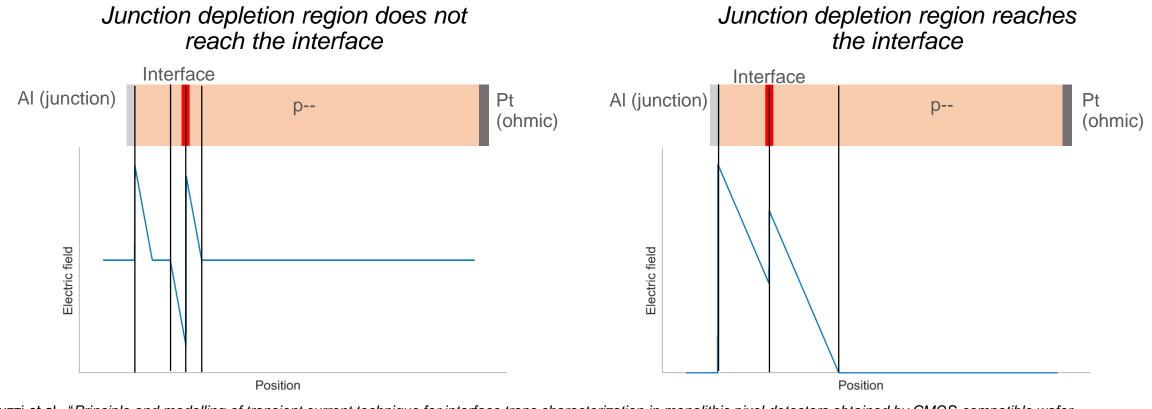

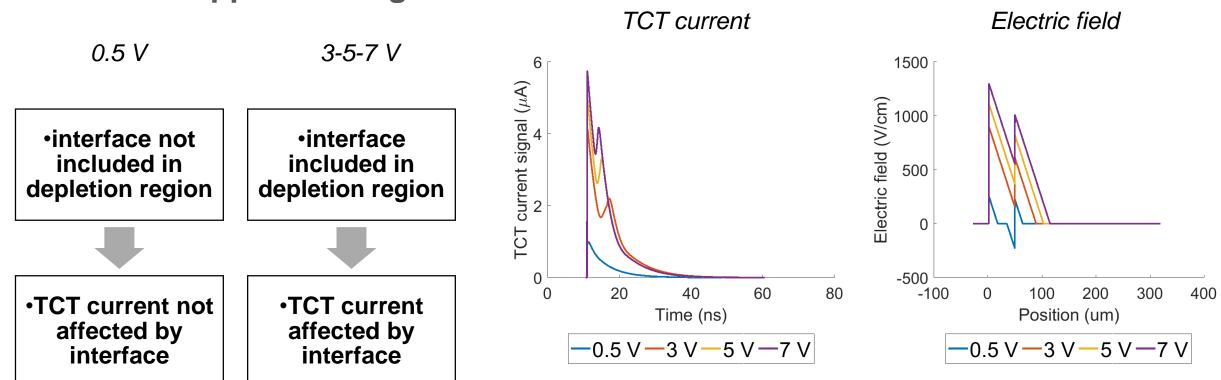

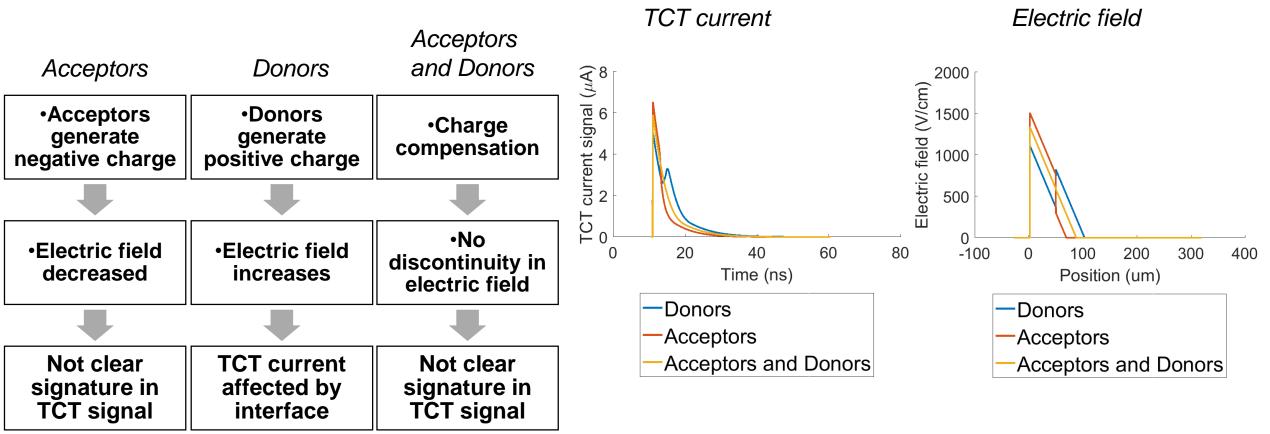

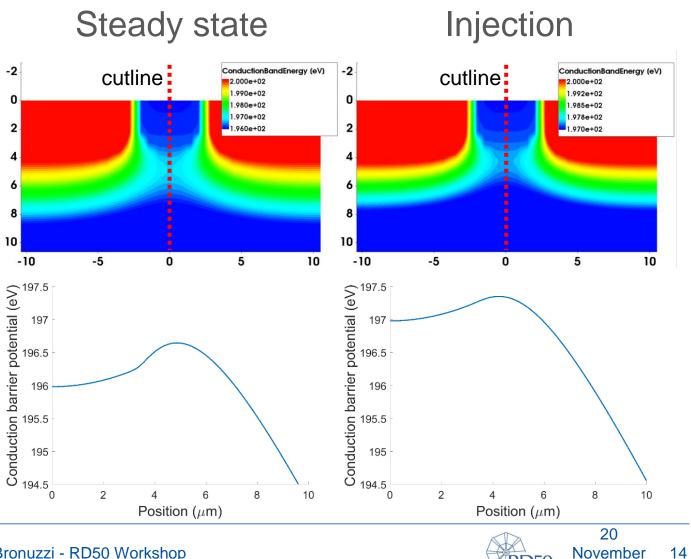

### Method of interface characterization using TCT

Amorphous silicon at the bonding interface can be modeled as a layer with a trap density 1e16 cm<sup>-3</sup> Analytical modeling of TCT transient current for bonding interfaces, 2 cases:

J. Bronuzzi et al., "Principle and modelling of transient current technique for interface traps characterization in monolithic pixel detectors obtained by CMOS-compatible wafer bonding", JINST, 11 P08016, 2016.

### TCT for bonding interface traps

#### Different applied voltage

### TCT for bonding interface traps

#### **Different traps type**

20

November

2017

**RD50**

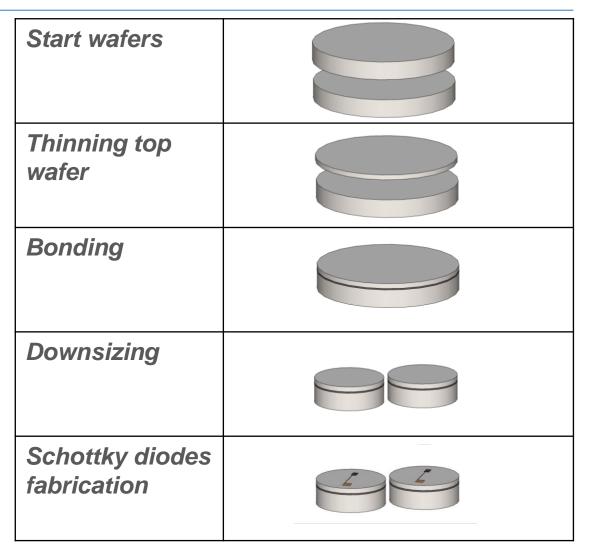

### **Test structures fabrication**

CMOS compatible bonding of silicon wafers at CEA-LETI:

- Silicon wafers: 8 inches, magnetic Czochralski P-type, ρ > 5000 ohm.cm

- Thinning (tolerance 1 µm), to have interface close to surface, and bonding (pressure 30 kN)

- Downsizing from 8 inches to 4 inches through laser cut

- Fabrication of Schottky diodes on top of wafers (at CMi EPFL) to be studied with TCT

| Substrate | Top wafer<br>thickness |             | Annealing<br>temperature |

|-----------|------------------------|-------------|--------------------------|

| P1        | 20um                   | Hydrophobic | 400°C                    |

| P2        | 20um                   | Hydrophilic | 400°C                    |

| P3        | 50um                   | Hydrophobic | 400°C                    |

| P4        | 50um                   | Hydrophobic | 400°C                    |

| P5        | 50um                   | Hydrophobic | T amb                    |

| P6        | 50um                   | Hydrophobic | T amb                    |

| P7        | 50um                   | Hydrophilic | 400°C                    |

| P8        | 50um                   | Hydrophilic | 400°C                    |

| P9        | 50um                   | Hydrophilic | T amb                    |

cea

**EP-DT**

**Detector Technologies**

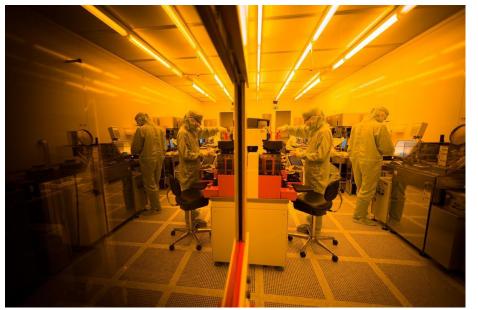

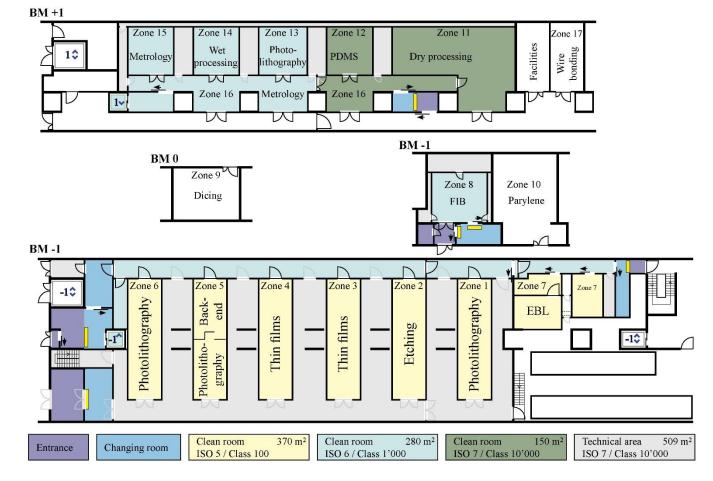

### Center of Micronanotechnology

- The Center of Micronanotechnology (CMi) is a ISO5-6-7 clean room complex at the École Polytechnique Federale de Lausanne

- CMi facilities are used for education, academic purposes and research

cea

**EP-DT**

ÉCOLE POLYTECHNIOUI

**Detector Technologies**

#### https://cmi.epfl.ch/

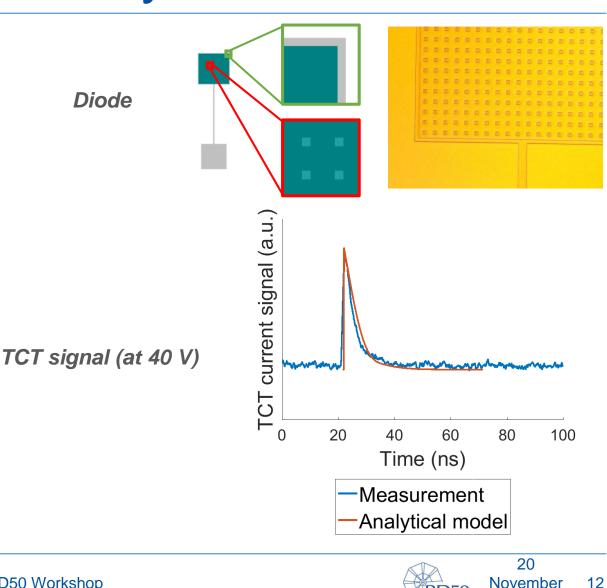

# Validation of TCT on Schottky diodes

- Tests performed on structures fabricated at CMi

- 4 inches wafers

- Resistivity > 2000 ohm.cm

- Float zone P-type

- Al for schottky contacts

- Pt for ohmic contacts

Next steps:

- Schottky diodes fabrication on bonded wafers

- TCT measurements on Schottky diodes on bonded wafers

Mi FPFL Center of

MicroNanoTechnology

2017

CMi: <u>https://cmi.epfl.ch/</u>

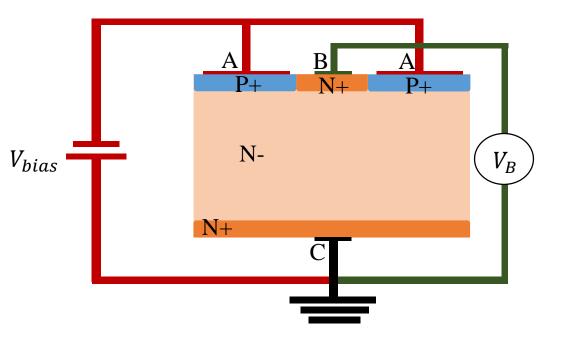

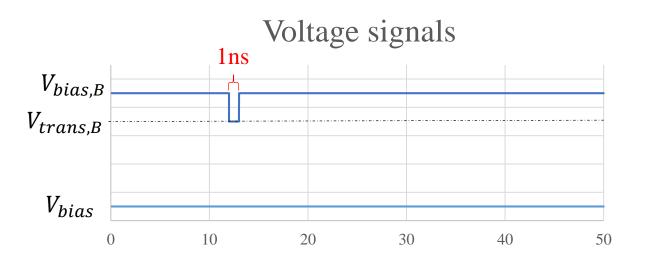

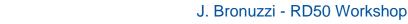

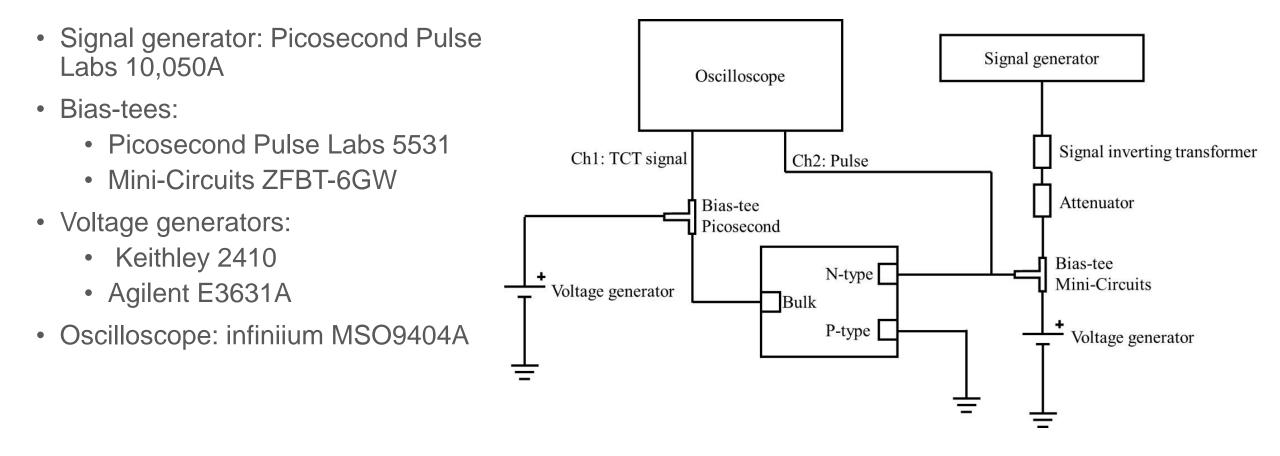

### **Electrical injection TCT**

- Instead of Schottky diodes, integrate TCT charge injection in silicon

- PiN Diode doping profile modified

- Nanosecond voltage pulse applied on the N-type well

20

November

2017

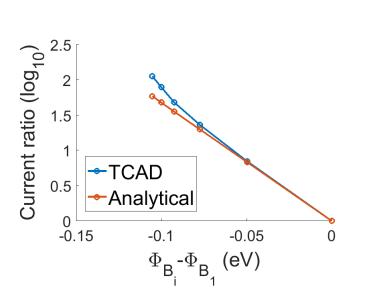

### Physical principle

Thermionic emission

$J_i/J_1 = e^{\frac{\phi_{B_1} - \phi_{B_i}}{kT}}$

cea

EP-DT

**Detector Technologies**

CERN)

ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

**RD50**

### Light and electrical injection

ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

ovember 15 2017

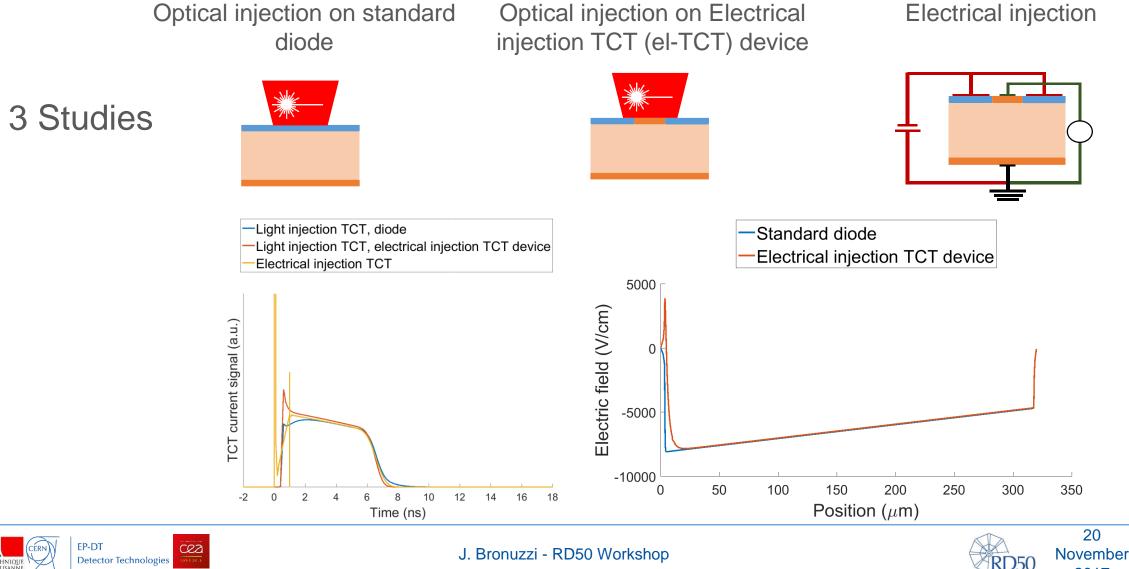

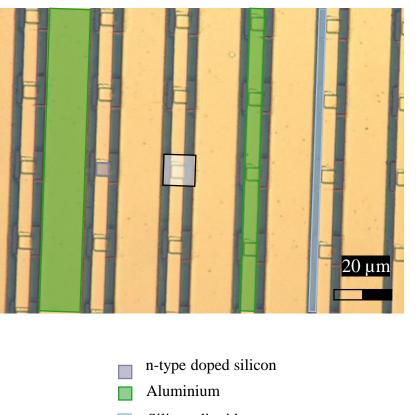

### Fabrication and measurements setup

Device fabricated at CMi

- Silicon dioxide

- ☐ Spacing between n and p-type doped silicon

## Setup components

### Proof of principle of el-TCT

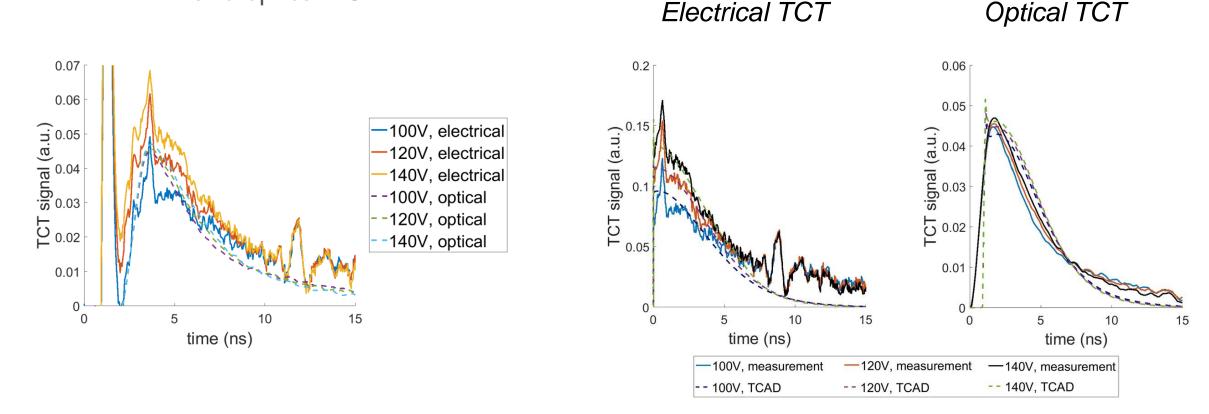

### Measurements: comparison electrical and optical TCT

Comparison TCAD simulations and measurements

20

November

2017

-250

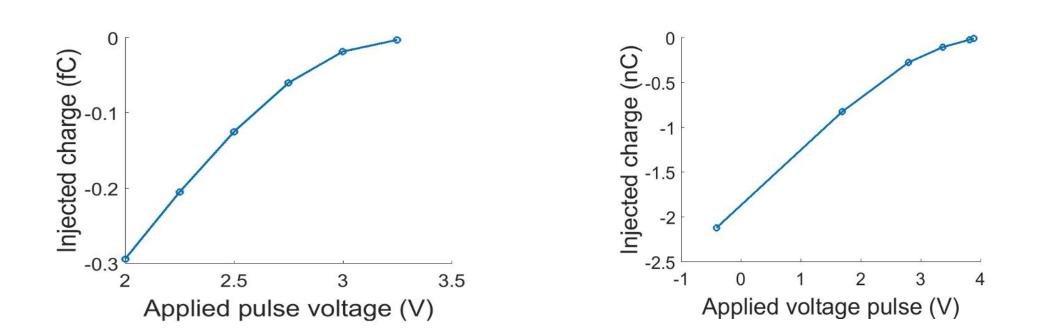

### Proof of principle of electrical TCT

TCAD simulations of injected charge

Measurements of injected charge

### **Conclusions and outlook**

New manufacturing technique for monolithic silicon sensors is being investigated:

- Characterization of bonding interface with TCT has been modeled

- Fabrication of devices for TCT bonding interface characterization is in progress

- Measurements will be performed at CERN in the early 2018

EI-TCT has been developed:

- The proof of principle has been demonstrated

- Evaluation of el-TCT for online measurements of radiation induced damage in silicon samples at IRRAD proton facility in 2018

# Thank you for the attention Questions?