#### Exceptional service in the national interest

#### FinFET technologies for Digital Systems with Radiation Requirements: TID, SEE, Basic Mechanisms, and Lessons Learns

#### Michael P. King

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

#### Motivation

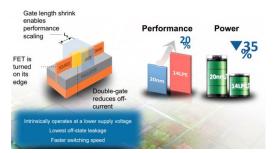

- Most commercial fabs have migrated to FinFETs below 20-nm gate length feature sizes

- FinFETs exhibit improved electrostatic control of the channel and improved reliability compared to equivalent scaled planar CMOS

- Some work on the TID response of FinFETs has been presented at IRPS, NSREC, and RADECs

T. Hook, FDSOI Conference, Taiwan, 2013

#### Outline

- Technology overview

- A very basic review of radiation effects in CMOS devices

- Total ionizing dose (TID) in 14/16-nm FinFET devices

- Single-event upset (SEU) in 14/16-nm FinFETs: data and discussion of mechanisms

- Observation of single-event latchup (SEL) in a 14/16-nm FPGA?

- Conclusions

## Current Technology Engagements

Sandia National Laboratories

- GlobalFoundries

- 14-nm FinFETs

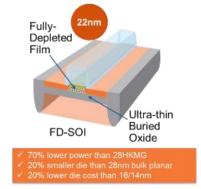

- 22-nm FDSOI

- NVM

- Optane / 3D CrossPoint

- IBM

- 32-nm PDSOI

- 22-nm PDSOI

- TSMC

- 16-nm FPGAs (Xilinx)

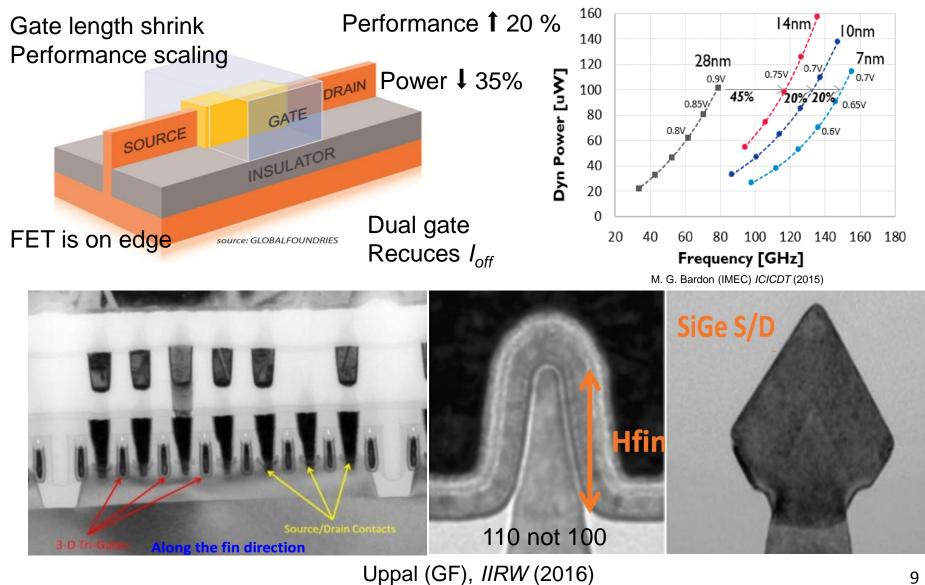

14nm FinFET Offers Breakthrough Power/ Performance

An Innovative, High-Density Design An Innovative, High-Density Design Cores Point Structure What is a structure of the structure Point of the structure of the structure Point of the structure of the structure Point of the structure of th

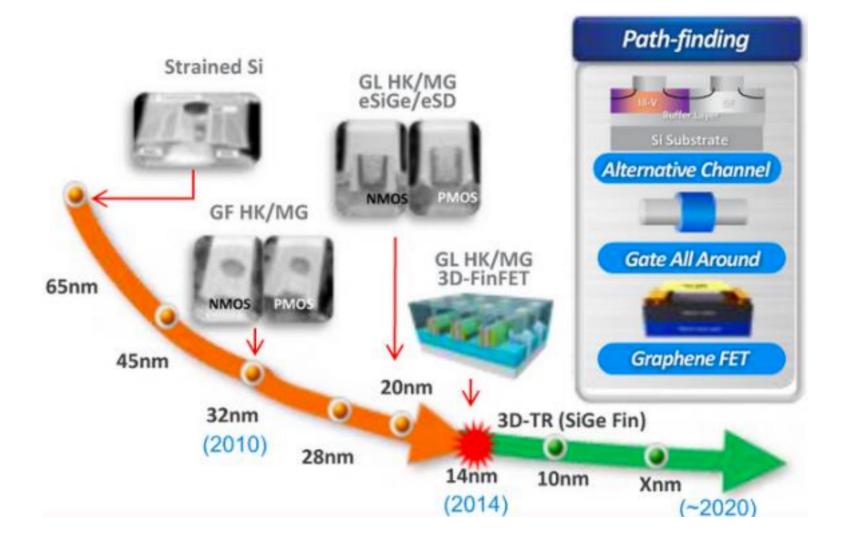

#### **TECHNOLOGY PROGRESSION**

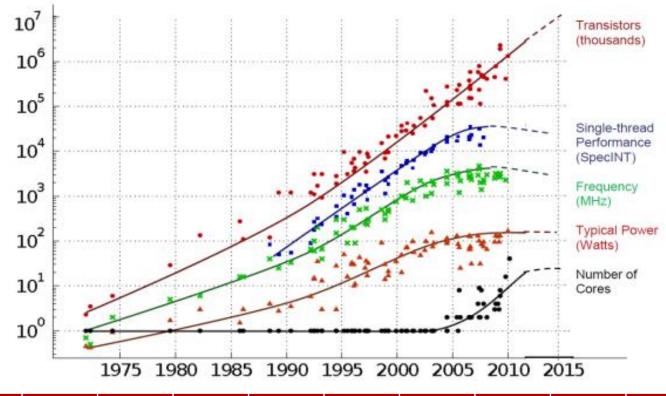

#### **Technology Scaling Trends**

| 1995 | 1997 | 1999 | 2001 | 2004 | 2006 | 2008 | 2010 | 2012 | 2014 |

|------|------|------|------|------|------|------|------|------|------|

| 350  | 250  | 180  | 130  | 90   | 65   | 45   | 32   | 22   | 14   |

| nm   |

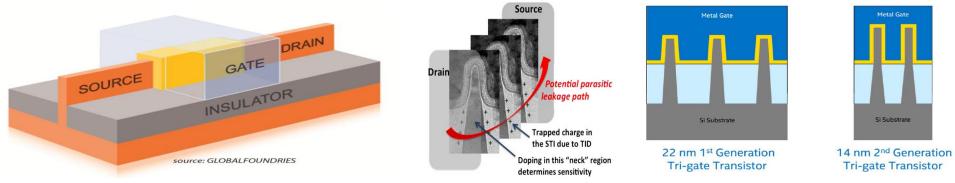

#### Path to FinFET Technology

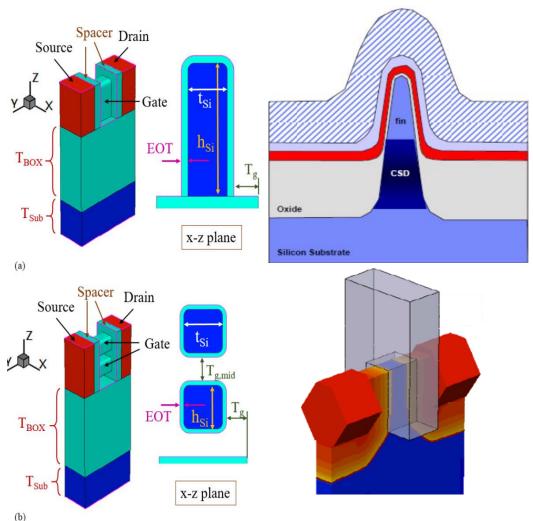

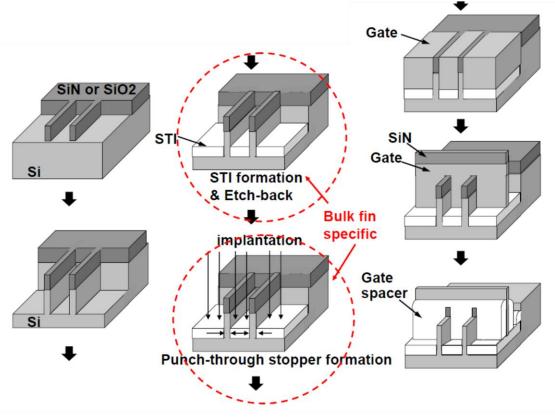

## Bulk FinFET Processing Technology

- Increasing processing complexity

- More challenging lithography

- Quad patterning

- Soon EUV

- Line edge roughness

- Isolation steps

- STI

- CSD/SSRW

A. Yagishita (Toshiba), SOI Short Course (2009)

## Advantages / Challenges

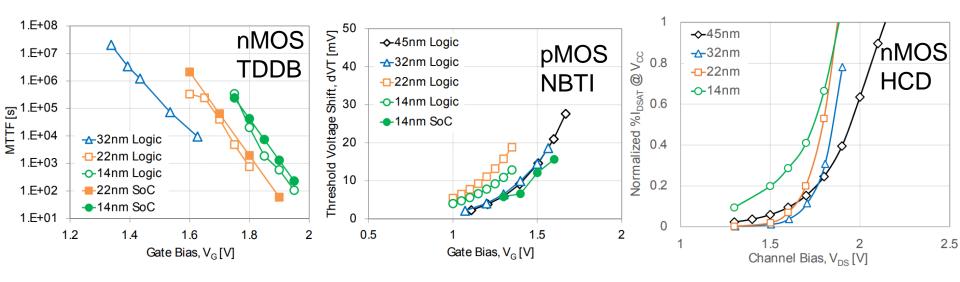

#### **Reliability Outlook**

- FinFET TDDB shows improvement over planar

- pMOS FinFET NBTI did show some regression; improved in second gen. overall BTI improved

- HCD does degrade some for FinFETs

#### RADIATION EFFECTS IN SEMICONDUCTORS

Brief review

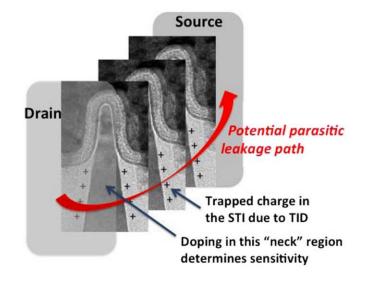

#### **Total Ionizing Dose Degradation Mechanisms**

- Shifts in threshold voltage changes drive current in on-state

- Increased leakage current at STI sidewalls causes higher power dissipation

- Timing / switching mismatch for digital systems

- Traditionally preferential impact on nMOSFETs

#### Chatterjee, IEEE TNS, 2013.

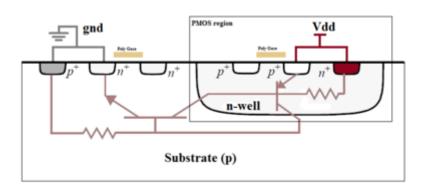

## Single Event Latchup (SEL)

#### Why do we care?

- Well it requires a powerdown event to quench

- Can be destructive if not handled quickly

- Parts that exhibit such behavior are *high risk*

- A high current state sustained by a positive feedback loop in a n-pn-p junction resulting from charge injection in cross-coupled bipolar junction transistor

- Similar to electrical latchup except initiated by a charged particle interaction

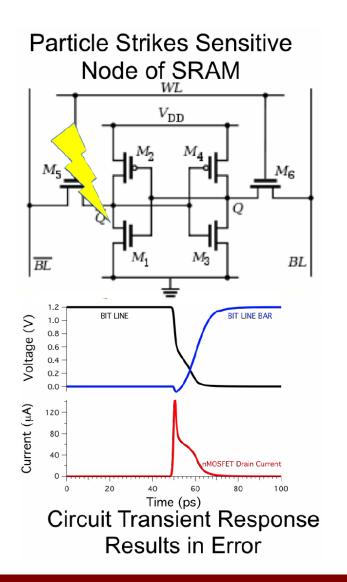

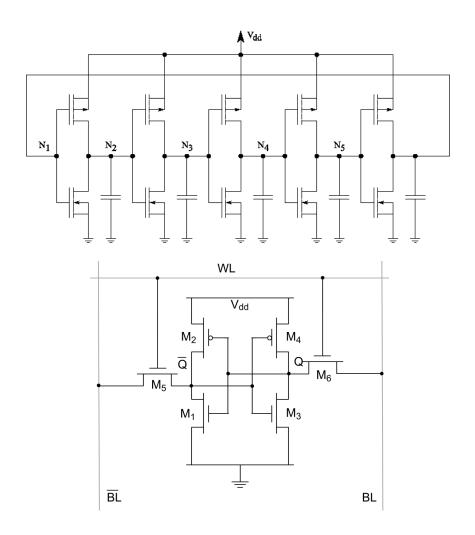

#### Single Event Upset (SEU)

- A possible circuit response to a charged particle interacting in specific regions of a memory (SRAM depicted) leading to an erroneous data state

- Problem because of data integrity and fault propagation up to the system level

And now for some data...

#### RESULTS

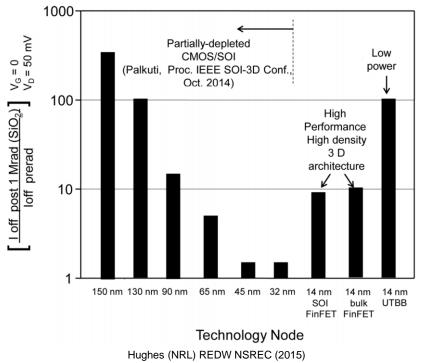

#### **TID vs Technology Scaling**

- Scaling trends of off-state leakage vs technology node

- PDSOI exhibits very low leakage for 45- and 32-nm at 1 Mrad

- Migration to FinFETs resulted in a dramatic increase in postirradiation leakage (early look)

- FDSOI shows leakage comparable to older technologies

#### **Description of Test Structures**

- Single logic and IO transistors in all V<sub>th</sub> flavors

- Special Structures

- Ring oscillator (RO) (RF) transistors

- Static random access memory (SRAM) transistors

#### **Experimental Methods**

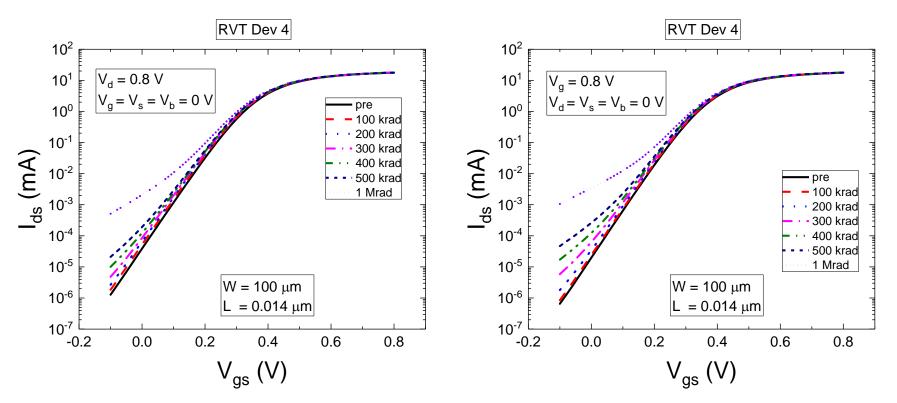

- Information extracted from I<sub>ds</sub>-V<sub>gs</sub> curves

- *V<sub>th</sub>* linear region approximation

- $g_m = dI_{ds}/dV_{gs}$

- $I_{ds,on} = I_{ds} @ V_{gs} = 0.9 V, V_{ds} = 50 mV$

- $I_{ds,off} = I_{ds} @ V_{gs} = 0 V, V_{ds} = 50 mV$

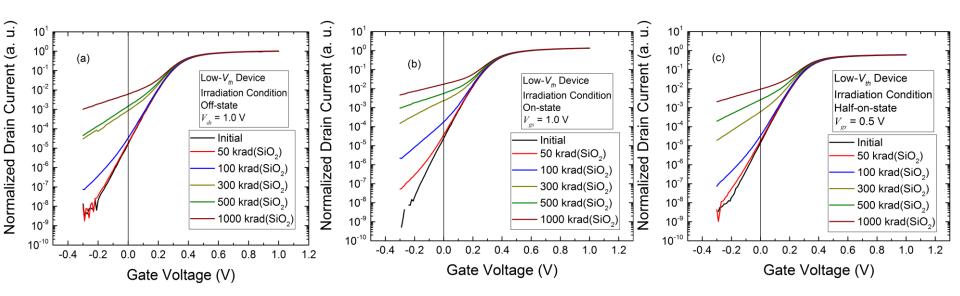

- Bias Conditions

- Off-state:  $V_d = 1.0 \text{ V}$ ,  $V_g = V_s = V_b = 0 \text{ V}$

- On-state:  $V_g = 1.0 \text{ V}$ ,  $V_d = V_s = V_b = 0 \text{ V}$

- Half-on-state:  $V_g = 0.5 \text{ V}$ ,  $V_d = V_s = V_b = 0 \text{ V}$

- Devices irradiated at 525 rad(SiO<sub>2</sub>)/s

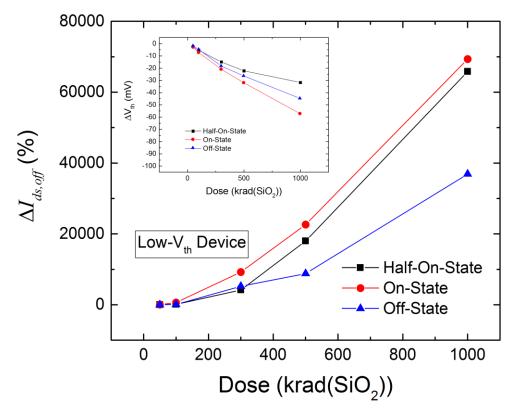

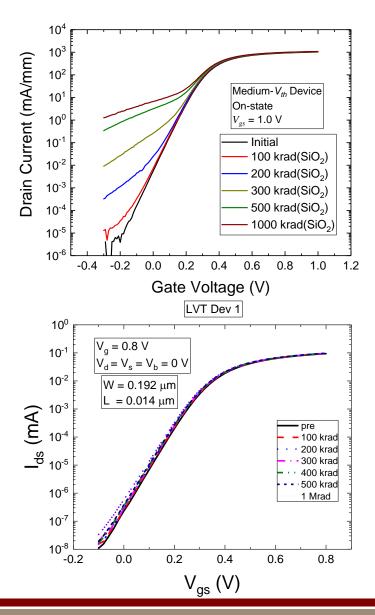

#### Low-V<sub>th</sub> Device Bias Dependence

- Large changes in I<sub>ds,off</sub>

- Gate-controlled leakage component

- On-state condition gives largest degradation

- Minimal change in V<sub>th</sub>

Sandia

National

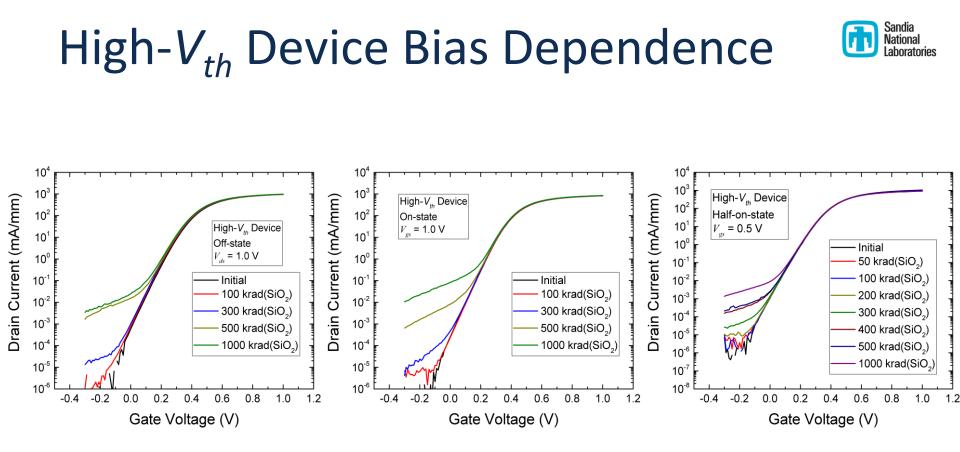

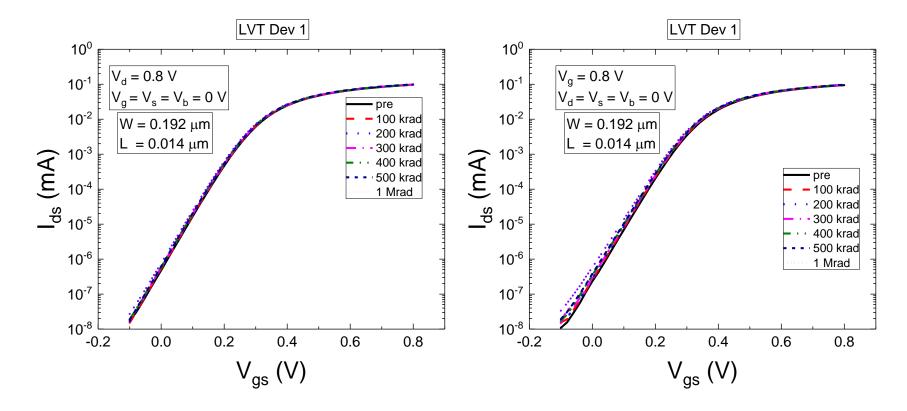

## **TID Irradiation Bias Dependence**

- \[

\Lap{AI\_{ds,off}} shows most

degradation for on state condition

\]

- \Delta V<sub>th</sub> fairly similar for all bias conditions (and small)

- Lower operating voltage (half-on-state) shows marginal improvement in  $\Delta I_{ds,off}$  and  $\Delta V_{th}$ compared to full onstate

- Less off-state leakage compared to low-V<sub>th</sub> device

- Reduced operating voltage has a greater impact on TID degradation for higher V<sub>th</sub>device

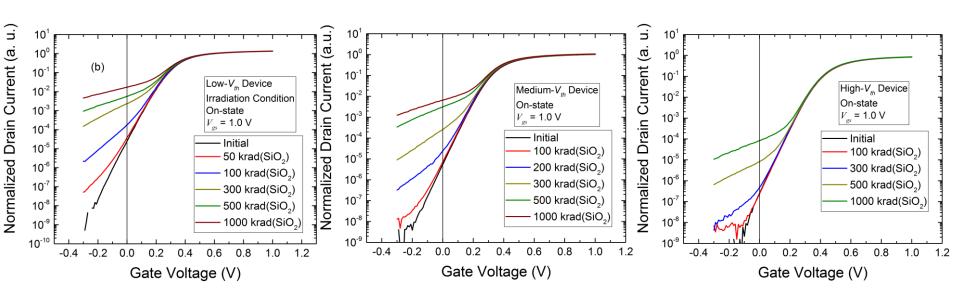

## Different $V_{th}$ Devices – On-State

- Increasing V<sub>th</sub> shows less I<sub>ds,off</sub> degradation for equivalent dose

- Process level decisions will clearly impact TID impact on devices, circuits, and ICs

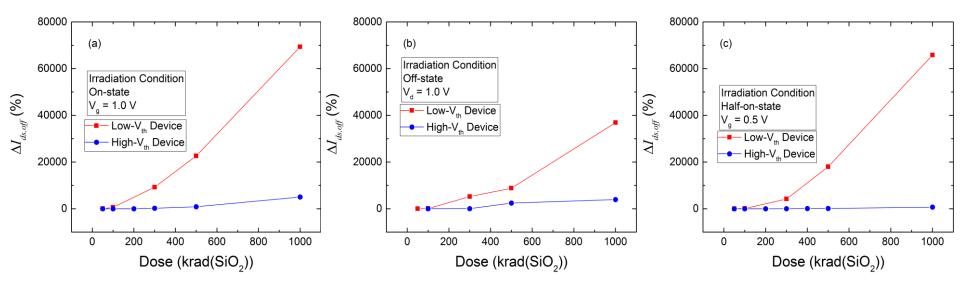

# Comparison of TID Variability for Different $V_{th}$

- High-V<sub>th</sub> device shows less ΔI<sub>ds,off</sub> compared to Low-V<sub>th</sub> devices

- On-state appears to be the worst case for device leakage response

Sandia National

#### A Tale of Two Commercial Processes

Typically comes about when they fix a leakage problem

Sandia

National

Impossible to say if TID resilience remains a permanent feature of the technology going forward

Two snapshots of a commercial 14/16-nm FinFET technology show *very* different TID results

#### Narrow width nFET

- Device shows more leakage in the on-state consistent with previous experimental results

- Response to TID is much less severe than original observations

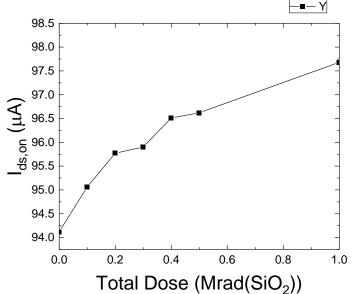

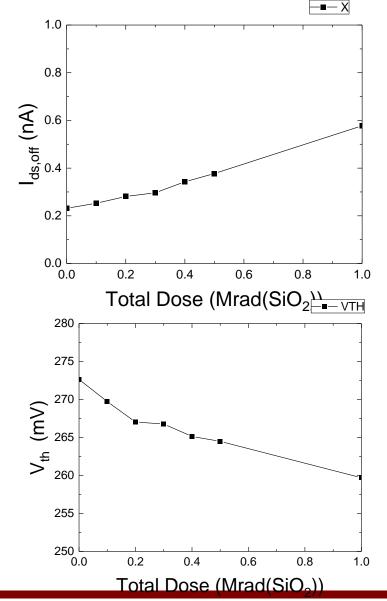

## Change in irradiated leakage and V<sub>t</sub>

- Drive current tracks V<sub>th</sub> with irradiation

- Leakage current shift smaller than previous evaluations

- Results not consistent

between foundries! recent

VU paper at NSREC

Sandia

National Laboratories

#### Not all is well in the land of Oz

Sandia

National Laboratories

- Largest device shows much more leakage than either of previous two devices

- May be some dependence on total width/number of fingers

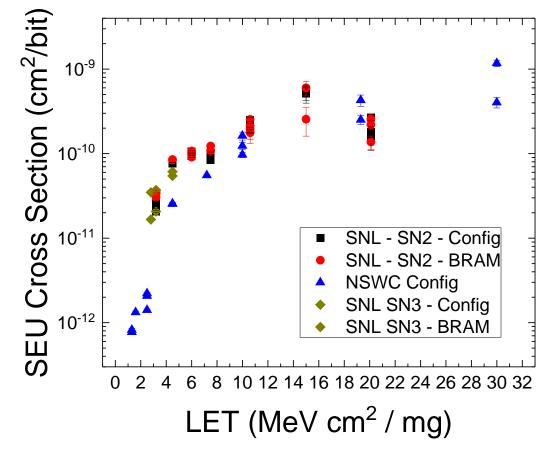

#### Xilinx UltraScale+ (16-nm) FPGA - SEU

- Parts exhibit a fairly low SEU cross section

- For some environments 3D geometry effectively lowers expected error rates even with higher bit density

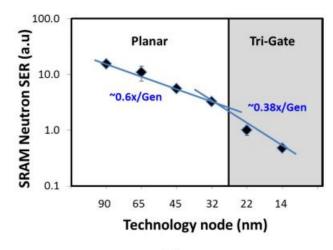

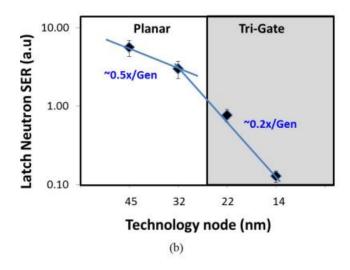

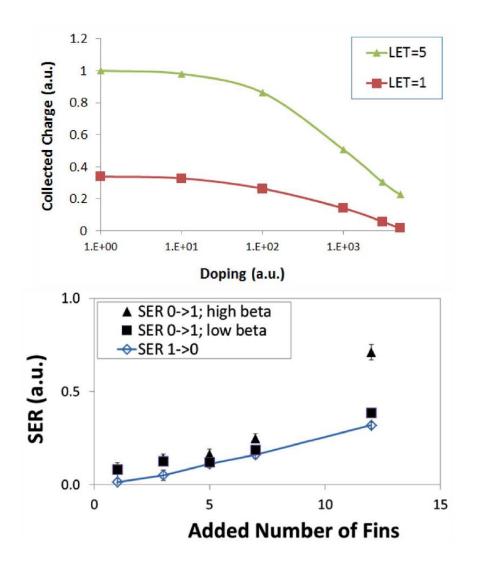

#### Early Neutron SER Report

- Industry looks at SER from alphas, muons, and neutrons for terrestrial environment reliability

- Several reports of reduced

SER from geometry change

in FinFET vs planar

- No reports of destructive effects due to neutrons to 10<sup>9</sup> n/cm<sup>2</sup> from Broadcom or Intel

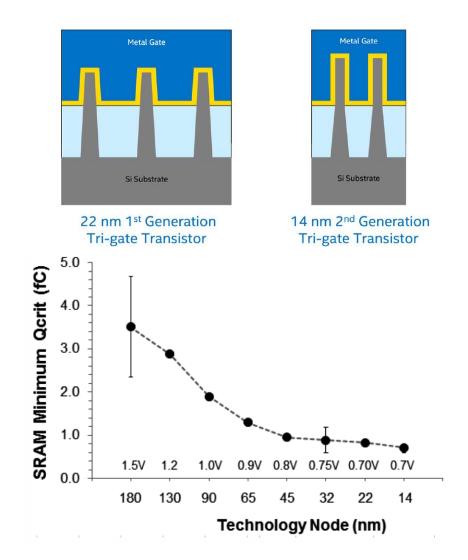

#### Mechanisms of SEU in FinFETs

- 3D geometry allows increasing drive without increase in Drain-Body/Well area

- Most charge is collected from subfin/well region this implies a higher

Q<sub>crit</sub> without impacting the sensitive volume dimensions

#### Additional SEU Mechanisms

- SER/SEU response ultimately will depend on things beyond our control

- Channel stop doping

- Well doping

- Some control from layout and memory architecture

- Effective transistor width

- Spatial separation of critical nodes

- DICE vs regular latch

Sandia

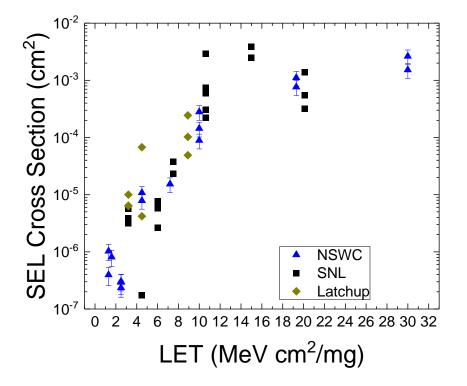

#### Xilinx UltraScale+ (16-nm) FPGA – "SEL" The Sandia Sandia

- Parts exhibit SEL-like behavior at relatively low LET

- Unclear if this is a circuit design issue or actual latchup

- There are reports of SEL in 14/16-nm that exhibit the correct temperature dependence but *none* have such low threshold LET

#### Conclusions

- On-state bias condition appears to be the worst case for I<sub>ds,off</sub> for all the transistor variations evaluated in this work

- More recent studies indicate TID may be less of an issue, however, some big questions still remain

- SEU shows some benefit for terrestrial environments even with higher memory density error rates can decrease

- Several design parameters can lead to lower TID impact and SEU rates

- We saw "SEL" and were not happy about it