# CT-PPS Experience during Intensity Ramp-Up; Recent Auto-Retraction

**Mario Deile**

MPP Meeting

22 September 2017

### **Intensity Ramp-Up**

- Up to the highest LHC luminosity:  $L = 1.6 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$

- 2 ramp-up periods: before and after TS1

- without any problems (except 1 interlock problem  $\rightarrow$  later)

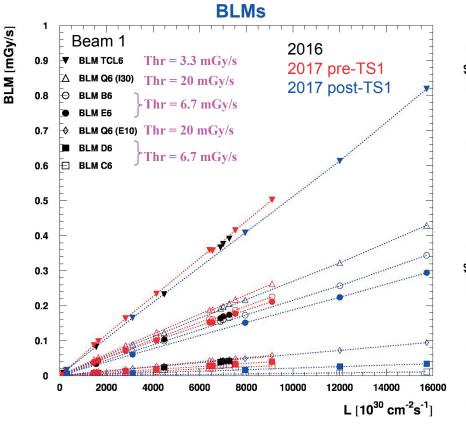

- BLM signals in line with 2016 (at least factor 3 below thresholds)

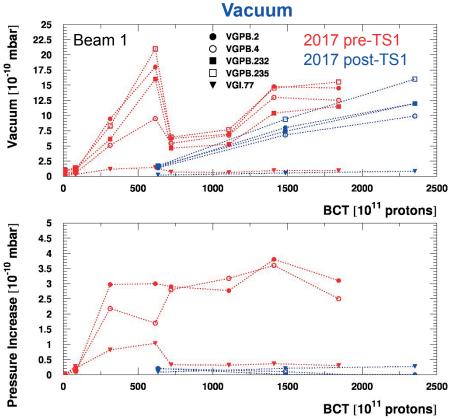

- very good vacuum levels

- benign temperatures

- no impedance problems

TOTEM

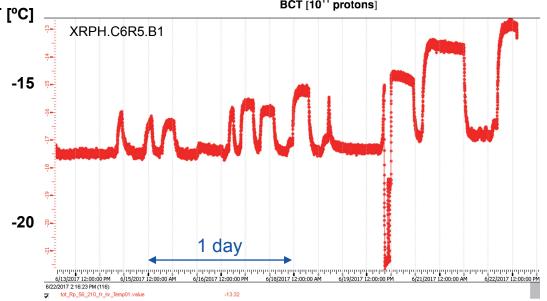

Vacuum dominated by other systematics, not primarily by beam current.

## **Intensity Ramp-Up (2)**

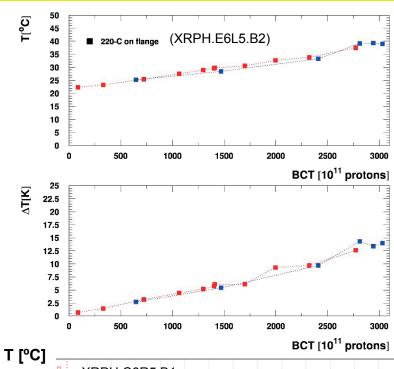

#### **Temperature vs. Beam Current:**

on XRP flange (not directly cooled)

on detector hybrid (cooled)

TOTEM

# Interlock Problem and FPGA Firmware Modifications during TS1

TOTEM

24 June: spurious dump by movement interlock, TIMBER logging time resolution not fine enough → no malfunction found

→ Implementation of an LVDT filter and a post-mortem diagnostic system

(see MPP 07.07.2017)

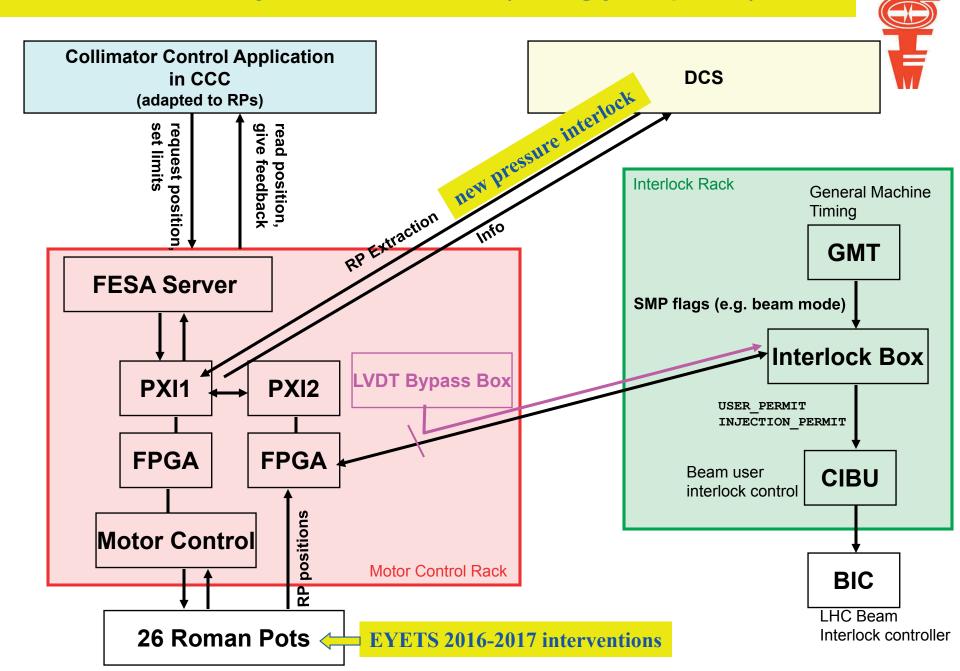

#### PXI for motor control:

- RS485 communication with motor encoder,

- DIM communication to DCS and CCC,

- Resolver measurement and calculation,

- Motor control.

- ➤ No modification for this part during TS1

## OPCUA Data exchange:

- Limits for interlocks

- LVDT Positions

#### PXI for RP position:

- LVDT measurement and calculation,

- Interlock generation according to Warning, Critical or Inner limits.

#### Modifications implemented during TS1:

- > Real time part (1):

- ➤ Generation of a post mortem file <u>after an</u> <u>interlock generation</u> (1s before and 1s after).

- > FPGA part (2):

- ➤ Interlock Generation if conditions are valid during three consecutive loop iterations of 10 ms each (same as AFP and ALFA)

i.e. only if the dump threshold was crossed! Crossing the warning threshold does not trigger a post-mortem file. **To be improved.**

### **Observations after the FPGA Modifications**

No post-mortem file was ever generated.

Dump threshold was never crossed since TS1.

#### But:

11 Sept., 17:51 h: Spring extraction of all XRPs during Stable Beams without apparent reason,

- no interlock

- no suspicious LVDT activity in TIMBER

- no post-mortem file generated (i.e. dump threshold was not crossed)

- also: crossing the warning limit extracts ONLY the violating pot

- → last conceivable option: signal glitch somewhere (e.g. STABLE\_BEAM flag to interlock box)

Future improvement (Christmas shutdown):

- generate a post-mortem file already at a crossing of the warning limit

- think about additional loggings (e.g. SMP flags received)

### **Restart after TS2**

- Alignment of all operational XRPs due to optics change and TS2 interventions: **done**

- Calibration data at 3 crossing-angles: 150, 130, 110 μrad: ongoing

- New physics settings: TCT + 3  $\sigma$  + 0.3 mm = 11.5  $\sigma$  + 0.3 mm

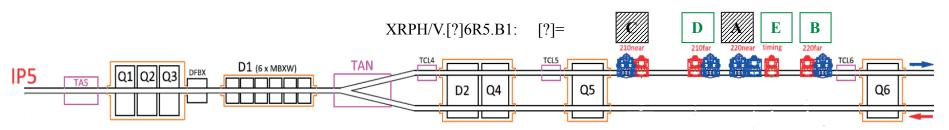

#### **Horizontal**:

- C units: empty, unused for the full year

- D units: used in all fills

- A units: empty, unused for the full year

- E units: used in all fills

- B units: used in all fills

#### Vertical:

- D and B units inserted in calibration runs,

- A and C units empty, unused.

#### Hardware groups (since TS1, unchanged):

- 1 global group and sequence with all pots used in normal fills (horizontal D, E, B)

- 3 subgroups with related sequences for flexibility (detector problems / limit irradiation): COLLIMATORS\_XRP\_TOTEM\_LOWBETA\_B / D / E

# **Additional Material**

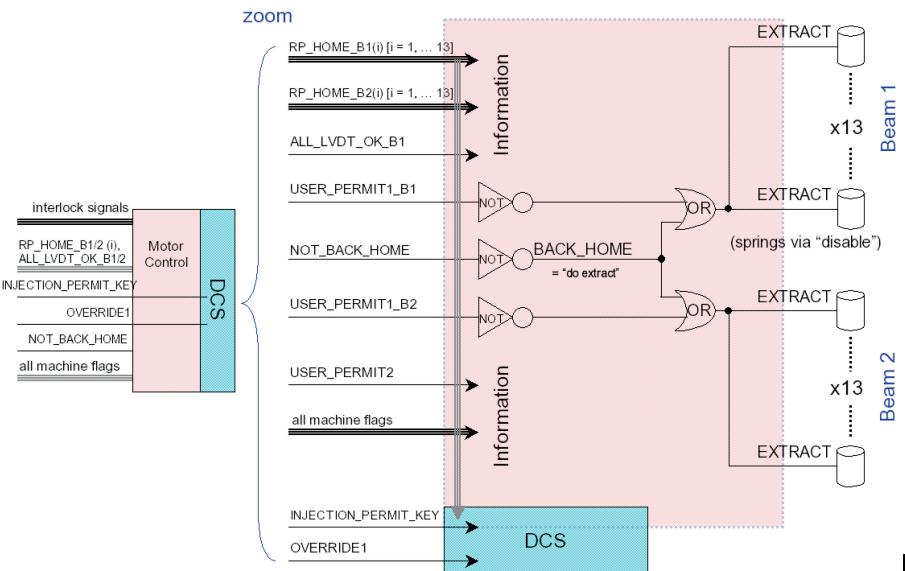

### **Movement System Architecture (strongly simplified)**

TOTEM

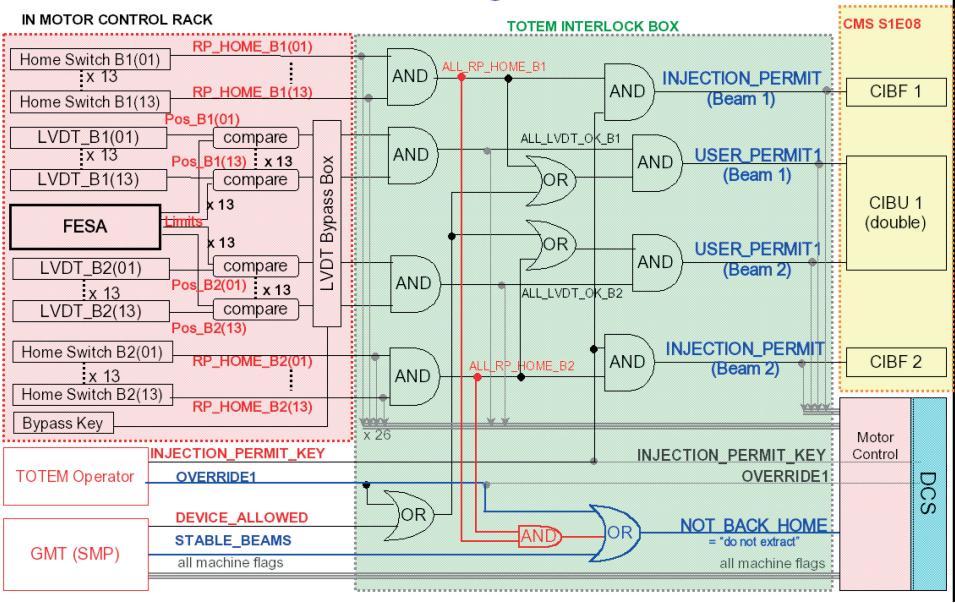

### **Interlock Logic 2015**

# Interlock Logic 2015 (Zoom on the motor control)