## Beam-tests of prototype modules for the CMS High Granularity Calorimeter at CERN PIXEL2018: International Workshop on Semiconductor Pixel Detectors for Particles and Imaging 2018

Arnaud Steen On behalf of the CMS collaboration

10-14 December 2018

### Outline

Motivation for upgrade

2 HGCAL prototype

Preliminary results

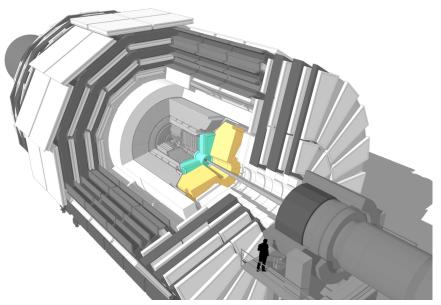

## CMS will replace its endcap calorimeters in 2024-25

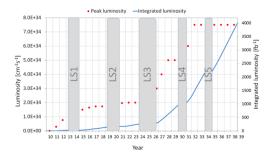

## High luminosity LHC

### High lumi LHC

- Luminosity :  $5 \times 10^{34} \ cm^{-2} s^{-1}$

- Integrated luminosity : 3000 fb<sup>-1</sup>

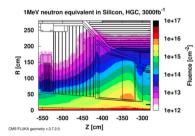

- Fluences : up to  $10^{16} neq/cm^2$  in ECAL endcap

- Average pileup : 140 (maximum of 200)

#### Need to replace endcap calorimeters

- Radiation tolerant

- Good timing resolution (pileup mitigation)

- Tracking capability (shower reconstruction, PFA)

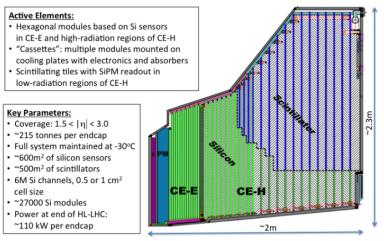

# CMS High Granular Calorimeter (HGCAL)

Electromagnetic calorimeter (CE-E): Si, Cu & CuW & Pb absorbers, 28 layers, 25 X<sub>0</sub> & ~1.3 $\lambda$  Hadronic calorimeter (CE-H): Si & scintillator, steel absorbers, 24 layers, ~8.5 $\lambda$

• More details about HGCAL project in Chia-Hung Chien's poster : The CMS High Granularity Calorimeter for HL-LHC

Arnaud Steen, NTU

## Overview and goals of the beam tests

### Main goals

- Validation of basic design of the HGCAL

- Comparisons with GEANT4 simulation

- Test calorimetric performance of silicon based calorimeter

#### 2016 beam tests

- Timing study with irradiated silicon diodes at CERN

- Electromagnetic calorimeter prototype using 6" modules and SKIROC2 ASIC (designed for CALICE SiWECal) at FNAL and CERN

### 2017/2018 beam tests

- New 6" modules using SKIROC2\_CMS ASIC (with time over threshold and time of arrival measurements)

- Various configurations tested at CERN with up to 20 modules in 2017

- Beam test at DESY (March/April 2018) with few modules

- Larger scale beam tests :

- CE-E prototype with 28 modules at CERN (June 2018)

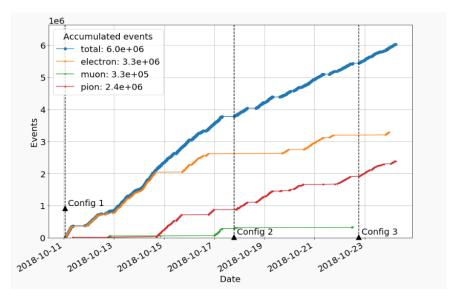

- Prototype with 94 silicon modules + the CALICE Analog Hadronic CALorimeter prototype (sampling calorimeter using scintillator tiles as active medium) at CERN (October 2018)

### Results from 2016 beam tests

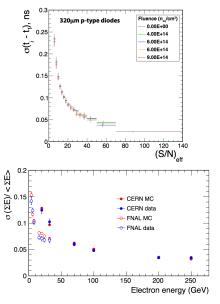

- Precision timing study with irradiated silicon diodes

- Electromagnetic calorimeter prototype using 6" modules and SKIROC2 chip (designed for CALICE SIWECal)

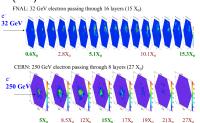

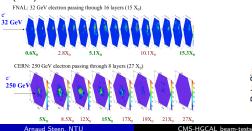

- ► FNAL beam test : 16 modules with total thickness  $\approx 15X_0$

- ▶ CERN beam test : 8 modules, with total thickness  $\approx 27X_0$

- Beam tests results in this paper :

N. Akchurin et al. First beam tests of prototype silicon modules for the CMS High Granularity Endcap Calorimeter (link)

### **Results from 2016 beam tests**

- Precision timing study with irradiated silicon diodes

- Electromagnetic calorimeter prototype using 6" modules and SKIROC2 chip (designed for CALICE SIWECal)

- FNAL beam test : 16 modules with total thickness  $\approx 15X_0$

- ▶ CERN beam test : 8 modules, with total thickness  $\approx 27X_0$

- Beam tests results in this paper :

N. Akchurin et al. First beam tests of prototype silicon modules for the CMS High Granularity Endcap Calorimeter (link)

1 Motivation for upgrade

BIGCAL prototype

3 Preliminary results

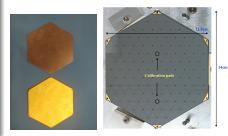

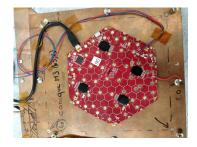

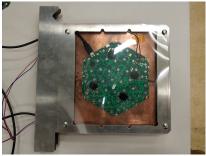

## Module assembly

#### Glued stack

- Baseplate (CuW for CE-E, Cu for CE-H), thickness : 1.2 mm

- Kapton foil with gold layer

- 6" silicon sensor from HPK

- PCB holding 4 SKIROC2\_CMS readout chips (32 channels per chip are connected to a silicon pads)

- Silicon pads wire bonded through holes in the PCB

#### Silicon sensors

- 6" hexagonal sensor

- Physical thickness : 320  $\mu m$

- Depleted thickness : 300 μm (4 modules with 200 μm)

- 134 individual silicon cells with an area of  $\approx 1.1 cm^2$  for the full cells

- 2 inner calibration pads with 1/9th of the area of the full cell (for MIP sensitivity after irradiation)

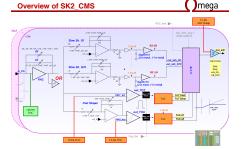

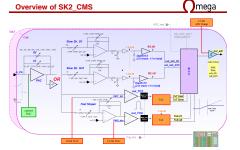

## Readout CHIP : SKIROC2\_CMS

- Derived from CALICE SKIROC2 chip

- 64 channels (though 32 are connected to a silicon pad)

- 2 slow shapers (shaping time between 10 and 70 ns) per channel with

- a 13-deep 40 MHz analog memory used as waveform sampler

- 12-bit ADC

- Fast shaper (shaping time between 2 and 5 ns) and discriminators for

- Time over threshold to measure large signal (preamplifier saturation region)

- Time of arrival (50 ps timing resolution foreseen)

- More details in this paper : J. Borg et al. SKIROC2\_CMS an ASIC for testing CMS HGCAL

## Readout CHIP : SKIROC2\_CMS

- Derived from CALICE SKIROC2 chip

- 64 channels (though 32 are connected to a silicon pad)

- 2 slow shapers (shaping time between 10 and 70 ns) per channel with

- a 13-deep 40 MHz analog memory used as waveform sampler

- 12-bit ADC

- Fast shaper (shaping time between 2 and 5 ns) and discriminators for

- Time over threshold to measure large signal (preamplifier saturation region)

- Time of arrival (50 ps timing resolution foreseen)

- More details in this paper : J. Borg et al. SKIROC2\_CMS an ASIC for testing CMS HGCAL

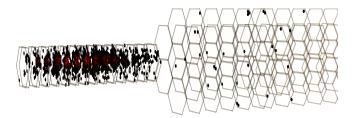

## **CE-E** prototype

#### Mini cassette

- 4 mm thick lead absorber plate

- 6 mm thick copper cooling plate holding 2 modules on its 2 faces

- Copper cooling pipe inside the copper plate

- Aluminium frame and mylar foil

#### ECAL prototype

- 14 mini cassetes (i.e. 28 silicon modules)

- Total depth :  $\approx$ 24  $X_0$ ,  $1\lambda_I$

- Water cooling to keep constant temperature : 28° C

## **CE-H** prototype

### CE-H layer

- 6 mm thick copper cooling plate holding 7 modules (only on front face)

- Copper cooling pipe glued to the backside of the copper plate

#### CE-H (silicon part) prototype

- 12 layers (9 with 7 modules + 3 with 1 module), 12k electronic channels in total

- Separated by 4 cm thick steel absorber plates

- Total depth :  $\approx 3.5 \lambda_I$

- Water cooling to keep constant temperature :  $28^{\circ}C$

#### CALICE AHCAL prototype

- 38 layers using scintillator tiles (tile size :  $3 \times 3 cm^2$ )

- pprox 22k channels

- Separated by 1.75 cm thick steel absorber plates

- Total depth :  $\approx 4\lambda_I$

## **DAQ** systems

#### Extra detectors in the beam line :

- $\bullet\,$  2 scintillators in coincidence for the trigger  $+\,$  1 veto scintillator between HGCAL and AHCAL prototypes to reject pion in electron run

- 4 delay wire chambers readout with TDC

- 2 MCP detectors for timing reference readout with 5 GHz digitizer

#### Custom DAQ boards

- SYNCH board (1 synch board in total)

- board creates 40 MHz clock

- receives and distributes triggers to RDOUT boards, AHCAL, TDC and digitizer

- RDOUT boards connected to up to 8 modules

- distribute low and bias voltage to the modules

- send commands to the MAX10 FPGA on the modules (trigger, slow control)

- read out the data using IPbus protocol

#### DAQ software

- eudaq framework https://eudaq.github.io/

- Collects data from each detector types

- Provides DQM framework

### Beam test summary

1 Motivation for upgrade

2 HGCAL prototype

#### O Preliminary results

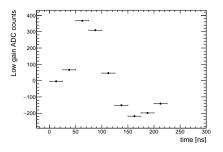

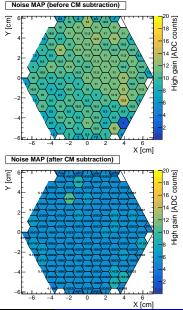

- Pedestal estimation and subtraction for each channel and each memory slot (13-deep 40 MHz analog memory)

- Common mode noise estimation for each module and each time sample

- Pulse shape fit to extract high and low gain amplitudes, after hit pre-selection

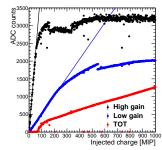

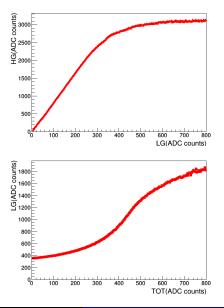

- Gain choice between high gain, low gain and ToT and hit energy calibration

- High gain calibrated using muon runs

- ▶ 1 MIP  $\approx$  40-50 ADC counts (high gain), S/N $\approx$ 6-7 for MIP

- Low gain calibrated using high gain

- ToT calibrated using low gain

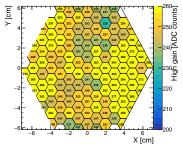

Pedestal MAP

- Pedestal estimation and subtraction for each channel and each memory slot (13-deep 40 MHz analog memory)

- Common mode noise estimation for each module and each time sample

- Pulse shape fit to extract high and low gain amplitudes, after hit pre-selection

- Gain choice between high gain, low gain and ToT and hit energy calibration

- High gain calibrated using muon runs

- ▶ 1 MIP  $\approx$  40-50 ADC counts (high gain), S/N≈6-7 for MIP

- Low gain calibrated using high gain

- ToT calibrated using low gain

- Pedestal estimation and subtraction for each channel and each memory slot (13-deep 40 MHz analog memory)

- Common mode noise estimation for each module and each time sample

- Pulse shape fit to extract high and low gain amplitudes, after hit pre-selection

- Gain choice between high gain, low gain and ToT and hit energy calibration

- High gain calibrated using muon runs

- ▶ 1 MIP  $\approx$  40-50 ADC counts (high gain), S/N $\approx$ 6-7 for MIP

- Low gain calibrated using high gain

- ToT calibrated using low gain

- Pedestal estimation and subtraction for each channel and each memory slot (13-deep 40 MHz analog memory)

- Common mode noise estimation for each module and each time sample

- Pulse shape fit to extract high and low gain amplitudes, after hit pre-selection

- Gain choice between high gain, low gain and ToT and hit energy calibration

- High gain calibrated using muon runs

- ▶ 1 MIP  $\approx$  40-50 ADC counts (high gain), S/N $\approx$ 6-7 for MIP

- Low gain calibrated using high gain

- ToT calibrated using low gain

HGCAL prototype

- Pedestal estimation and subtraction for each channel and each memory slot (13-deep 40 MHz analog memory)

- Common mode noise estimation for each module and each time sample

- Pulse shape fit to extract high and low gain amplitudes, after hit pre-selection

- Gain choice between high gain, low gain and ToT and hit energy calibration

- High gain calibrated using muon runs

- ▶ 1 MIP  $\approx$  40-50 ADC counts (high gain), S/N≈6-7 for MIP

- Low gain calibrated using high gain

- ToT calibrated using low gain

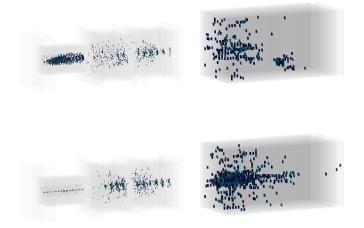

## Event displays : 300 GeV EM showers

# Event displays : 300 GeV hadronic showers

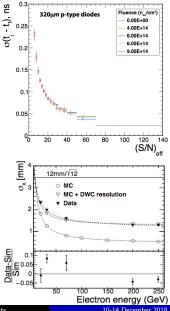

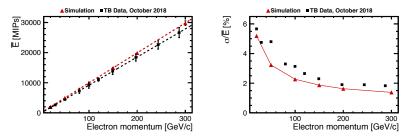

### **Electromagnetic shower results**

- Energy sum from all layers (only CE-E prototype i.e. 28 modules)

- Beam energy corrected to take into account synchrotron radiation

- Simulation being tuned with momentum spread from SPS

- Next steps :

- Improve hit calibration

- Apply weights for each layers

### Conclusion

- $\bullet\,$  New HGCAL prototype has been built with 94 silicon modules ( $\approx\,$  12k channels) between 2017 and 2018

- Combined data taking with AHCAL prototype, delay wire chambers and MCP has been a success

- Good preliminary results

- Low noise

- Good S/N for MIP

- Reasonable data-simulation agreement

- Energy and time resolution close to expectations

- Next plan for the data analysis :

- Improve the calibration

- Compare data and simulation

- Apply clustering technique

- Combine HGCAL data with AHCAL for hadronic shower study

- Time precision study using MCP detectors

# Back-Up

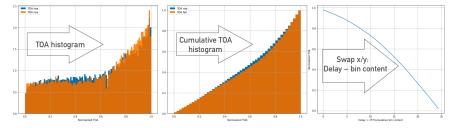

# Calibration of ToA

#### ToA signal

- Using electron runs from June data

- ToA threshold :  $\approx 10$  MIPs

- ToA measure time between ToA trigger and next falling/rising edge (but skiping first edge) of the 40 MHz clock

#### ToA calibration

- Beam is asynchronous → Time distribution expected to be uniform

- ToA range = 25 ns (with 12.5 ns offset)

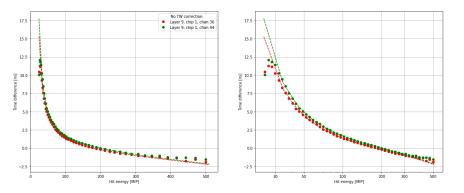

### Time walk correction

- Time walk can be large for low signal amplitude

- Time walk correction :

- Select a reference channel (and small amplitude window to minimize TW effect)

- Look at time diffence with neighbouring cells to extract the time-walk

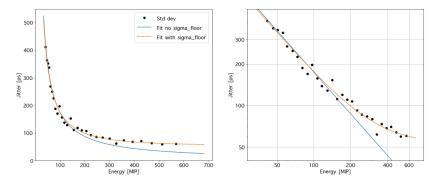

### **Time resolution**

• Time differences between 2 silicon pads

- ▶ Assume same time resolution in each cell  $\rightarrow \sigma_t = \sigma_{\Delta_t}/\sqrt{2}$

- ▶ Time resolution constant term  $\approx$  50 ps

• Next step : use MCP data for the time reference