# **LINAC4 Quadrupole Power Converters**

**TE-EPC** J.M. CRAVERO

06.10.2009

# Requirements

### • Requirements summary

|                  | application               | DTL-CCDTL-PIMS | DTL-CCDTL-PIMS | PSB - TL       |  |  |  |

|------------------|---------------------------|----------------|----------------|----------------|--|--|--|

| magnet           | magnet number (serial)    | 1              | 2              |                |  |  |  |

|                  | maximum operating current | 100 A          | 100 A          |                |  |  |  |

|                  | inductance                | 10.8 mH        | 21.6 mH        |                |  |  |  |

|                  | resistance                | 0.38 Ω         | 0.76 Ω         |                |  |  |  |

| cable<br>+filter | inductance                | 0.12 mH        | 0.18 mH        | 0.09 mH        |  |  |  |

|                  | resistance                | 0.5 Ω          | 0.6 Ω          | 0.35 Ω         |  |  |  |

| power converter  | power converter type      | Maxidiscap III | Maxidiscap III | Maxidiscap III |  |  |  |

|                  | precision during flat-top | ~1000 ppm      | ~1000 ppm      | ~1000 ppm      |  |  |  |

|                  | operating voltage         | 600 V          | 900 V          |                |  |  |  |

|                  | flat top duration         | 2 ms           | 2 ms           | 1 ms           |  |  |  |

|                  | repetition rate           | 2 Hz           | 2 Hz           | 1.1 Hz         |  |  |  |

|                  | quantity (workpackage)    | 23             | 0              | 16             |  |  |  |

- PSB-TL quads parameters are under study

- DC cabling has been considered but the cable definition is not done

- an output filter has been added to suppress overvoltages on the load due to cable length

- a flat-top of 2ms duration has been considered for the converter design

- final quantities are still under discussion

# **Maxidiscap Topology**

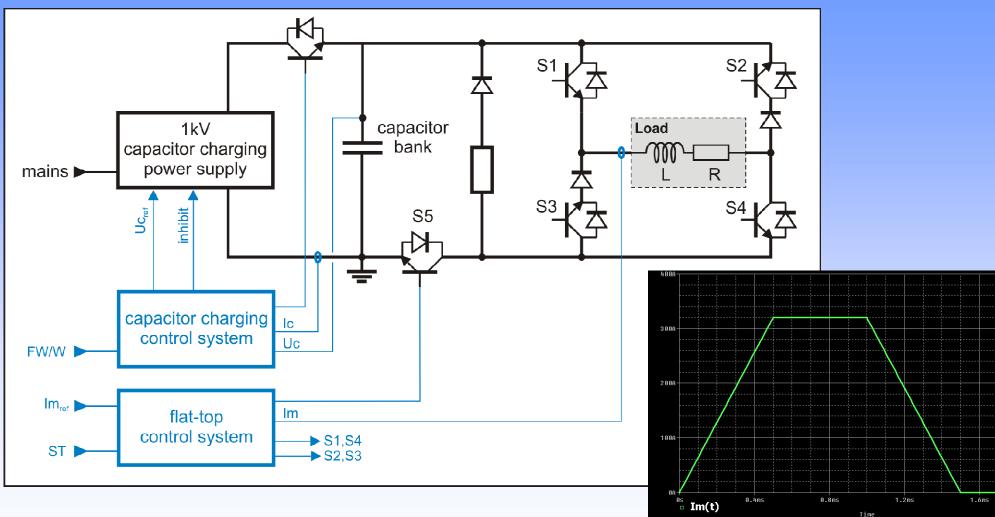

### Converter topology

- S1, S2, S3, S4 are used to ramp the current (up or down)

- S5 is used in linear mode to produce the flat-top

### **Maxidiscap Limitations**

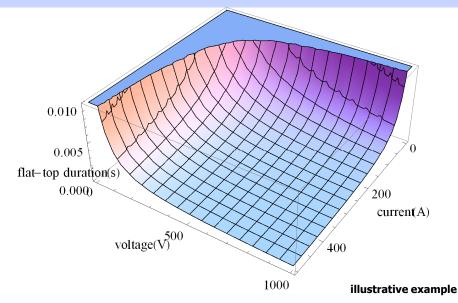

- Maxidiscap converters are pulsed power converter with a linear stage, some limitations are inherent to this topology

- the average power that can be dissipated in the linear stage is limited by the cooling

- the power dissipated in the linear stage leads to thermal cycling in the IGBT and may imply limited lifetime expectancy for the device

- the energy stored in the capacitor bank that is transferred to the load during the discharge is limited

- → the maximum flat-top duration is a function of the maximum operating current, the charging voltage and the load parameters.

### Simulations, junction temperature and expected lifetime

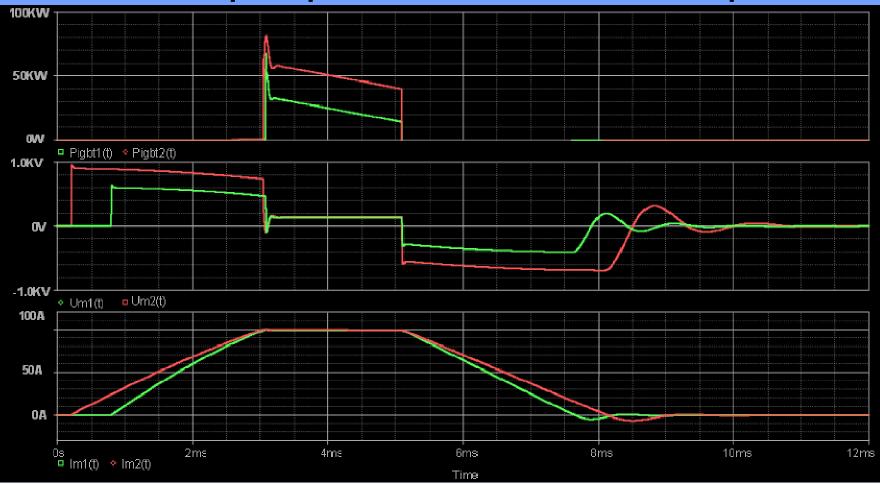

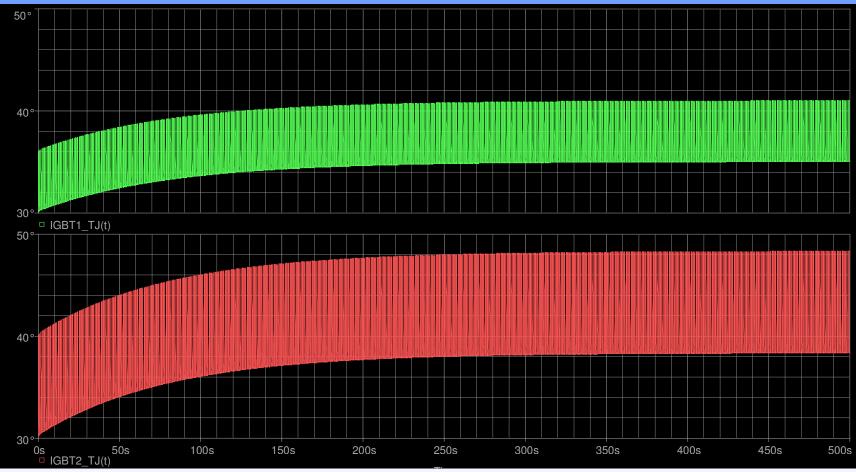

### DTL-CCDTL-PIMS quadrupoles : waveforms with 2ms flat-top

- green  $\rightarrow$  load = 1 magnet Uc=600V  $\rightarrow$

- red  $\rightarrow$  load = 2 magnets serially connected Uc=900V

# Simulations, junction temperature and expected lifetime

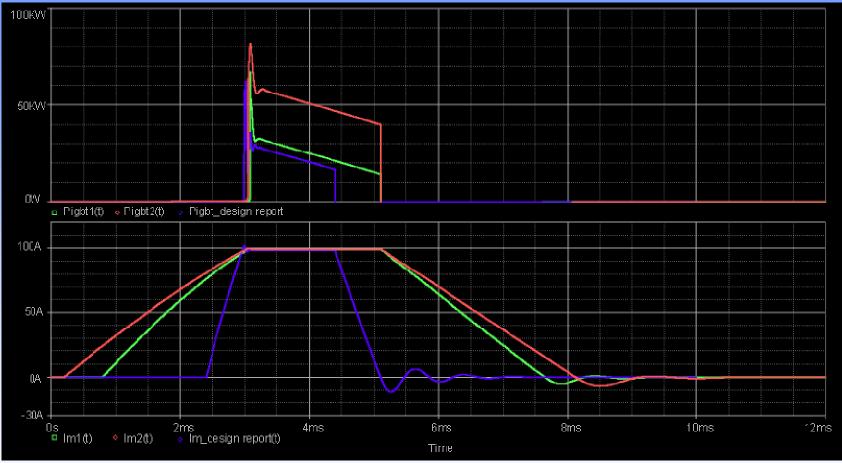

#### DTL-CCDTL-PIMS quadrupoles : change from design report

- green  $\rightarrow$  1 magnet (actual) Uc=600V flat-top duration=2ms

- red → 2 magnets in serie (actual) Uc=900V flat-top duration=2ms

- blue → 1 magnet (design report) Uc=400V flat-top duration=1.4ms

# **IGBT junction temperature and expected lifetime**

### DTL-CCDTL-PIMS: IGBT junction temperature

- green (1 magnet 2ms flat-top)  $\rightarrow \Delta Tj = 6^{\circ} MaxTj = 41^{\circ}$

- red (2 magnets 2ms flat-top) → ∆Tj = 10° MaxTj= 49°

- $\rightarrow$  with such values, thermal cycling has not effect on lifetime expectancy

# **Technical Design Summary**

|                          | application                    | DTL-CCDTL-PIMS | DTL-CCDTL-PIMS    | PSB - TL       |

|--------------------------|--------------------------------|----------------|-------------------|----------------|

| magnet                   | magnet number (serial)         | 1              | 2                 |                |

|                          | maximum operating current      | 100 A          | 100 A             |                |

| maç                      | inductance                     | 10.8 mH        | 21.6 mH           |                |

|                          | resistance                     | 0.38 Ω         | 0.76 <sub>Ω</sub> |                |

| cable<br>+filter         | inductance                     | 0.12 mH        | 0.18 mH           | 0.09 mH        |

| cal<br>+fil              | resistance                     | 0.5 Ω          | 0.6 Ω             | 0.35 Ω         |

| rter                     | power converter type           | Maxidiscap III | Maxidiscap III    | Maxidiscap III |

| IVe                      | operating voltage              | 600 V          | 900 V             |                |

| power converter          | flat top duration              | 2 ms           | 2 ms              | 1 ms           |

| wer                      | repetition rate                | 2 Hz           | 2 Hz              | 1.1 Hz         |

| d                        | quantity (workpackage)         | 23             | 0                 | 16             |

|                          | rise time                      | 2.2 ms         | 2.8 ms            |                |

|                          | di/dt                          | 45.5 kA/s      | 35.7 kA/s         |                |

| owe                      | flat-top                       | 2 ms           | 2 ms              |                |

| output current and power | fall time                      | 2.6 ms         | 3.2 ms            |                |

|                          | P peak flat-top                | 40.0 kW        | 60.0 kW           |                |

|                          | Max. Junction temp.            | 41 º           | 49 <sup>o</sup>   |                |

|                          | Delta TJ simulated (per pulse) | 6 <sup>o</sup> | 10 <sup>o</sup>   |                |

|                          | Irms (100A-2ms flat-top)       | 9.5 A          | 10 A              |                |

|                          | Pmagnet (100A-2ms flat-top)    | 34 W           | 38 W              |                |

|                          | Irms (80A-1.5ms flat-top)      | 6.9 A          | 7.4 A             |                |

|                          | Pmagnet (80A-2ms flat-top)     | 18 W           | 21 W              |                |

- RMS values are compatible with magnet design

- TL quads : the goal is to use the same converter design for both magnets parameters

### **Power Converter Modifications**

- Same converters have been used in Linac II, Linac III and LEIR but some modifications are necessary to allow flat-top with extended duration

- Power crate

- the capacitor bank has to be increased to 1000uF

- capacitor charger replacement have to be studied

- some modifications have to be foreseen (cabling, IGBT driver , etc...)

- test with filter, cables and dummy load have to be performed

- compatibility with previous versions must be kept

- Electronic crate

- FGC3 integration

- flat-top control with anti-windup system has to be evaluated

# **Basic Planning**

|                                  | Q4 2009 | Q1 2010 | Q2 2010 | Q3 2010 | Q4 2010 | Q1 2011 | Q2 2011 | Q3 2011 | Q4 2011 | Q1 2012 | Q2 2012 | Q3 2012 | Q4 2012 |

|----------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Technical design                 |         |         |         |         |         |         |         |         |         |         |         |         |         |

| Power crate modification testing |         |         |         |         |         |         |         |         |         |         |         |         |         |

| FGC3 integration                 |         |         |         |         |         |         |         |         |         |         |         |         |         |

| Prototype (electronic+power)     |         |         |         |         |         |         |         |         |         |         |         |         |         |

| Market Survey+call for tenders   |         |         |         |         |         |         |         |         |         |         |         |         |         |

| Production and reception testing |         |         |         |         |         |         |         |         |         |         |         |         |         |

| Installation and commissioning   |         |         |         |         |         |         |         |         |         |         |         |         |         |

- Technical design must be finished before the end of 2009, TL quads parameters have to be defined urgently.

- Final converter quantities are not needed before mid-2010

### Conclusion

- With the latest LINAC4 EM Quad design, it is possible to power 1 or 2 magnets in series by limiting the di/dt during the ramp

- The PSB transfer line Quads and LINAC4 Quads will use the same power converter design

- ➔ final converter design will be done when the PSB transfer line magnet design is well advanced

- Development and test of the Quadrupole Power Converter prototype will start early 2010, with series production in 2011

- → final quantities are required before tendering in mid-2010