# Status Update on the VMM3

Investigation of the Cooling Requirements

Lucian Scharenberg RD51 Mini Week, 14 DEC 2017

### Motivation of the "VMM cooling project"

#### **Motivation**

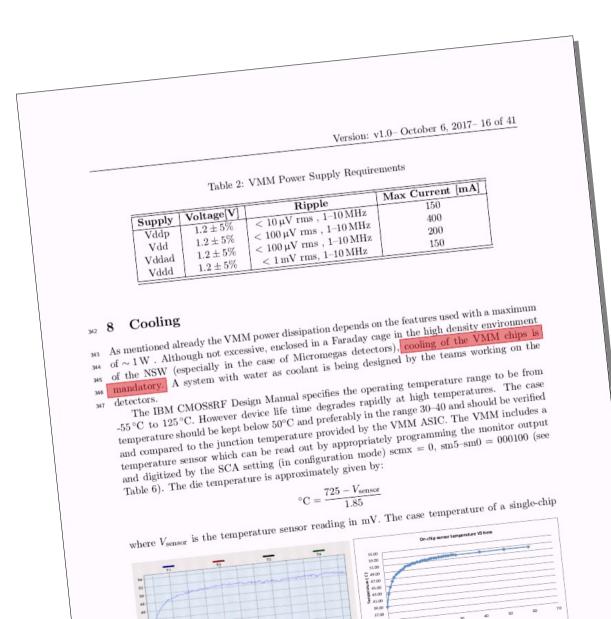

• Manual: "[...] cooling of the VMM chips is mandatory."

14 DEC 2017

#### **Motivation**

- Manual: "[...] cooling of the VMM chips is mandatory."

- ATLAS uses water cooling

- GDD/ESS/RD51: Other kind of implementation

→ VMM still consumes about 2 W of power

- Is water/active cooling required? Is passive cooling sufficient?

- Investigate performance of the VMM depending on the temperature

- $\rightarrow$  Create test set-up and perform measurements

- Why this effort?

- $\rightarrow$  NMX Experiment has movable detectors

- $\rightarrow$  Neutrons scatter on hydrogen

- $\rightarrow$  Passive much simpler; easier to adapt for others

#### GDD/ESS/RD51 Implementation

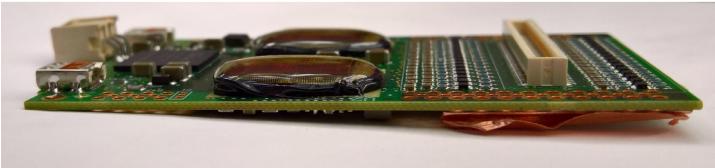

• Replace APV25 cards with VMM hybrid:

- For more details: See talks from Michael and Hans

- Build test set-up for hybrids

## Design & Assembly of the Test Set-Up

#### **Design of the Test Set-Up**

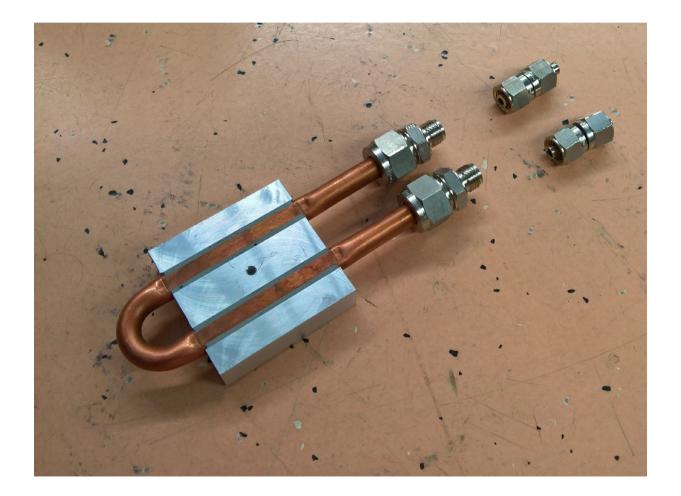

• First attempt...

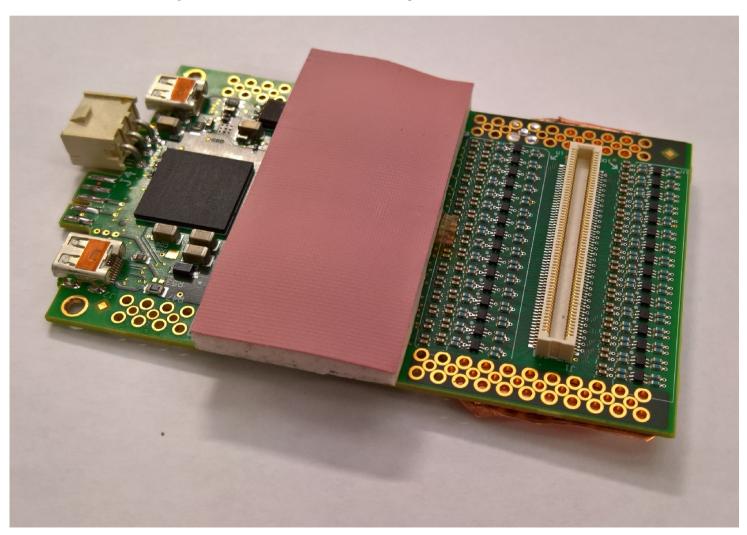

- Key component: Aavid Hi-Contact<sup>™</sup> 2-Pass Cold Plate

- In combination with: Julabo FN25-ED

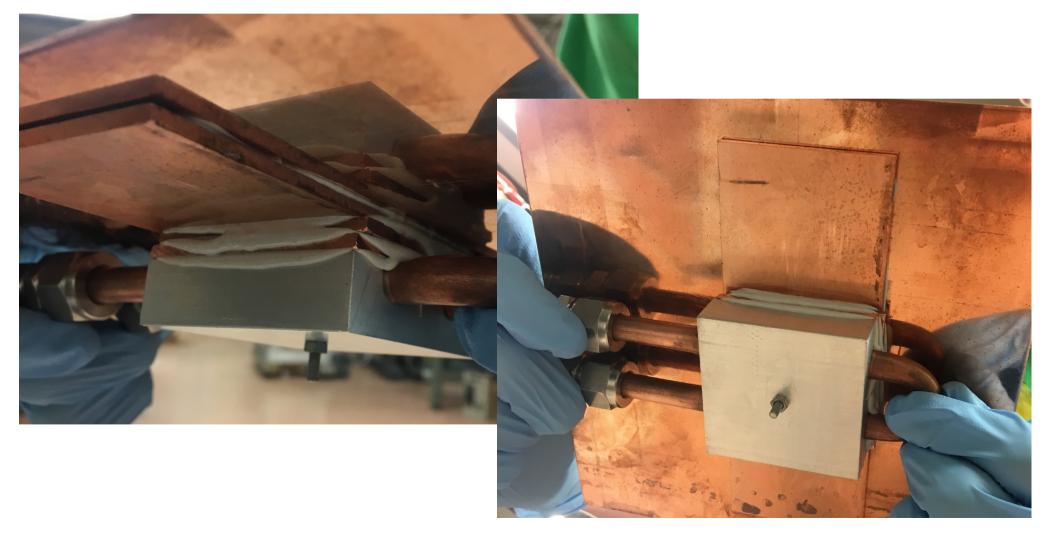

For test set-up a good heat distribution is needed

→ Use copper plates and thermally conductive paste

For test set-up a good heat distribution is needed

→ Use copper plates and thermally conductive paste

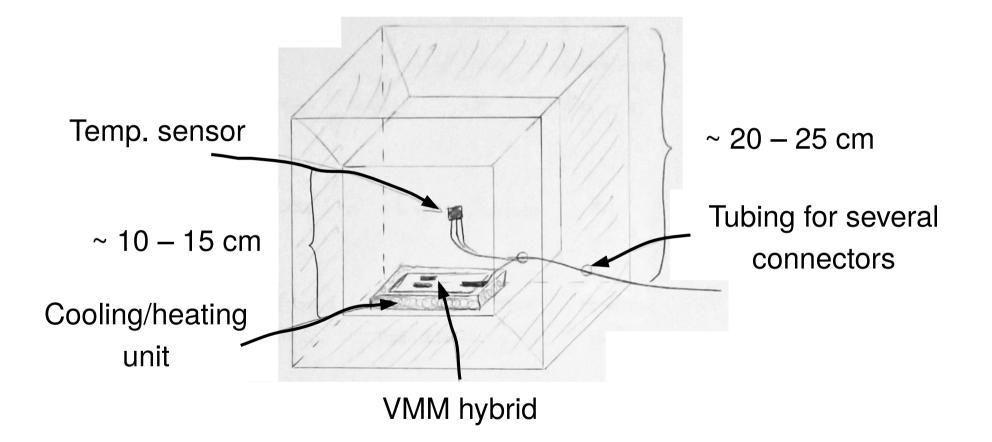

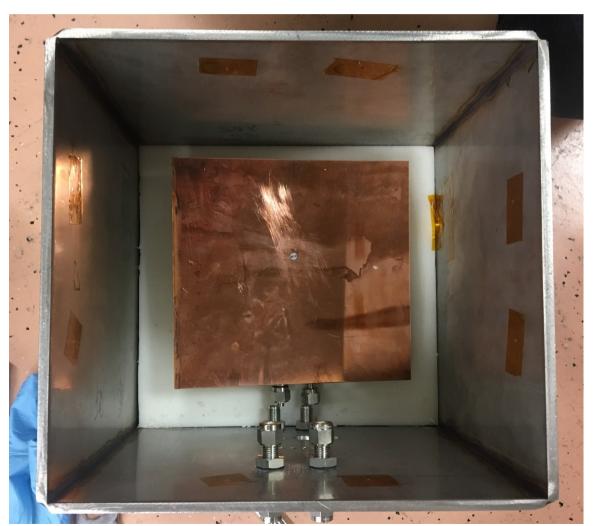

• Fit everything into box (little test environment) to protect from variations of conditions outside:

#### L. Scharenberg @ RD51 Mini Week

Build even more controlled/stabilised environment

→ Use insulating material (polyurethane)

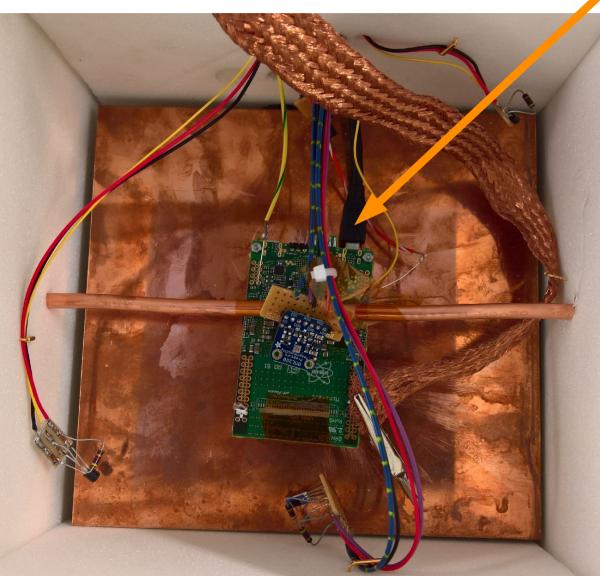

- Mechanical set-up done

- $\rightarrow$  Move on to measurement circuit

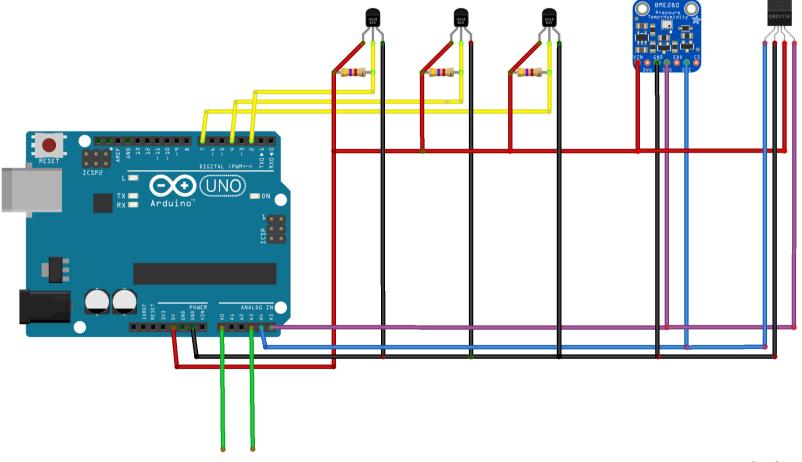

fritzing

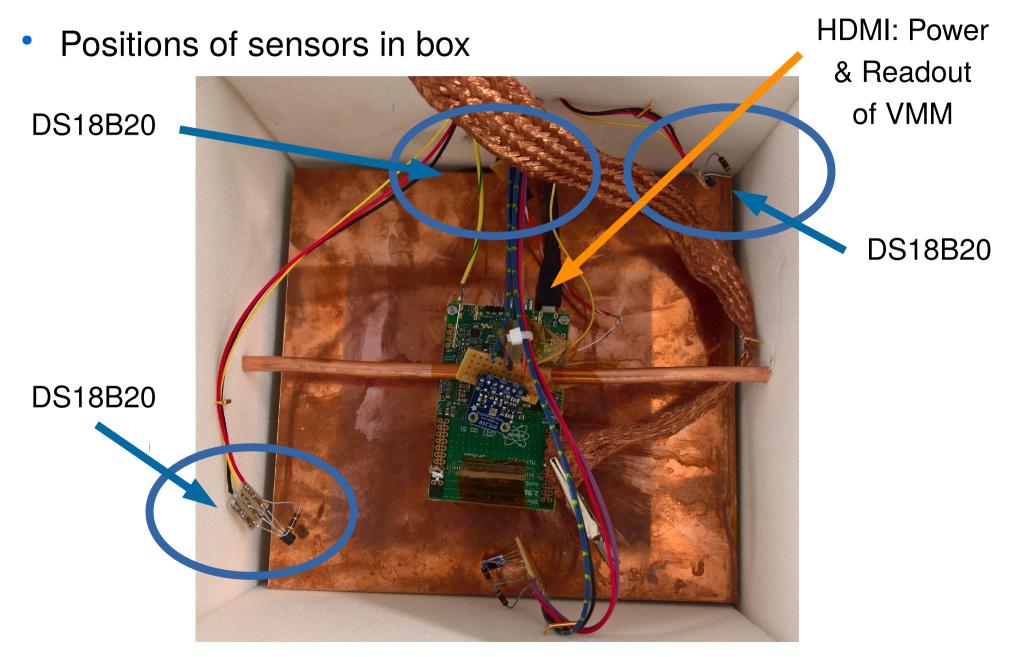

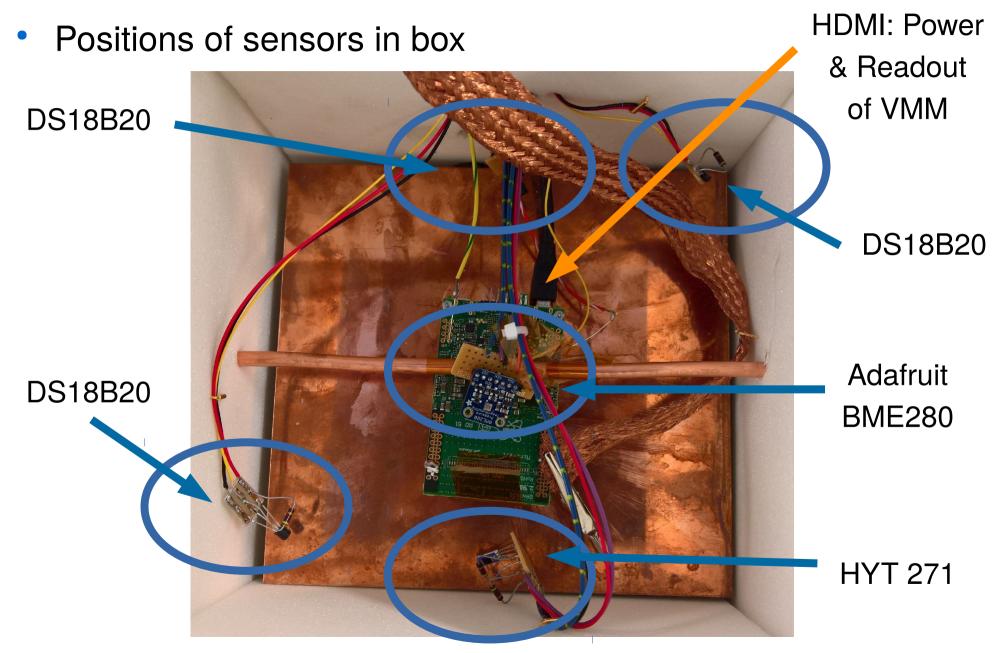

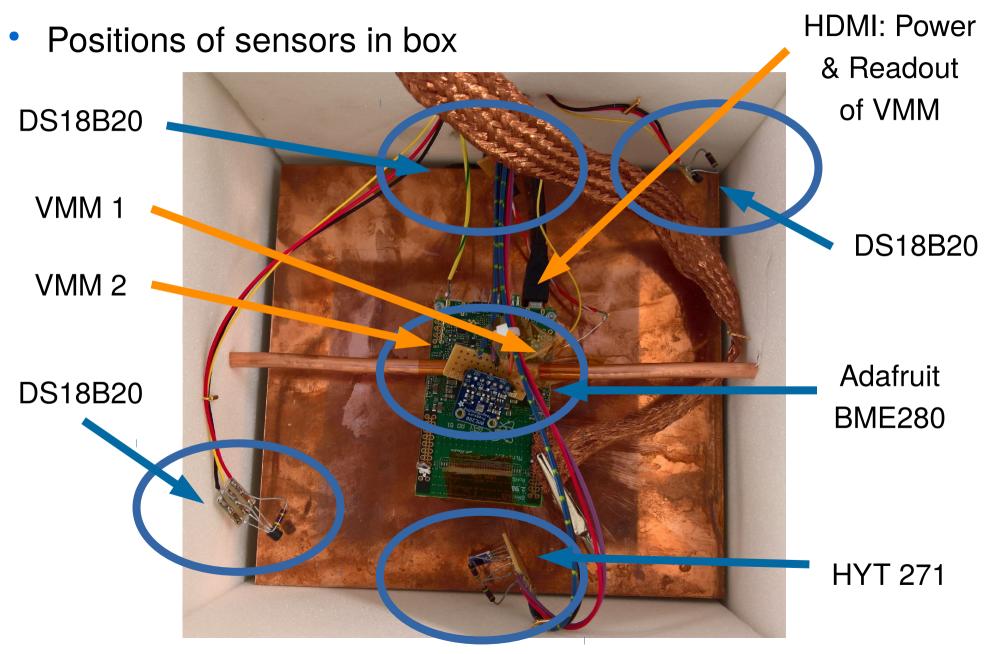

Positions of sensors in box

HDMI: Power & Readout of VMM

- Several sensors to measure the temperature

- 10-bit ADC used for digitising the voltage output from integrated temperature sensor

- Conversion of sensor voltage to temperatur

$$T(^{\circ}C) = \frac{725 - V_{sensor} (mV)}{1.85}$$

(1)

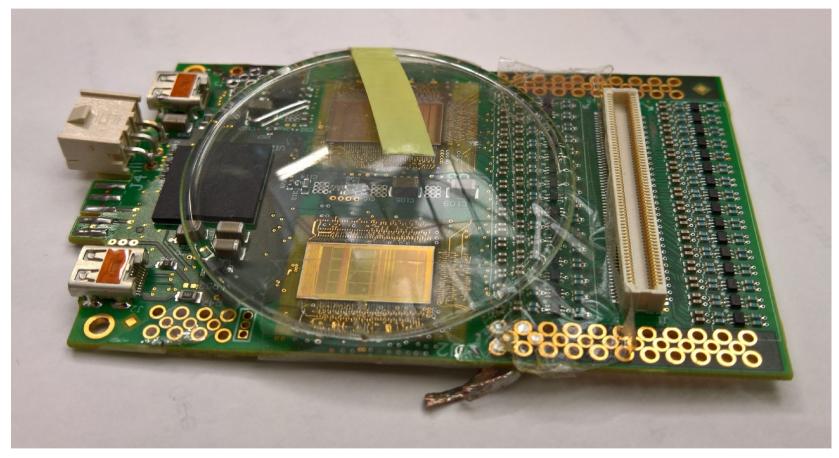

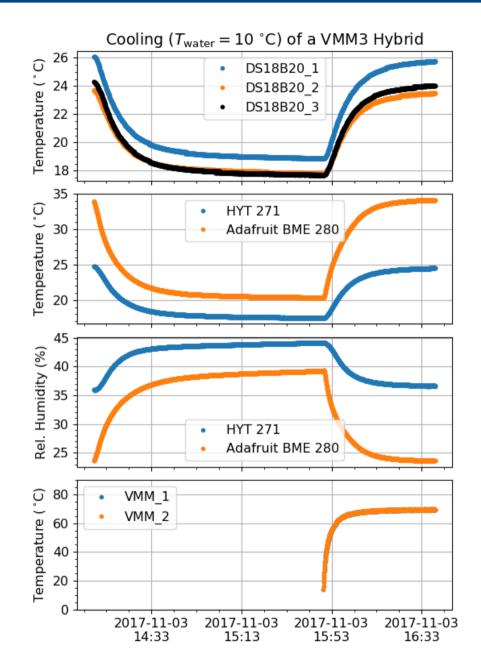

• Start testing of set-up...

#### **First Tests**

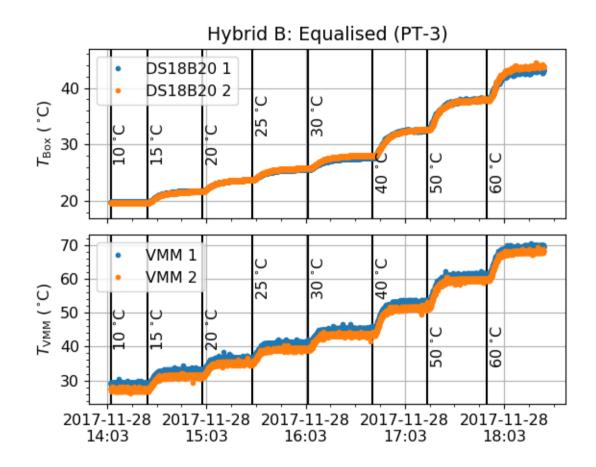

- One of the first test of set-up

- Still with glass protection

- Temperature inside chip reaches equilibrium state

- Unfortunately some of the external sensors died

- Further improvements of the set-up...

#### Prototype Glob Top

Great Thanks to Hans

#### **Further Improvement**

Get the temperature directly "inside" the chip:

→ Use thermally conductive tape

#### Data from the Performance Measurements

#### How to Quantify Performance?

As mentioned: Quantify performance depending on temperature

#### How to achieve this?

- → Take data and look how they change for different temperatures

- Problem: Data taking not possible, due to geometrical restrictions

- $\rightarrow$  Only hybrid fits in the box, but no complete detector

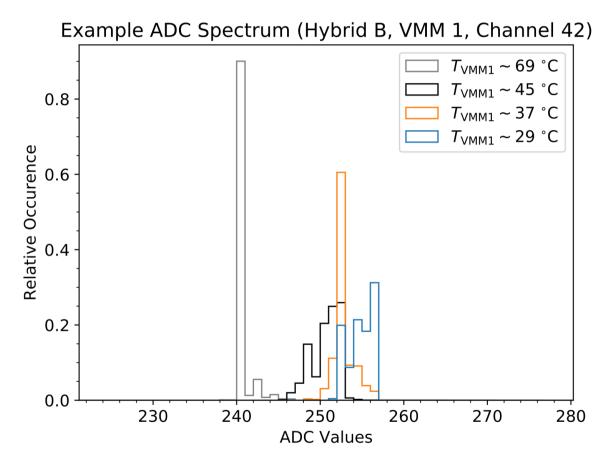

- Solution: Take test pulse spectra for different chip temperatures

- Test pulses on each channel  $\rightarrow$  64 t.p. per VMM

- Important: Makes only sense for equalised ADC baseline

#### **Measurement Process**

- Cool down environment

- Connect Hybrid to power

- Wait until equilibrium state is reached

- Start measurement with test pulses

- When measurement finished: Increase temperature and repeat process from 3.

#### **Starting Point of Analysis**

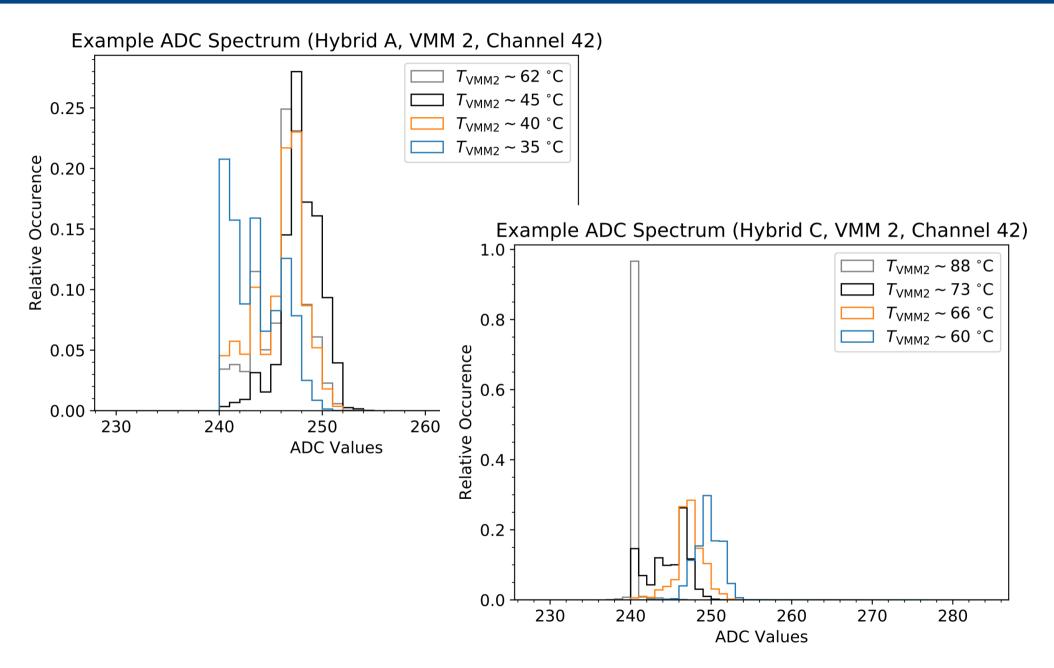

- Look at ADC spectra for each channel for different chip temperatures

- What can we extract?

- → Mean ADC value

- → Width of ADC distribution

#### Some Examples

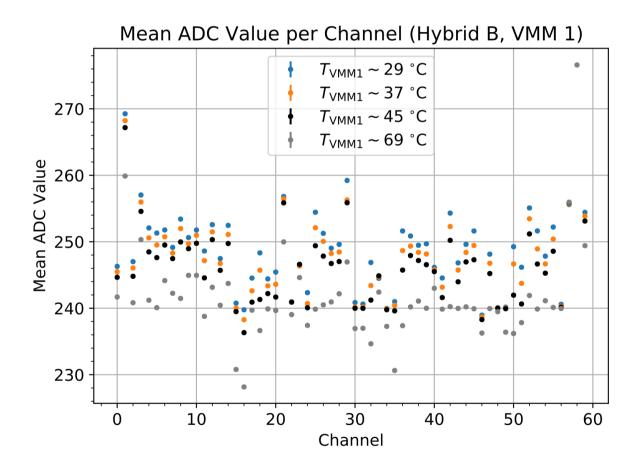

#### Mean ADC Value per Channel

• Looking at every ADC spectrum is not useful

#### L. Scharenberg @ RD51 Mini Week

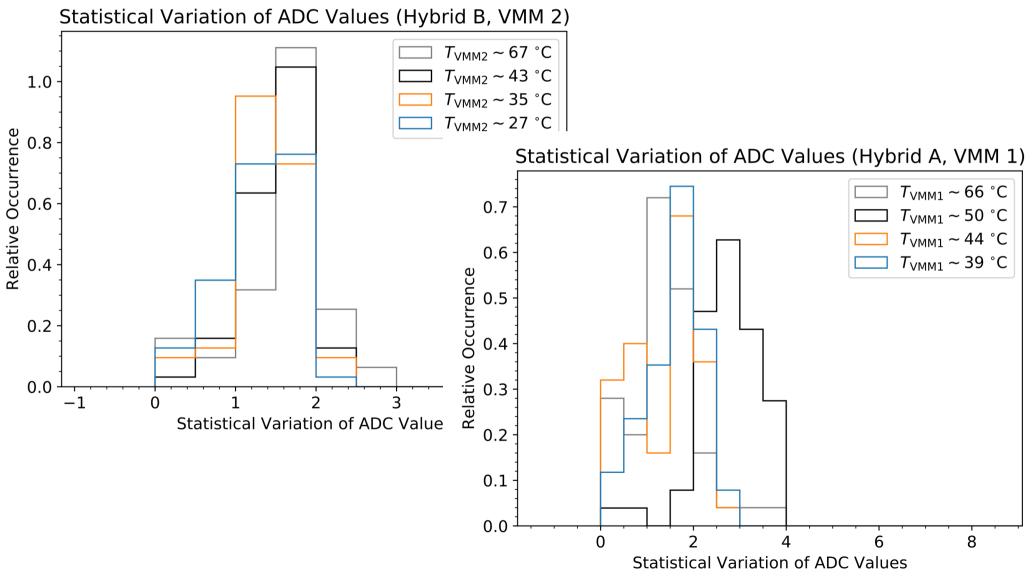

#### Width of ADC Spectra

Looking at every ADC spectrum is not useful

L. Scharenberg @ RD51 Mini Week

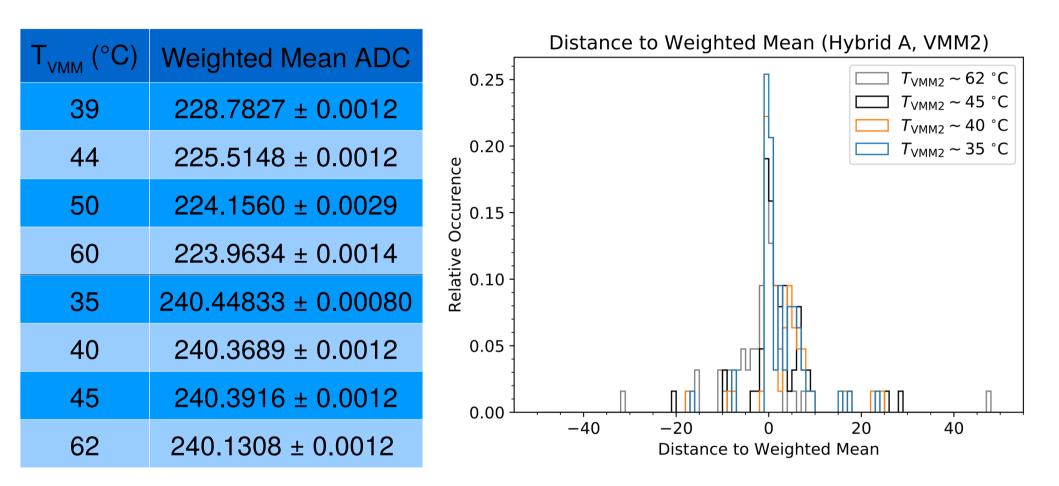

#### Behaviour of the Chip

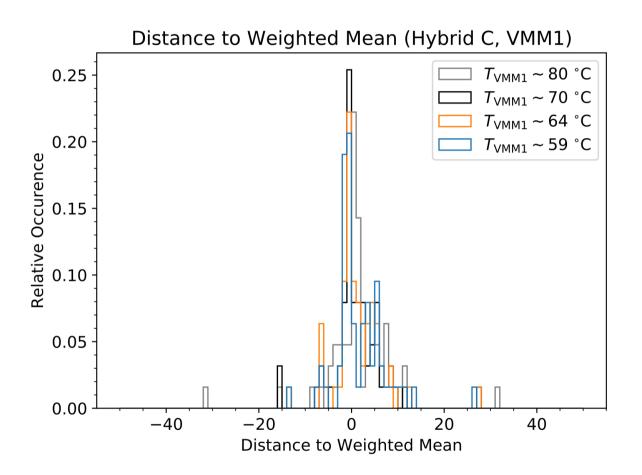

- So far: Looked at every single channel independently

- Now: Look at overall chip behaviour

- → Distance of mean

ADC (channel) to

weighted mean

ADC (chip)

#### Behaviour of the Chip

#### Weighted mean for hybrid A Top half: VMM 1, Bottom half: VMM 2

### **Conclusion & Summary**

#### **Conclusion & Summary**

- Successfully build test set-up to investigate the thermal behaviour of the VMM3 readout ASIC

- Measured 3 hybrids  $\rightarrow$  6 Chips

- Temperature dependence seen: ADC baseline shifts

- Only baseline shifts: No change in behaviour for constant temperature

- Proposal for cooling: Cooling might help, but only necessary to stabilise the temperature. Cooling itself seems to have no influence on performance. Passive cooling should be sufficient

- Did not investigate very high temperatures (> 100 °C)

→ Not enough hybrids to risk destruction

Special thanks to Florian Brunbauer, Michael Lupberger, Hans Muller and Miranda van Stenis and the whole GDD group for their great support!

# Thanks for your Attention. Questions?