# ATLAS High Granular Timing Detector Conceptual design and R&D

L. Serin on behalf of the ATLAS collaboration

- Detector location & requirements

- Sensor R&D

- Electronics R&D

- Conceptual design and on going optimisation

- Conclusion

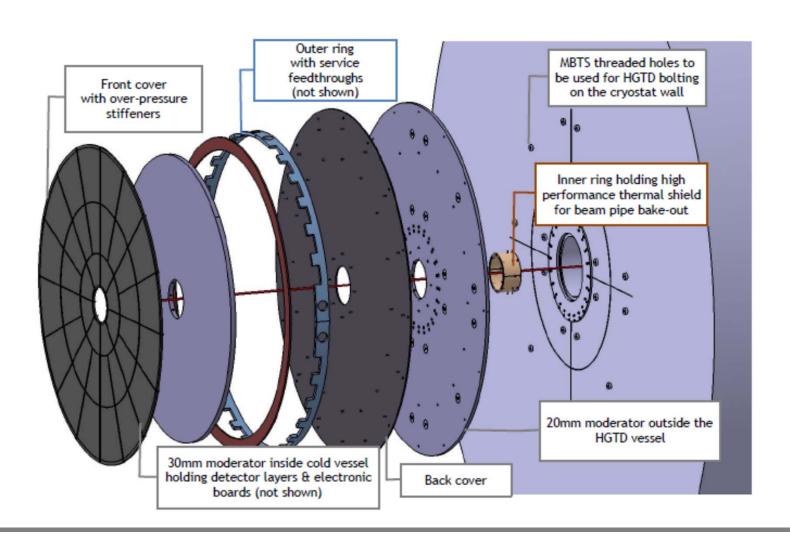

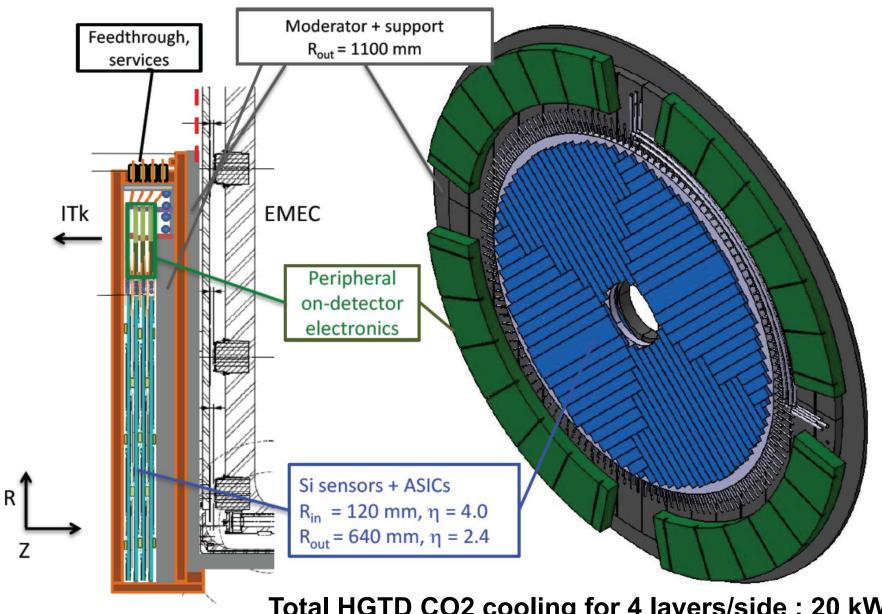

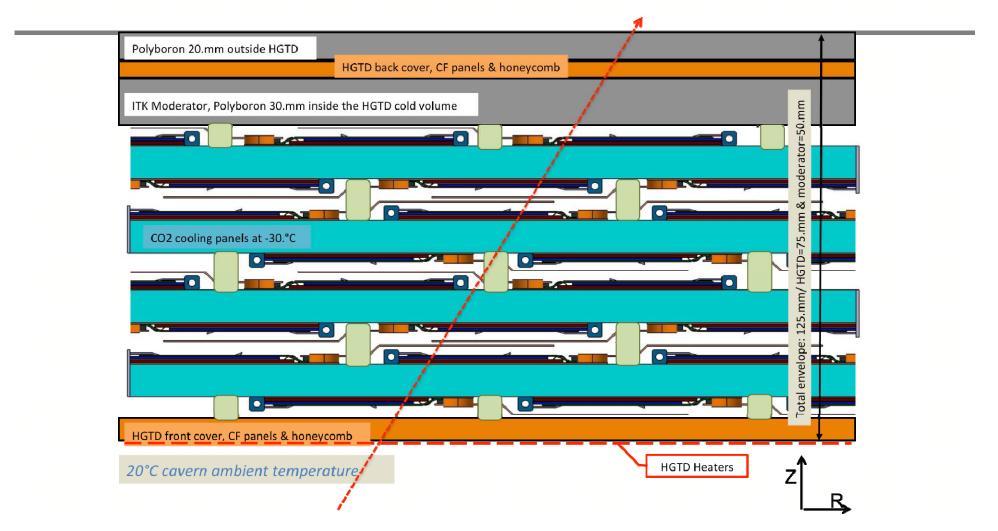

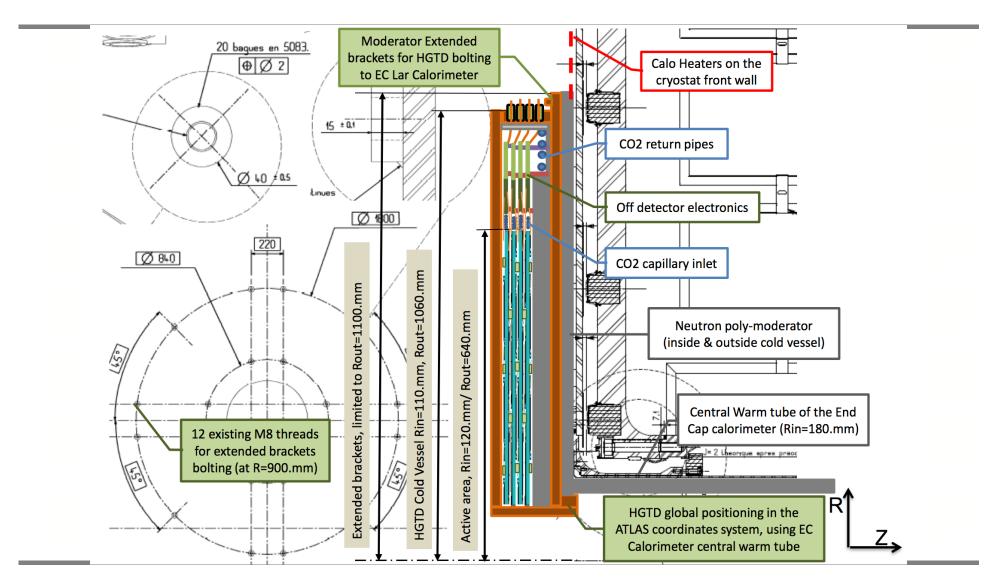

Proposed HGTD:

Radially constrained by ITk/HGTD services (64cm) and pump (12cm)  $2.4 < \eta < 4.0$

Thickness constrained to  $\Delta Z = 7.5$  cm (+ 5 cm moderator) Detector with individual planar layers (modularity/installation)

Requirement of 30 ps time resolution per mip during HL-LHC running

- **Excellent timing sensor**

- Excellent Front End Electronics → Dedicated ASIC ALTIROC

- → Thin LGAD

#### Proposed HGTD:

Radially constrained by ITk/HGTD services (640mm) and pump (120mm)  $2.4 < \eta < 4.0$

Thickness constrained to  $\Delta Z = 75$  mm (+ 50 mm moderator) Detector with individual planar layers (modularity/installation)

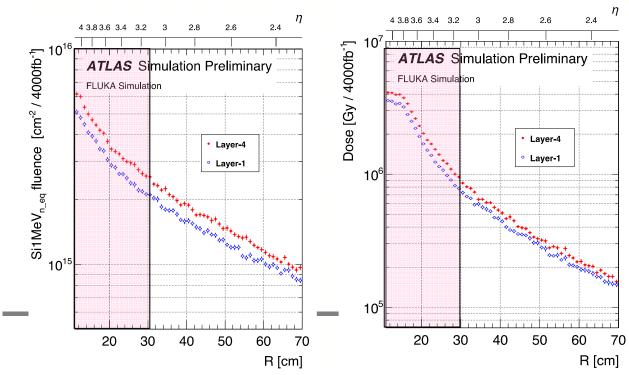

## **Expected radiation levels**

- Max neutron fluence / dose after 4 ab<sup>-1</sup>, including safety factors:

- At r=12 cm 9 x  $10^{15}$  n<sub>eq</sub>/cm<sup>2</sup> and 9 MGy

- ~20% of sensors + ASICs (r<30 cm) need replacement at 1/2 life time of HL-LHC

$\rightarrow$ max. doses: 4.5 × 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> and 4.5 MGy (r < 30 cm)

$4.0 \times 10^{15} \text{ n}_{eq}/\text{cm}^2 \text{ and } 2.1 \text{ MGy (r> } 30 \text{ cm)}$

No safety factor applied in these plots

1.5 for simulation

x 1.5 for ASIC

#### **Radiation**

- → Operation at -30°c

- → C02 cooling

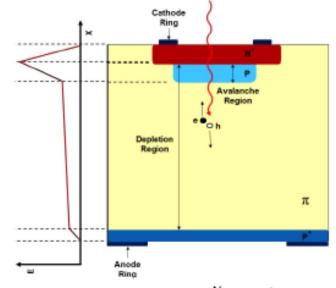

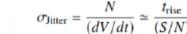

## Thin LGAD

Standard n-p silicon diode with an extra highly doped p layer

- Moderate gain ~20 with respect to pin diode

→ increase signal and keep sensor noise limited

- Thin detector :

- → better radiation hardness and short rise time (smaller jitter and Landau fluctuation)

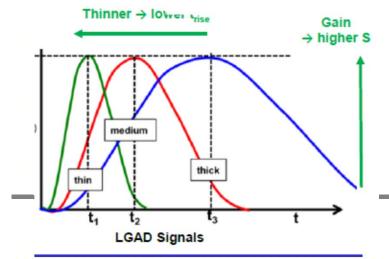

A lot of work done with the RD50 collaboration and with 3 possible vendors : CNM, HPK and FBK

Tests with different fabrication technologies, different structure, doping level, pad size before and after irradiation .....

## Unirradiated sensors performance (50 µm LGAD)

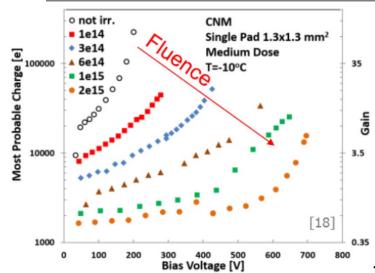

## Irradiated sensors performance (50 µm LGAD)

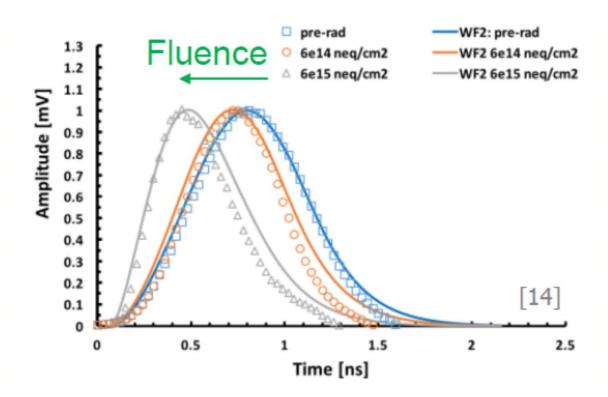

G. Kramberger et al, to be sumitted

## Radiation damage:

- Trapped of charge carriers (→thin sensor)

- Increase of leakage current (→ -30 °c)

- Modification of effective doping concentration

- → modification of multiplication layer

- → Reduction of gain thus increase of time resolution. Partially mitigated by larger bias voltage

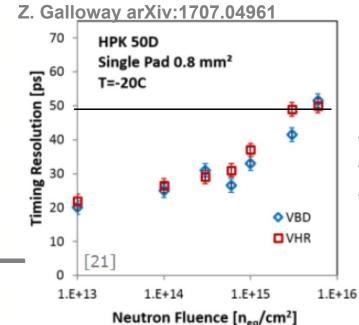

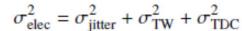

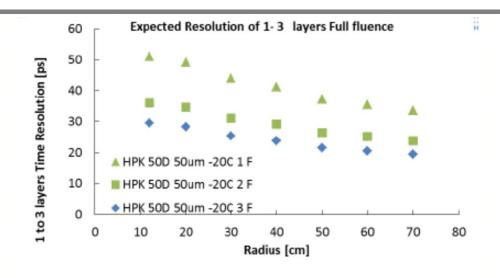

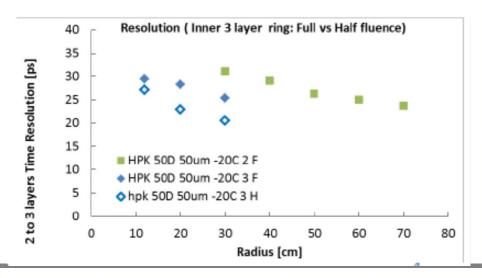

#### Time resolution:

- Operate at safe bias voltage / breakdown

- Achieved 50 ps up to  $6.10^{15}$   $n_{eq}$  /cm<sup>2</sup> at -20 °c

#### On going R&D

- Improving radiation hardness (Ga/B, C spray)

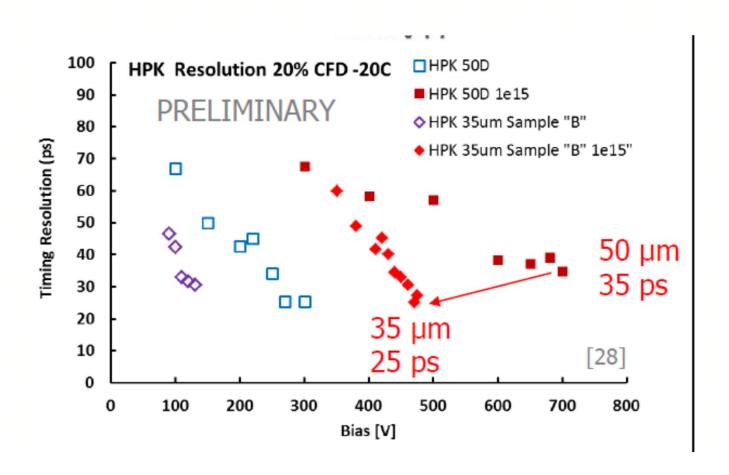

- Thinner LGAD 35 μm (excellent first measurements)

- Improving fill factor

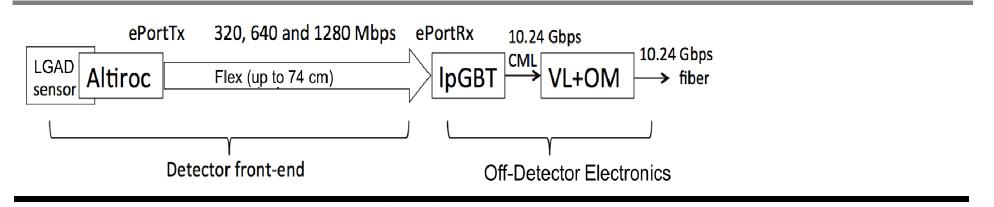

#### **Electronics**

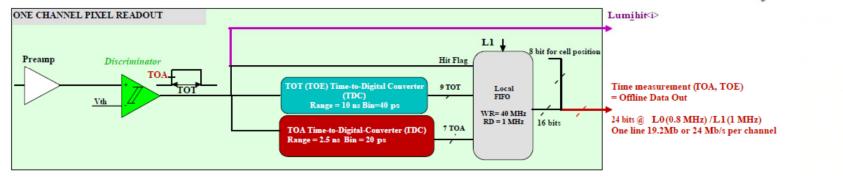

Broadband preamplifier common source configuration followed by fast discriand TDC (vernier lines)

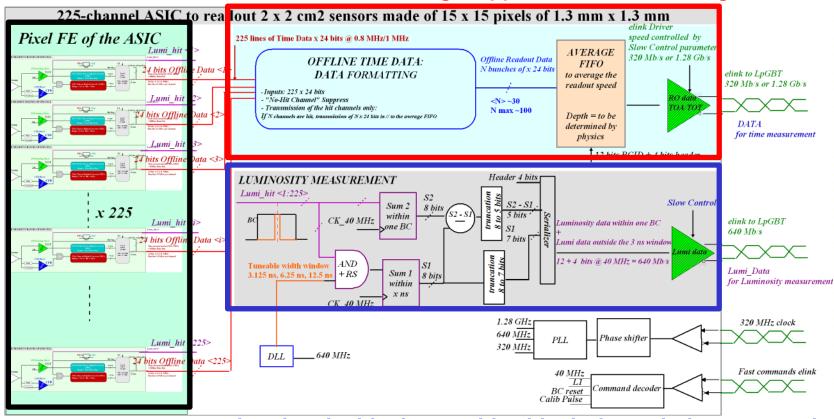

TOA measurement (20 ps) + TOT measurement (40 ps) + local FIFO until L0/L1 TSMC CMOS 130 nm

#### **Electronics**

#### Single pixel

#### Data formatting/ suppression + rate average

Luminosity block: provides hits in 3 ns window centered on bunch crossing and outside the window at 40 MHz Dedicated back end

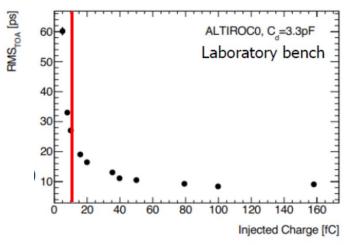

## **ALTIROC Front End ASIC**

#### TSMC 130 nm

ALTIROC0: 4 channels only analog part

25 ps for one mip (10 fC at G=20)

- → Noise to be improved and bandwidth too small

- → New version in building block submitted in December Has been bump bonded to LGAD and exposed to beam

ALTIROC 1: 25 channels with full single pixel readout (analog+TDC+FIFO) to be submitted in Feb 2018, and bump bonded to sensor Q3/1018

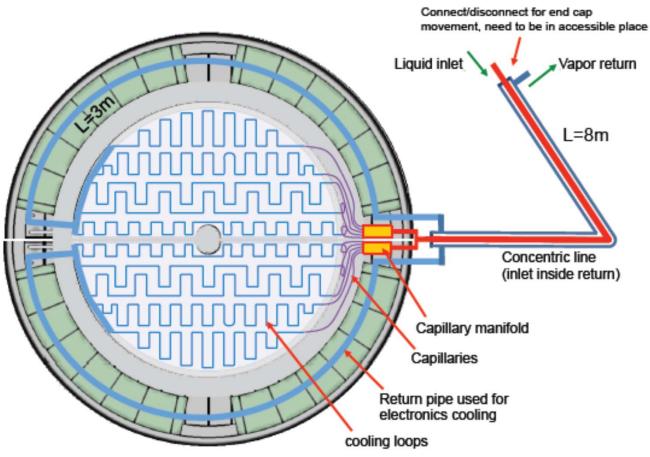

Total HGTD CO2 cooling for 4 layers/side : 20 kW 1.4 m<sup>2</sup> LGAD sensor area per layer <sub>12</sub>

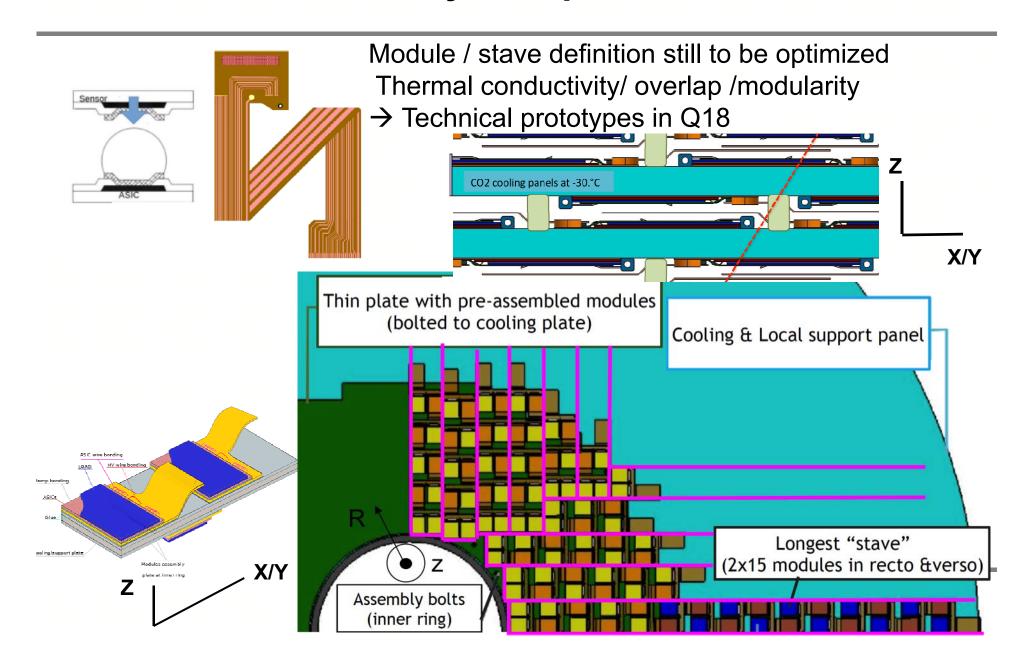

## Modules + Layer R-phi view

## Optimisation towards final baseline design

#### Sensor size (4x2 cm<sup>2</sup>):

- fitting the inner radius

- sensor yield and flip-chip yield

- unique sensor size

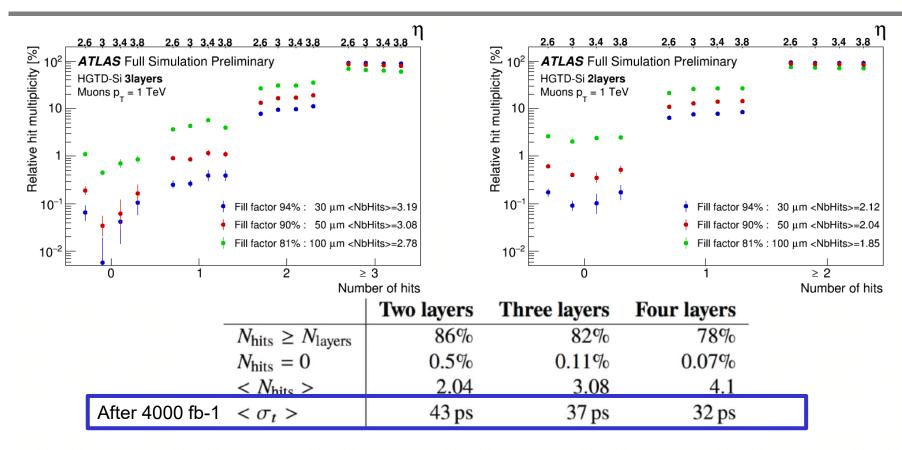

#### Number of layer :

- Dead area / efficiency

- Time resolution after irradiation

|                                   | Two layers | Three layers | Four layers |

|-----------------------------------|------------|--------------|-------------|

| $N_{\rm hits} \ge N_{\rm layers}$ | 86%        | 82%          | 78%         |

| $N_{\rm hits}=0$                  | 0.5%       | 0.11%        | 0.07%       |

| $< N_{\rm hits} >$                | 2.04       | 3.08         | 4.1         |

| $<\sigma_t>$                      | 43 ps      | 37 ps        | 32 ps       |

< 1 % geometrical inefficiency for 2 layers From 32 ps to 43 ps at worse radiation level radius assuming 60 ps/hit

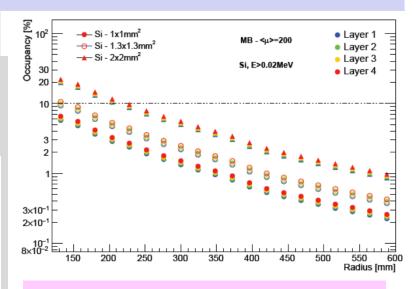

#### Granularity (1.3x1.3 mm<sup>2</sup>):

- occupancy < 10 %

- Time resolution (detector capacitance)

#### Integration:

- Half disk/vessel for easier installation

- Inner module wheel

## Conclusion

Intensive R&D since organised activity started mid 2015

→ 30 ps time resolution for mip over HL-LHC period looks feasible but still R&D on sensors and electronics to validate it

Overall detector design under optimisation to find the best trade-off between performance, construction/installation complexity/schedule and cost (to be provided In Technical Proposal in April 2018)

A highly motivated community (~20 institutes from 7 countries) is willing to build it for Phase II and improve the ATLAS detector performance under the harsh HL-LHC environment.

# Back up

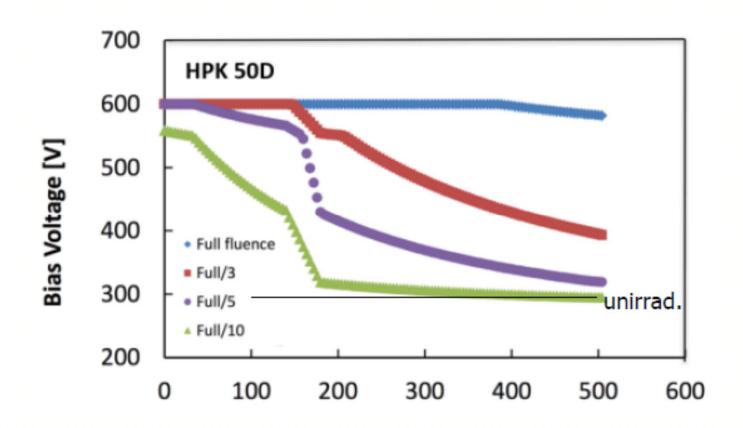

## **HV** along radius

## **Expected sensor alone time resolution at HL-LHC**

## Preliminary performance with 35 µm LGAD

## Pulse shape with irradiation

# **Main HGTD parameters**

| Pseudorapidity coverage                                       | $2.4 <  \eta  < 4.0$                            |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------|--|--|--|

| Position in z                                                 | 3420 < z < 3545 mm including 50 mm of moderator |  |  |  |

| Position of active layers                                     | 3435 < z < 3485  mm                             |  |  |  |

| Radial extension (active area)                                | 110-1100 mm (120 mm-640 mm)                     |  |  |  |

| Time resolution of HL-LHC running                             | 30 ps / MIP                                     |  |  |  |

| Pixel size                                                    | $1.3 \times 1.3 \text{ mm}^2$                   |  |  |  |

| Number of layers                                              | 2–4 per side                                    |  |  |  |

| Layout with 2 (4) layers per side                             |                                                 |  |  |  |

| Number of channels                                            | 3.15 (6.3M)                                     |  |  |  |

| Number of Si sensors $(2 \times 4 \text{ cm}^2 \text{ each})$ | 6976 (13952)                                    |  |  |  |

| Number of ASICs $(2 \times 2 \text{ cm}^2 \text{ each})$      | 13952 (27904)                                   |  |  |  |

| Total Si active area                                          | 5.6 m <sup>2</sup> (11.2 m <sup>2</sup> )       |  |  |  |

## **R-Z** view

A 4-layer design would fit in the allocated thickness but strict tolerance required

# Number of layers/performance/cost on going optimisation

0.5 % geometrical inefficiency for 2 layers From 32 ps to 43 ps at worse radiation level radius assuming 60 ps/hit

# CO<sub>2</sub> cooling

| Component                | Power                                                    | Total (kW) |

|--------------------------|----------------------------------------------------------|------------|

| Sensor                   | < 20 mW/cm <sup>2</sup>                                  | 2.23       |

| ASIC                     | $< 200 \text{ mW/cm}^2$                                  | 15.2       |

| Flex cable               | 25 mW/flex                                               | 0.35       |

| HGTD cold vessel heaters | < 100 W/m <sup>2</sup>                                   | < 0.9      |

| EC calo cryostat heaters | $120 \text{ W/m}^2$ , $50\%$ up to $R = 1600 \text{ mm}$ | < 0.6      |

| Total for CO2 cooling    |                                                          | 19.2       |

| Off-detector electronics | 30% of ASICs power consumption                           | 5          |

## **HGTD** integration

## **HGTD** integration