# Endcap Muon (CSC) Trigger Phase I and II Upgrade Plans and Status

Ivan K. Furić University of Florida

on behalf of the CSC Detector and Trigger communities

### Overview

- CSC "low" occupancy in LHC running

- utilized in design of trigger, DAQ data flow

- SLHC challenge: handle internal rates, control trigger?

- Phase I:

- Detector upstream: trig primitive quality good enough, focus is on handling increased rate

- Track Finder: handle increased rate + improve CSC standalone momentum resolution

- Phase II:

- Detector upstream: relax upper limits on number of trigger primitives (another internal rate increase)

- Track Finder: combine CSC and tracker information for ultimate momentum resolution

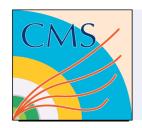

#### Dataflow Architecture Sketch

Chambers Peripheral Crates CSC Track-Finder Crate

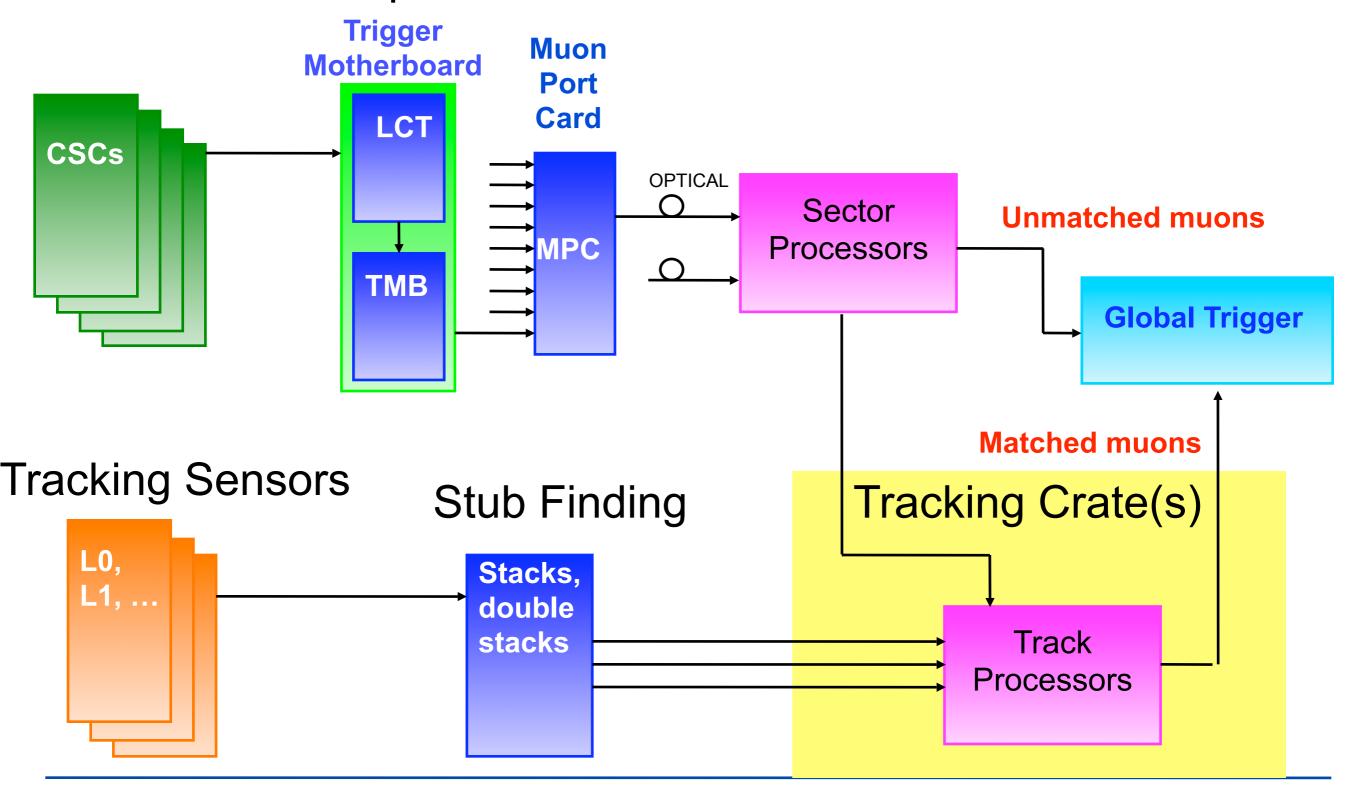

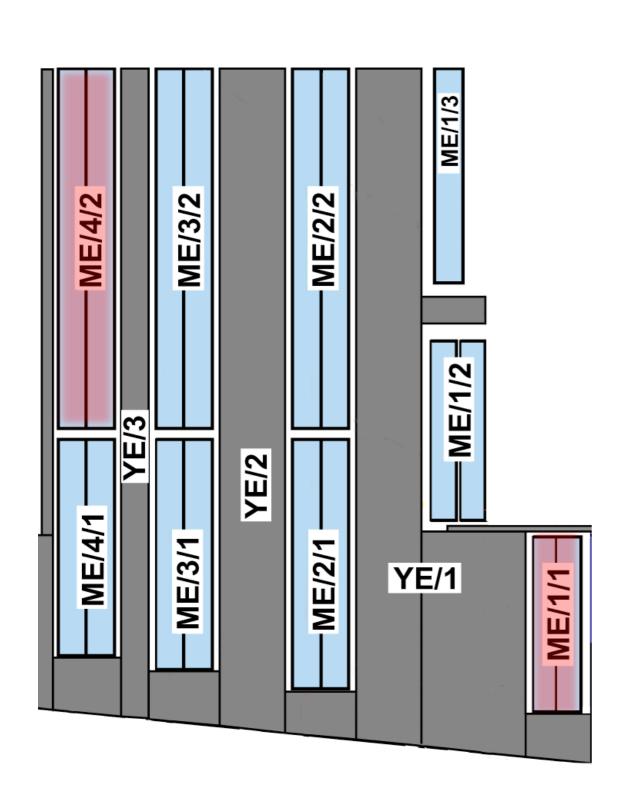

# ME4/2 and MEI/I upgrades

"Empty" YE3 disk ready for ME4/2

### Simulation result (May '09)

(Vadim Khotilovich, Alexei Safonov)

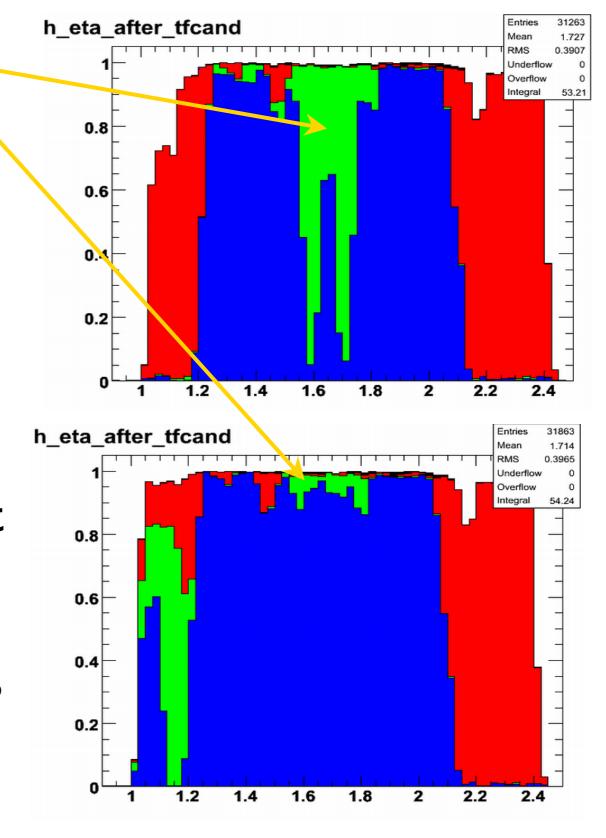

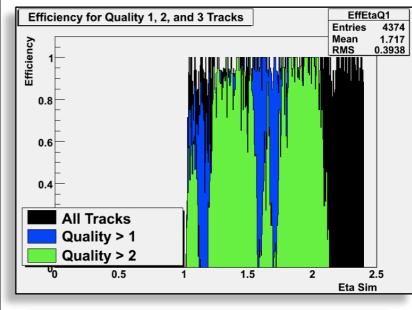

- Efficiency gaps for good quality TF tracks disappear with addition of ME4/2

- ME4/2 will be included by default in 31X

- Back-porting to 22X took a considerable amount of effort

- Thanks to the experts:

Rick Wilkinson, Tim Cox,

Oana Boeriu and Slava

Valuev!

# ME4/2 upgrade motivation

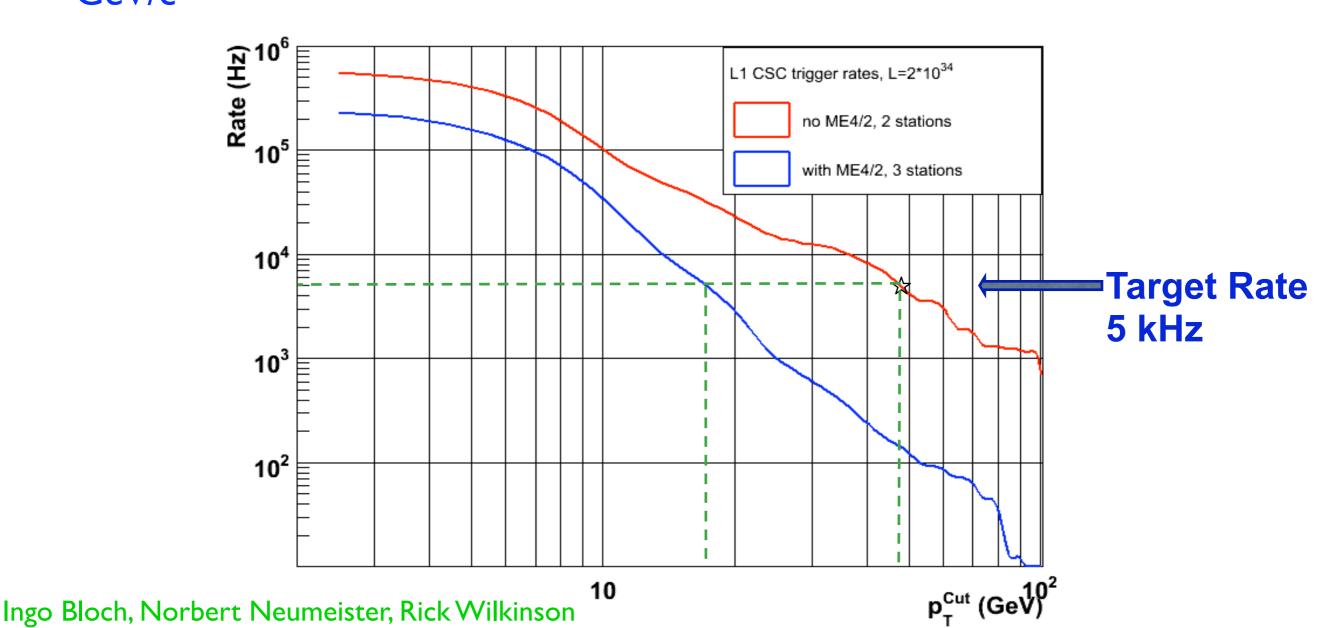

- Triggering with & without the ME4/2 upgrade:

- The high-luminosity Level 1 trigger threshold is reduced from 48 → 18

GeV/c

### "Digital CFEB" cathode board

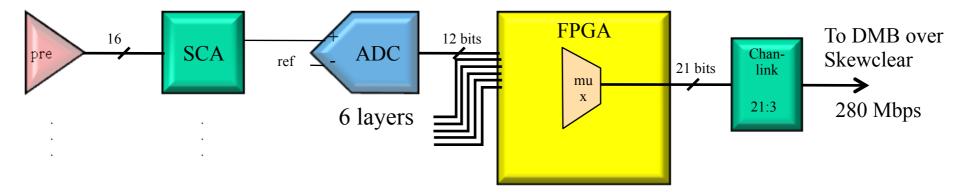

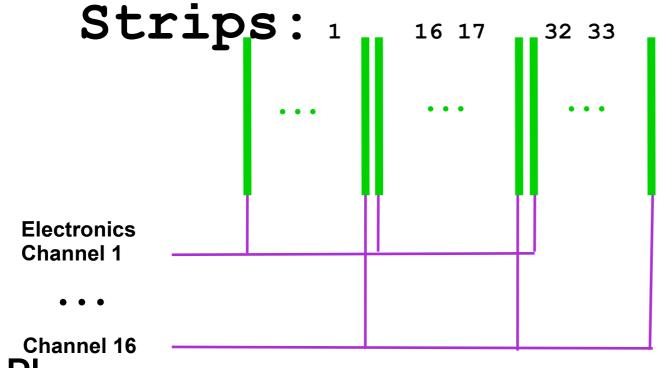

- CSC principle: digitize cathode charges to ~1%, interpolate for fine position

- Current CFEB: the ADC is multiplexed 16:1

- Requires analog charge storage ASIC (SCA)

- Serial digitization after L1A

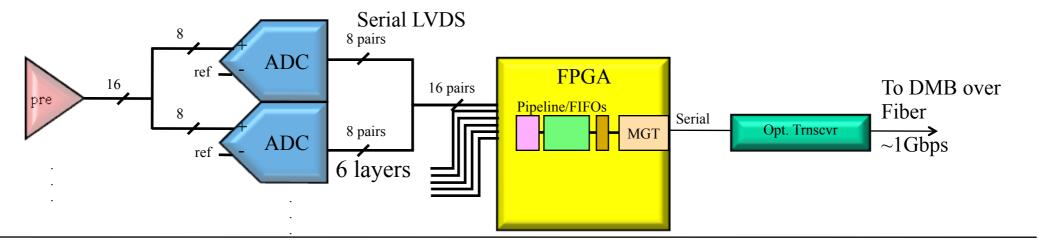

- Digital CFEB uses Flash ADCs:

- Continuous and deadtimeless digitization

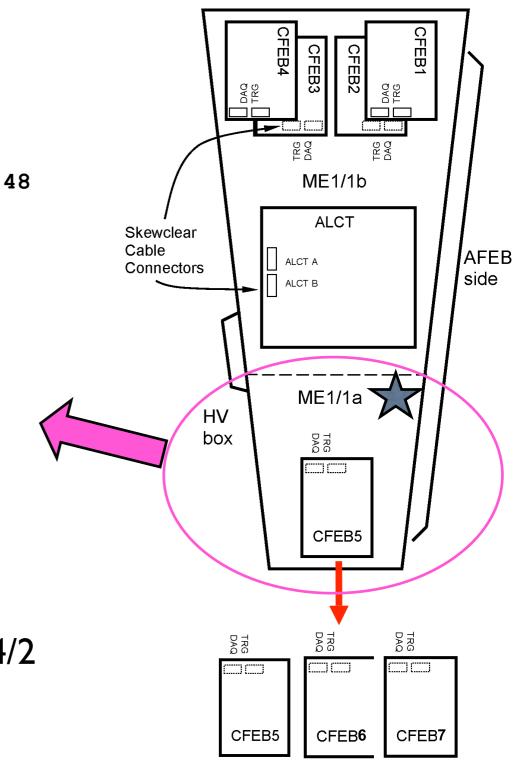

# MEI/I Restoring η 2.1-2.4

- High-η section of MEI/I

- Cathode strips are currently ganged 3:1

- Plan:

- Install DCFEB boards on MEI/I

- Move existing CFEBs from MEI/I to ME4/2

- Takes ~2.5 months per endcap

- 72 new TMB and DMB boards needed to accommodate additional inputs, optolinks

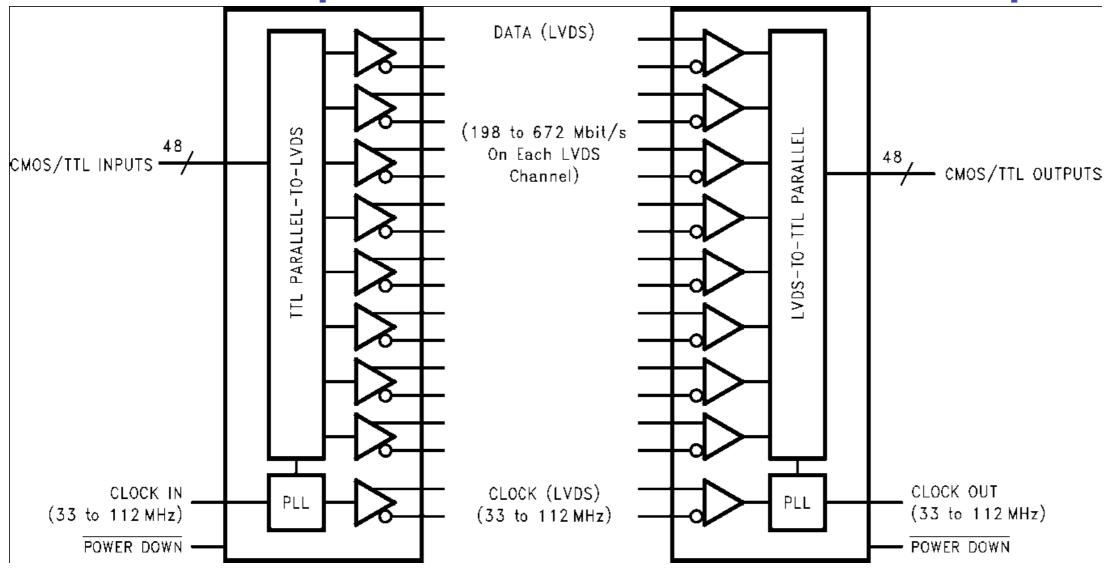

### Comparator dCFEB-to-TMB option

- Channel Link: DS90CR483/484A

- 48-8 bit Ser/Deser, requires 19 conductors per CFEB

- Use 20th conductor as "cable detect" to control Power-Down

- Has options for pre-emphasis and DC balancing

- Provides for reliable operation, even on our longest cables

- Adds ~3 BX to the trigger latency (~same as Fiber options)

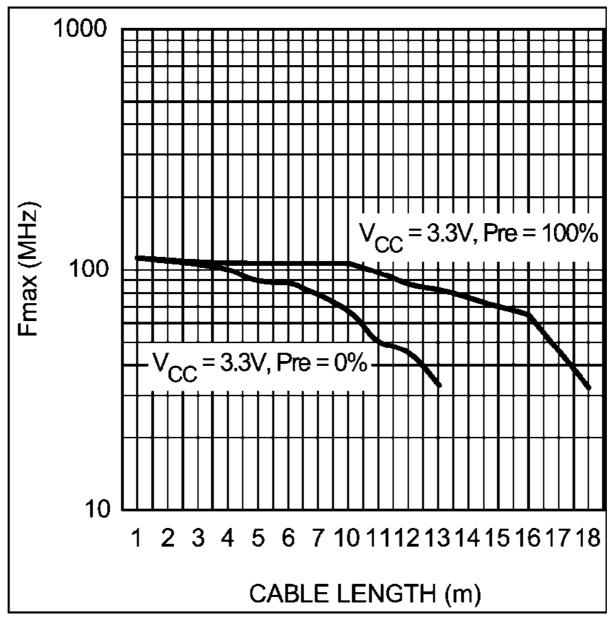

### Channel Link Performance Spec

- Performance exceeds our needs: I4 m cable @40 MHz

- Use the same 50-pin SkewClear, 5 cables to TMB!

- Each cable can carry one OR two CFEB's comparator bits

- Two-CFEB case gets appropriate fan-out at MEI/I Patch Panel

#### TMB-to-MPC

#### For MEI/I the rates are very high...

- How to send 4 LCTs per BX to MPC?

- Efficiency will suffer if we don't do this

- Review Virtex-5 capabilities: SelectlO

- Up to 800 Mb/sec on single ended lines

- Up to 1250 Mb/sec on differential lines

#### Using current backplane resources, what can we do?

- Consider differential signals at 320 Mb/sec, FPGA-to-FPGA:

- Must go from one mezzanine connection to the other...

- ...through two backplane connectors!

- This will double the bandwidth, allows 4 LCTs per BX

- Requires much "proof-of-concept" testing

- Is it reliable? Should we abandon the mezzanine?

- Signal distance is only ~0.5 m: Can it work?

# Port Cards Current design is adequate for LHC luminosity

- 2 LCTs (di-muon signal) + 1 (background) = 3 LCTs per Port Card per BX

- With luminosity upgrade, we expect ~7 LCTs per Port Card per BX.

- Preliminary simulated data, no measurements so far

- Reality could be worse

- Port Card becomes a bottleneck

- Solution:

- Keep 2 Trigger Primitives per chamber

- Bring all LCTs to SP (18 per Port Card per BX), no filtering

- May keep the filtering option in Port Cards, in case it's needed

- Port Cards have to be redesigned and replaced system-wide

- Faster data links evaluated.

### Trig. Primitives -> Coordinates

- Presently, conversion is done using large LUTs

- 4MB per primitive

- For upgrade:

- Using large LUTs impossible: too much memory

- Make conversion inside FPGA

- Combine LUTs and logic to reduce memory size

- Use  $\theta$  instead of  $\eta$

- Using  $\theta$  allows for uniform angular extrapolation windows, no need to adjust them depending on  $\theta$

# Track reconstruction logic: Expanding Current design

| Module                                                    | % in current<br>design | increase<br>factor | %<br>upgraded |

|-----------------------------------------------------------|------------------------|--------------------|---------------|

| Multiple Bunch Crossing Analysis (BXA)                    | 8%                     | 36                 | 282%          |

| Extrapolation units (EU)                                  | 23%                    | 11                 | 262%          |

| Track assembly (TAU)                                      | 1%                     | 4.5                | 4%            |

| Track parameters assignment (PAU)                         | 13%                    | 4.5                | 57%           |

| Sorting, ghost cancellation (FSU)                         | 51%                    | 20                 | 1012%         |

| Output Multiplexor (MUX)                                  | 2%                     | 4.5                | 9%            |

| BX adjustment to 2 <sup>nd</sup> trig. primitive (BXCORR) | 2%                     | 1                  | 2%            |

| Total                                                     | 100%                   |                    | 1628%         |

That's too big reserve at God switchle FDC A for reserve to large relative to current: about 16 x bigger

That's too big, may not find suitable FPGA for reasonable cost.

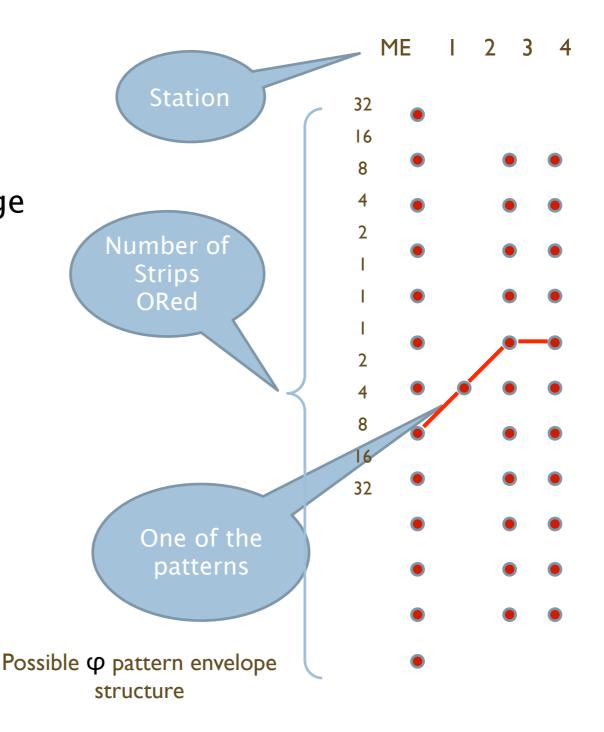

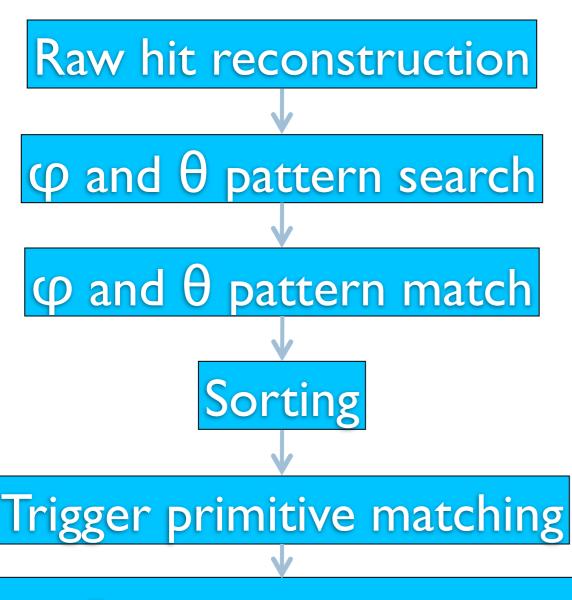

# Pattern-based TF

- Investigating another approach:

- Pattern-based detection

- Separately in  $\varphi$  and  $\theta$

- Once the patterns are detected, merge them into complete 3-D tracks

#### Benefits:

- Logic size reduction

- Certain processing steps become "natural", logic for them is greatly simplified or removed

- Multiple Bunch Crossing Analysis

- Ghost Cancellation

- Automatic track timing on 2<sup>nd</sup> trig. primitive

# Pattern-based finding

Precise parameter assignment

- Similar to pattern search logic in front-end boards (ALCT)

- Sector is split to 5  $\phi$  zones and 6  $\theta$  zones defined by chamber coverage

- Patterns detected independently in each zone

- Best φ and θ patterns matched together to make 12 track candidates

- Best three are selected by sorting logic

- Corresponding trig.

primitives found, precise

parameters assigned.

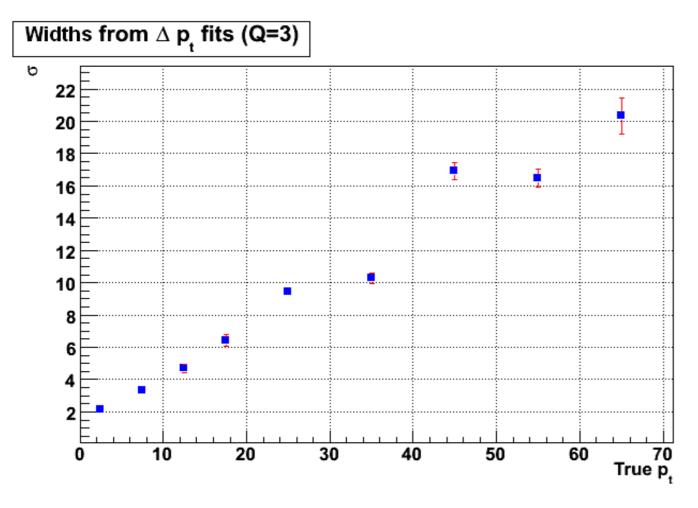

### **CSC TF Resolutions**

p<sub>T</sub> resolution of TF: current LUT's - 40%

- better LUT's developed, not deployed yet 30%

[E. Berry (Princeton), A. Kropivnitskaya (UF)]

- design predictions 20-30% below 30 GeV/c

# Further Improvements

- There is unused information in the TF fit:

- phi information is truncated in fit

- ignore track direction in chambers

- ignore staggering in Z of chambers

- eta information truncated to 4 bits in fit

- segment quality ignored

- room for further improvement of CSC standalone track finding

- follow up with simulation work to estimate impact

# Phase I Summary: • Detector electronics upgrades deal with increased

- Detector electronics upgrades deal with increased internal rates and occupancy

- ME 4/2 increases high quality track coverage

- Track Finder expects significant I/O and processing challenge due to increased occupancy

- investigating pattern based approach as solution

- TF fit can incorporate more information to improve momentum resolution measurement

- follow up with simulations to evaluate impact

- Phase II studies found resolution important for track seeding window width, efficiency

- upgrade needs to incorporate both increased volume and better resolution - next major push

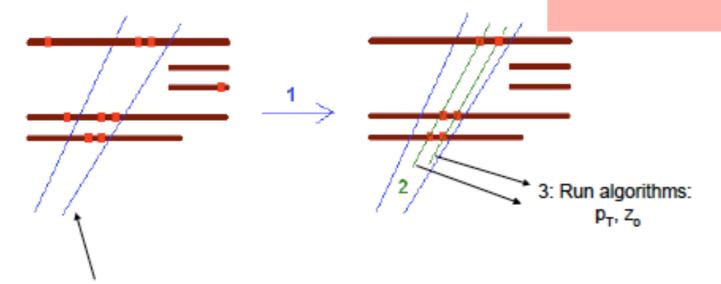

### Phase II: CSC + Tracker Trigger

### Illustration

More details: talk by B. Scurlock, Muon Phase II session

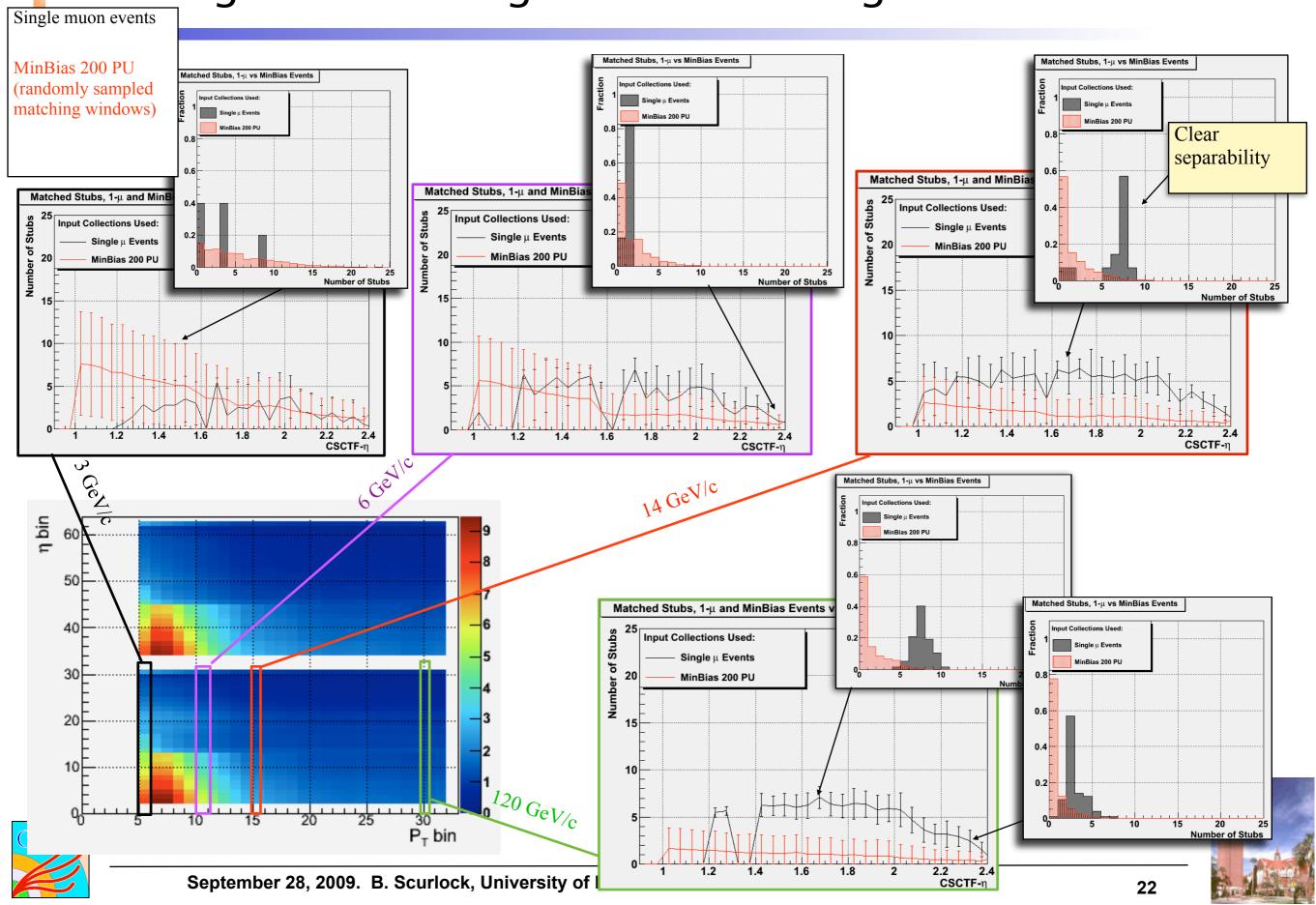

- Step 1: Use matching windows to cut stubs based on Trackfinder<sub>z,φ</sub>-Tracker<sub>z,φ</sub>

- Step 2: Only keep stubs that are correlated in Δφ & Δcotθ (ie φ<sub>dstack2</sub>-φ<sub>dstack0</sub>)

- Step 3: Apply r-z algorithm → cot(θ) & z<sub>o</sub>

and r-φ algorithm → p<sub>T</sub>

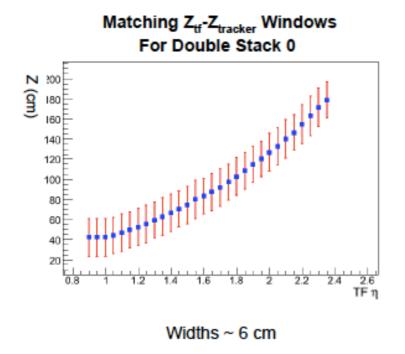

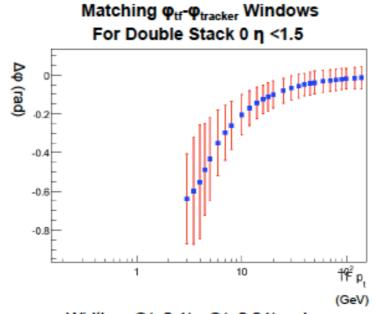

### CSC+Trigger Matching Windows

Examples of For Double Stack 0:

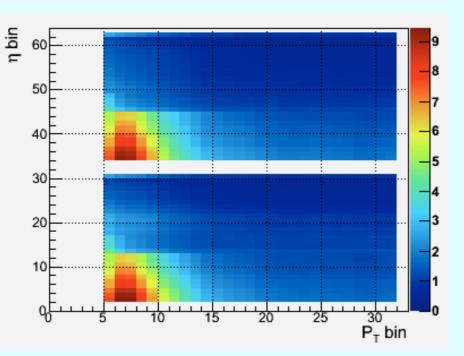

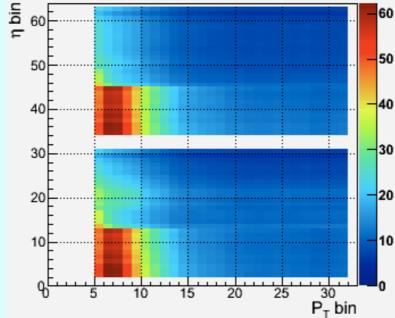

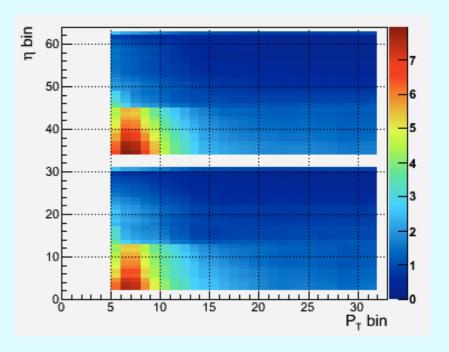

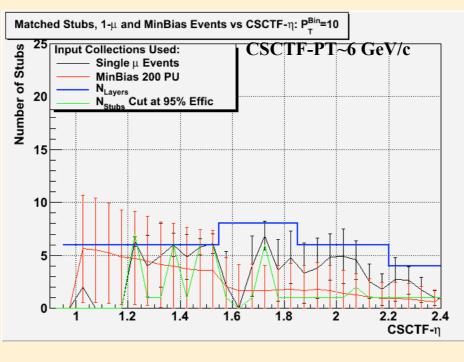

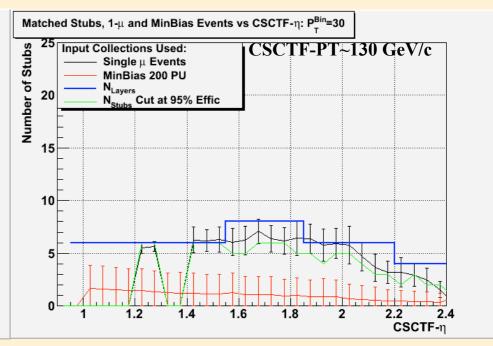

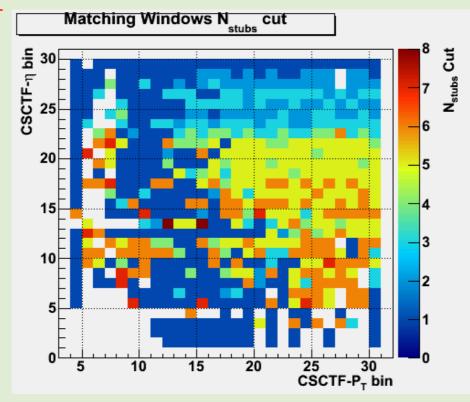

Widths =O(~0.1) - O(~0.01) rad η dependence low p<sub>T</sub> due to inhom. B-field Can be tightened if necessary6 Matching windows are defined for all possible CSCTF-P<sub>T</sub> (5 bits) and CSCTF-η (5 bits per endcap) values. Average matchwindow-occupancy plots shown below are a function of these CSCTF bins and were made with min bias events (200 PU).

#### Stubs from unclustered PixelDigis

#### Stubs from clustered PixelDigis

### Matching Windows: Signal versus Background

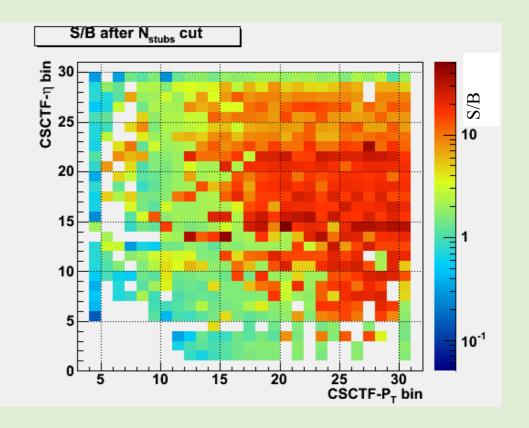

#### Matching Windows: Separating Signal from Background

Once matching windows are retuned, expect that counting can provide a powerful handle for rate reduction from noise and CSCTF mis-measurement.

Example exercise: tune matching window bin-by-bin N<sub>stubs</sub> threshold to accept 95% of signal stubs. Cuts and S/B versus bin seen on right →

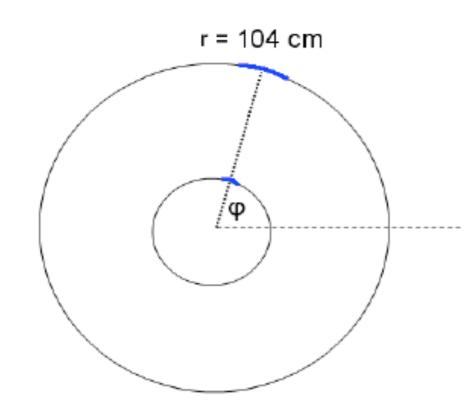

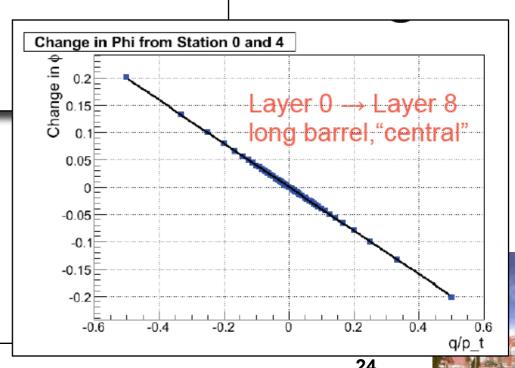

### P<sub>T</sub> Estimate 1: Using Δφ

Circle Fit Approximation:

$$\phi = \phi_0 + \arcsin(\zeta R / p_T)$$

linear approximation:

$$\Delta \phi \sim 1/p_T$$

$$\Delta \phi \sim \Delta R$$

- sensors report local coordinate → global φ

- measure φ in 100 μm units of arc length at 104 cm

- $\Delta \phi_{09} = \Delta \phi_{ij} \cdot \Delta R_{09} / \Delta R_{ij}$

- $\Delta \phi_{09} \rightarrow 1/p_T \rightarrow p_T$

Approach demonstrated to achieve 2% P<sub>T</sub> resolution

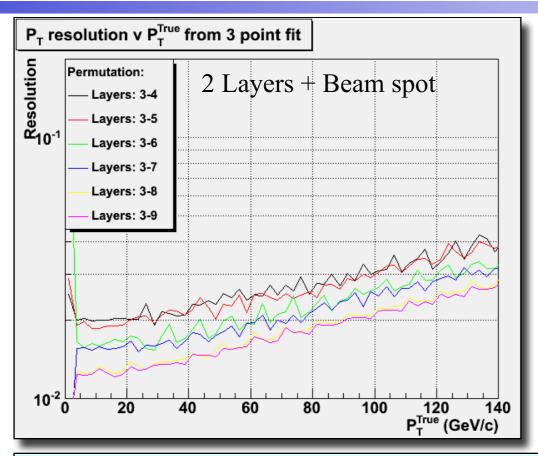

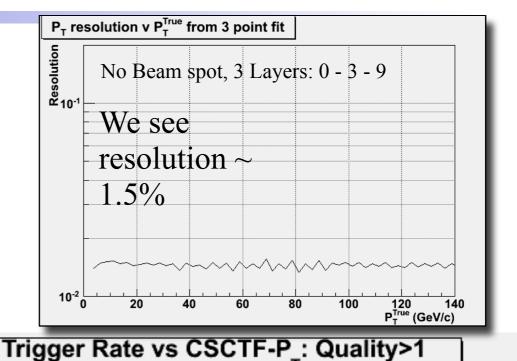

### PT Estimate 2: Circle-Fit Resolutions

**University of Florida, CSCTT Model**

P\_Thi25hold

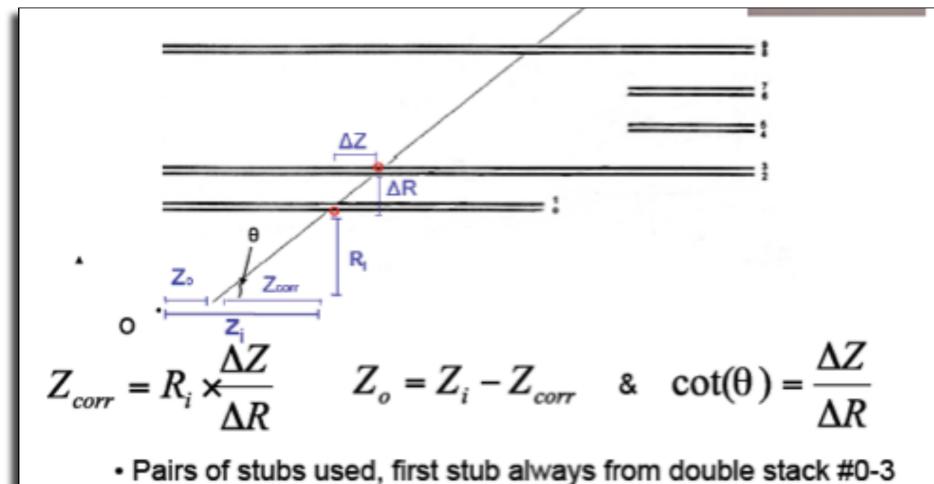

### $cot(\theta) \& Z_0$

- Similar triangles

- cot(θ) and Z<sub>corr</sub> calculated then stored in a lookup table.

CSTT model has been demonstrated to achieve zo resolution 640 µm and cot(θ) resolution 0.002

### Phase II Status:

- New manpower: B. Scurlock (UF)

- reviewed and integrated code used in summer studies, validated internal consistency

- results reported in July still stand, further developed

- new studies:

- counting tracker stubs in matching window rejects background. More tracker layers in trigger lead to more reliable trigger output

- 3 layers of tracker in trigger allow for beam spot independent pt measurement and beam spot estimation on line (track beam position in real time)

## Conclusions:

- CSC electronics upgrades will increase internal data throughput for high luminosity running

- CSC TF Phase II studies with LB geometry converged.

- Recently full CVS permissions, committing code in the upcoming few days

- CSC TF Phase I challenge: increased multiplicity + better resolution, both at the same time

# Supporting Material

### Phase II: CSCTT Algorithm

- Define regions of interest to help pre-sparsify tracker readout

- Assume stub information is read out from tracker

- Define narrow roads in φ, z to further filter tracker readout

- Tracker stubs have excellent positional resolution utilize internal correlations

- Attempt fit using tracker-only information (best measurement at low momenta

- Current CSCTT model developed in context of the Long barrel geometry

- CSCTT code is now in CVS

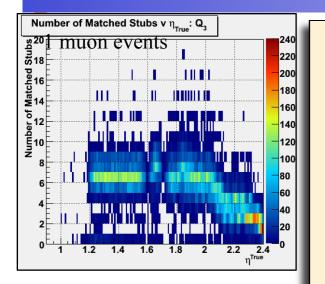

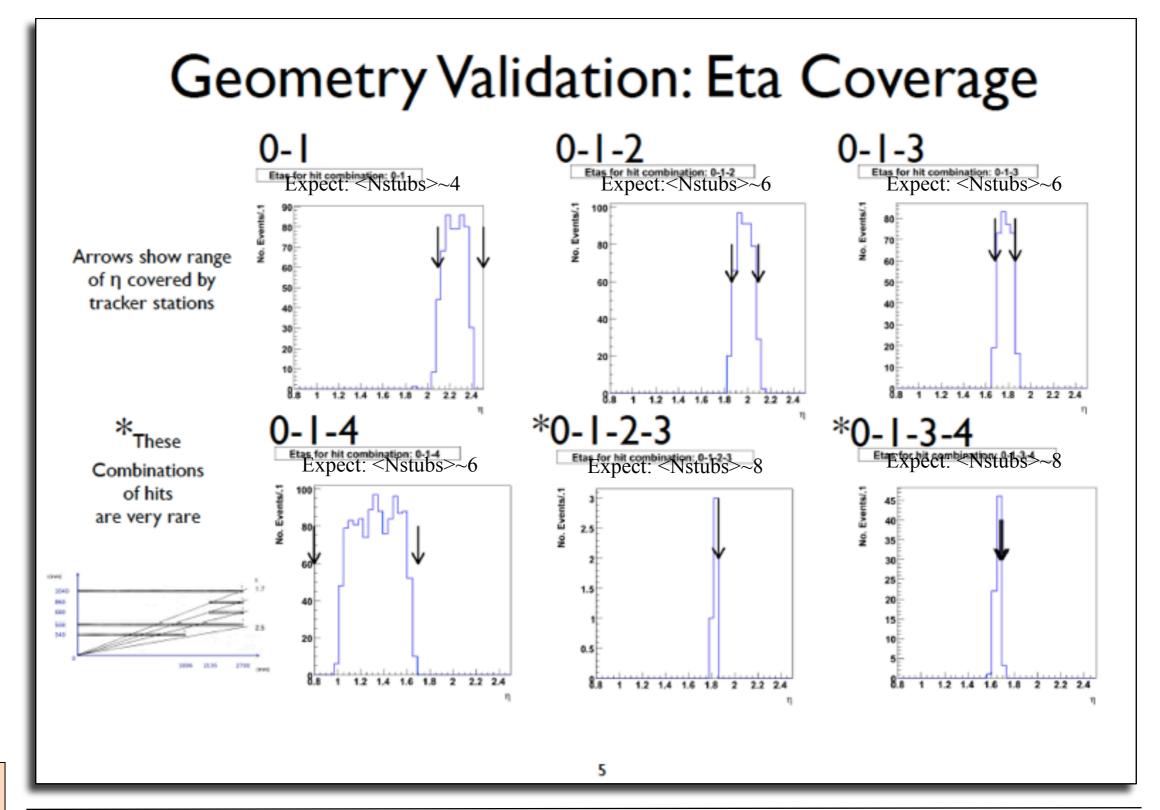

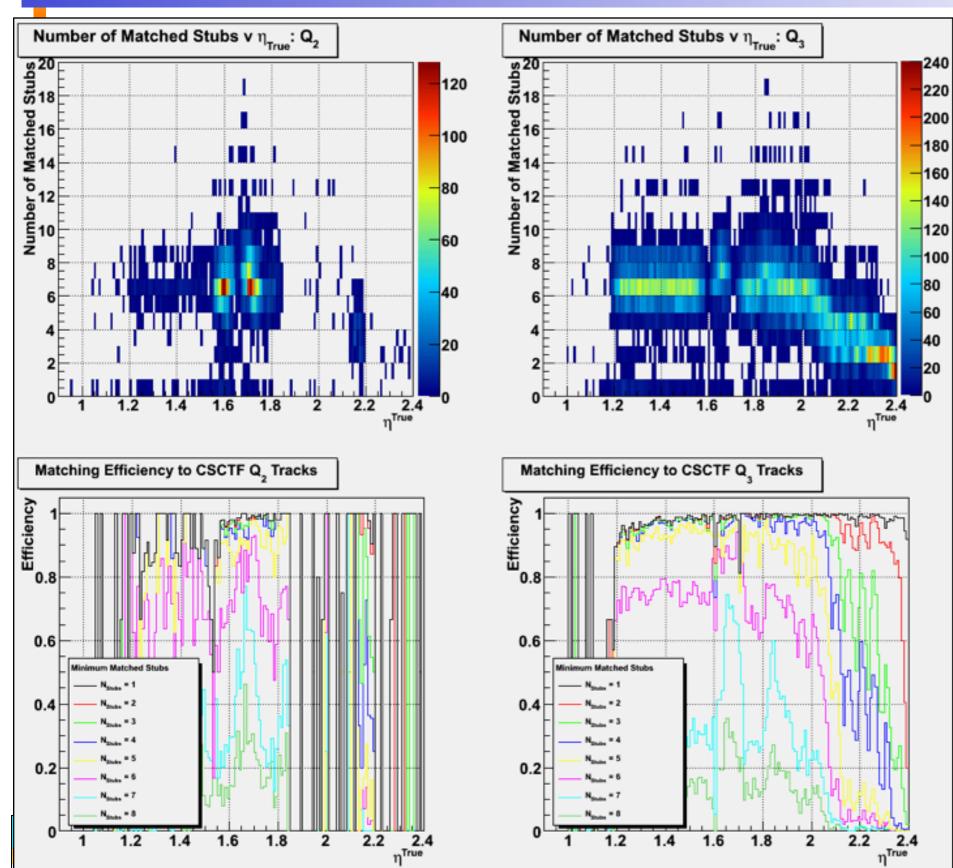

### Expected Eta Coverage (Longbarrel)

#### Matching Windows Efficiency (room for fine-tuning)

Here we see origin of inefficiency caused by Nstubs cut.

- (1) |Eta|>2.1 Nstubs is seen to drop to ~2 (expect 4)

- (2) Eta dependent switch in CSCTF-track quality assignment due to gap between inner and outer rings of ME2 and ME3 (matching windows are tuned for Q3 tracks). Q3:Q2 ~ 8:1 for 1 mu events (cf Q3:Q2 ~ 2:1 for MinBias)

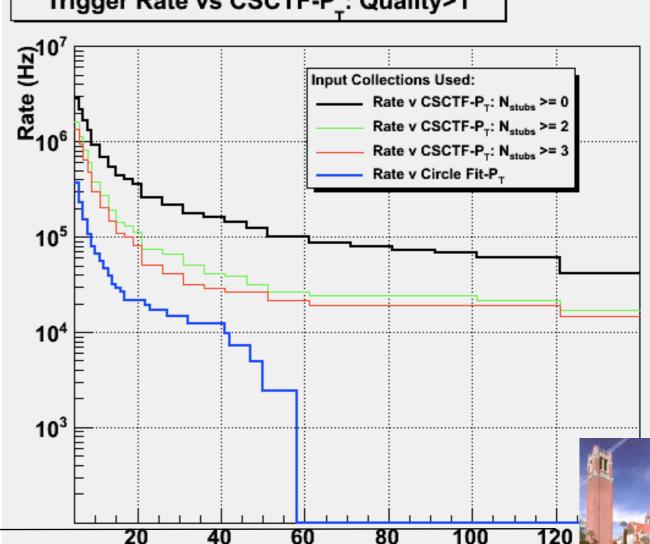

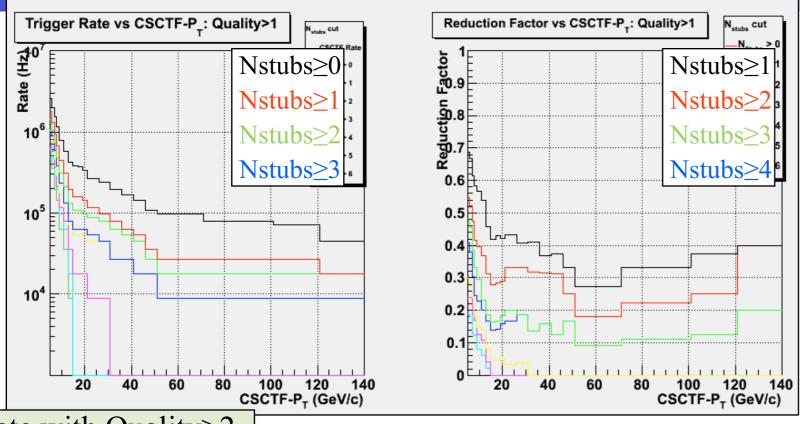

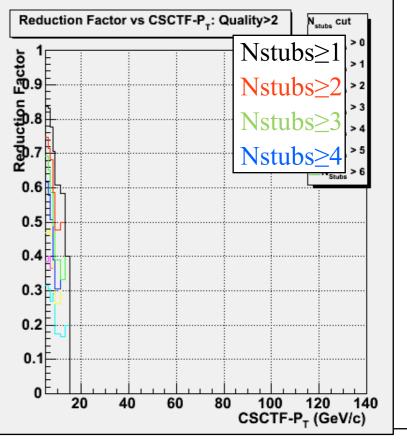

### Rate Reduction from stubs

Rate and relative reduction contours with Quality>1 CSCTF Tracks (versus Nstubs matching window cuts)

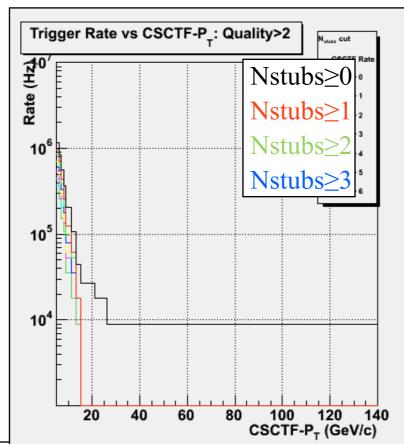

Rate with Quality>2 CSCTF Tracks

Rate reduction power is mostly related to CSCTF Quality. Improperly seeded windows miss underlying stubs. This can be a powerful weapon against CSCTF mis-measurement!

### P<sub>T</sub> with Beam spot drift

- Current algorithm takes filtered stub candidates and assigns  $P_T$  by finding effective  $\Delta\phi_{09}$  between tracker Layers

- Uses linear fit between  $1/P_T$  and  $\Delta \varphi_{09}$ , with (0,0,0) beamspot

- This algorithm can be re-tuned to accommodate off-center (not investigated yet)

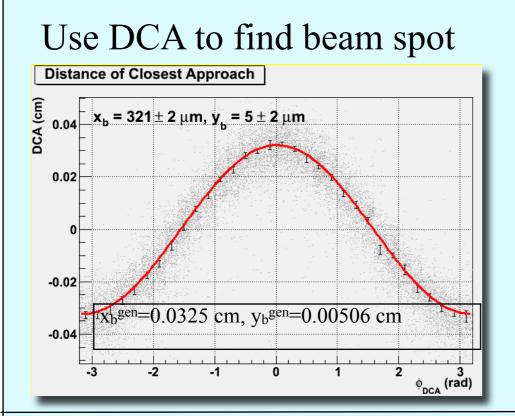

- Can we use the CSCTT model framework to accommodate beam spot drift?

- Take filtered stub candidates and use a 3-point circle fit to find P<sub>T</sub>

- Algorithm 1: Assume a known beam spot and use stubs available from two tracker Layers

- Algorithm 2: Assume unknown beam spot and use stubs available from three tracker Layers

- Can then use DCA to provide beam spot location

- Both algorithms fit two lines: L1 = Point<sub>i</sub> to Point<sub>i+1</sub> and L2 = Point<sub>i+1</sub> to Point<sub>i+2</sub> (points increasing in radius). Solve for the intersection of the two orthogonal lines which bisect L1 and L2

- Working with engineer to understand how we can implement algorithm in HW