### LHCb Upgrade

## .....from the point-of-view of electronics

### on behalf of the LHCb collaboration

## Many thanks to all my colleagues who provided material

### Reminder of Electronics Architecture

Review of electronics status Sub-detector specific Common projects

Outlook to installation

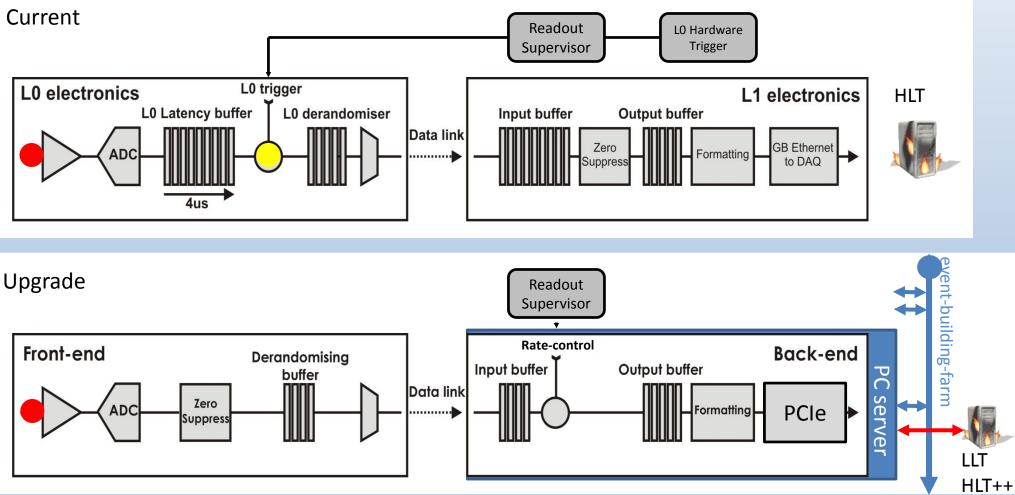

Upgrade philosophy

Remove existing LO hardware trigger (1 MHz)

Read out all detector data from all BXs @ 40 MHz

Triggering is 100% in software running in PC farm

$\Rightarrow$  New electronics & DAQ Upgrade installation in LS2

### Upgrade architecture

HCh

#### No 'front-end' trigger, Event rate to DAQ nominally 40 MHz

# Review of electronics status (non-exhaustive)

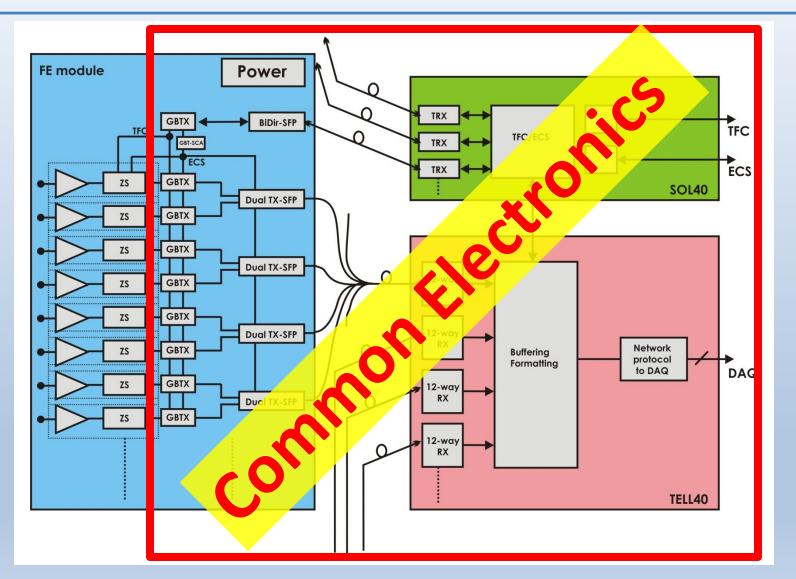

### Generic Implementation

#### Common front-end components

A huge thank you to the teams for the many man-years of development And to the management for the 'White Paper' R&D funding starting 2007 The LHCb upgrade would not be possible without this effort

#### Some words on ASIC technologies

Although not without problems, we have benefited hugely from changing 130nm CMOS technology in 2014

Fast & reliable turnaround Financial savings (& Multi-Layer-Mask option) Generous wafer quantities from Engineering Runs Sharing of blocks Good & stable radiation performance

Many thanks for the 'technology support' from CERN

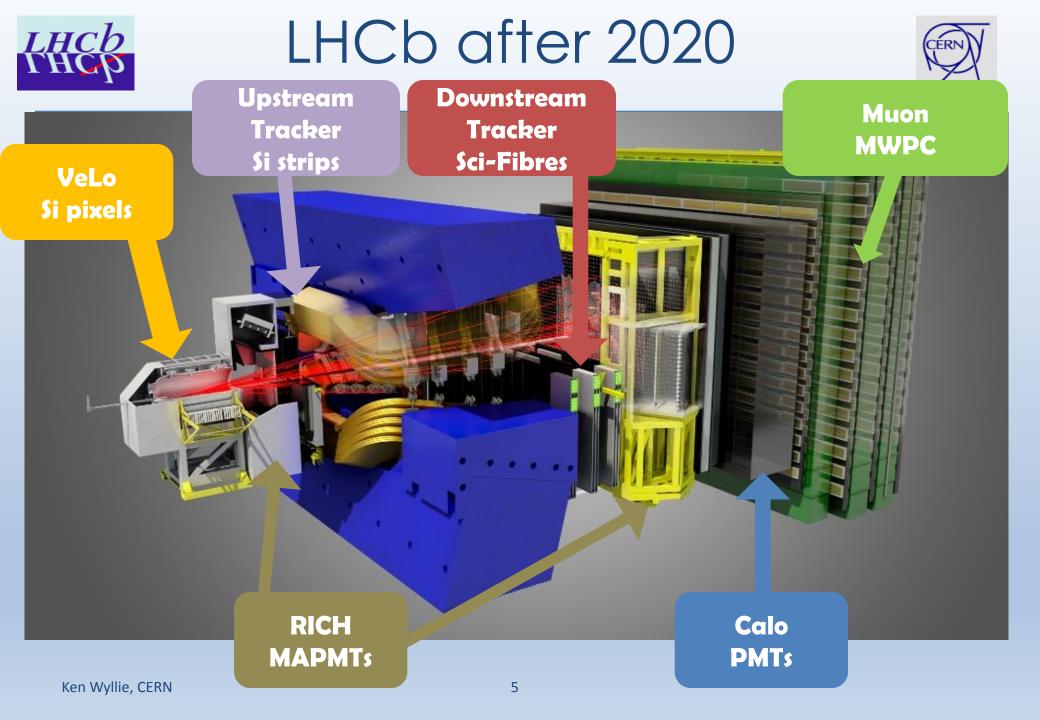

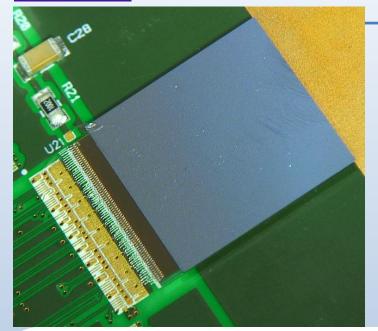

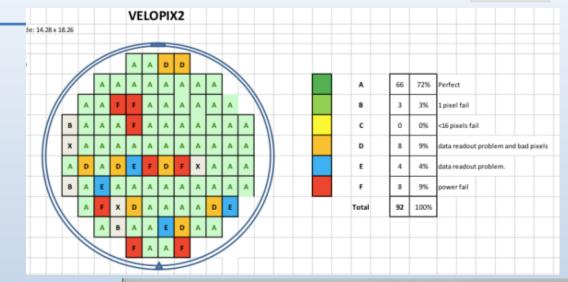

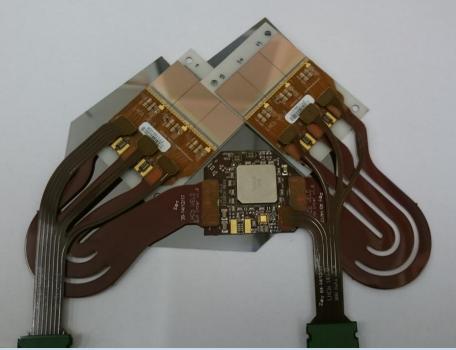

### VeLo (Si pixels)

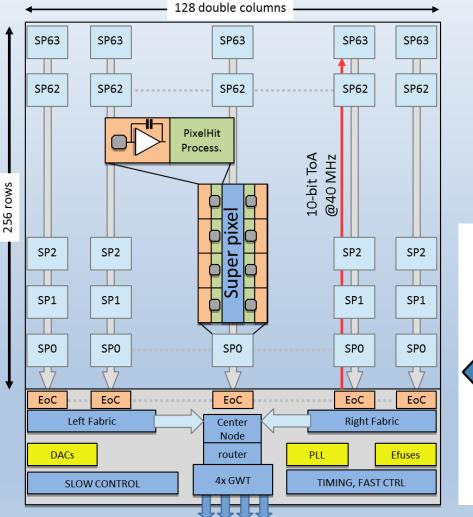

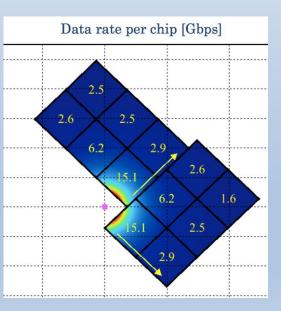

#### VeloPix readout chip Big challenge: high data rate

#### 4 x 5.12 Gbps

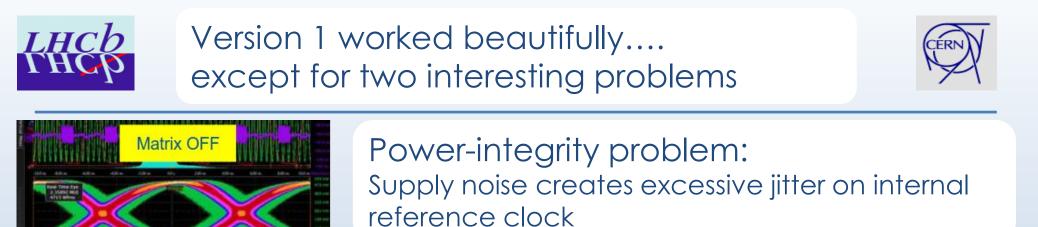

Version 2

(best phase)

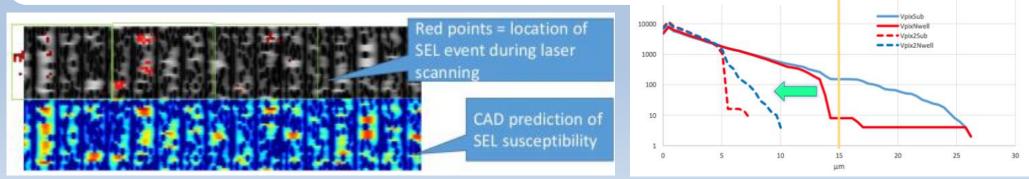

Single-event latch-up (30mA current increases) Observed with heavy-ions, confirmed with laser scanning Analysed in layout as function of well/sub-to-implant distance

Matrix ON

### Production started

Wafer-probing => bump-bonding

Pre-production of: hybrids, data-flex, power-distribution

Ken Wyllie, CERN

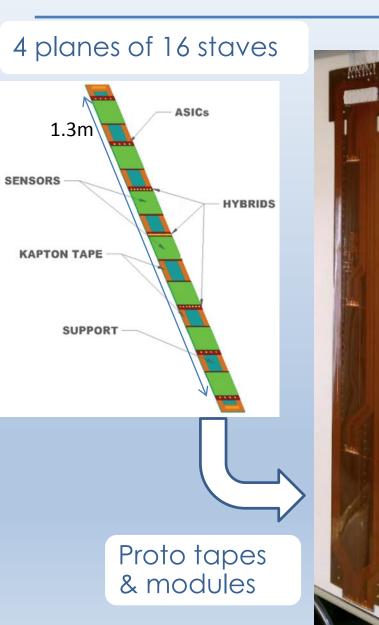

### Heb Upstream Tracker (Si strips) 🕅

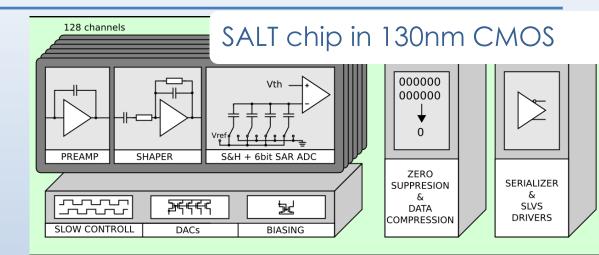

SALT: Fighting parasitic effects: New version under test

Other parts: Hybrids Flex tapes Data TX boards All tendering for production

**ð** 8,

44 (ABA)

เอโอโอโอโอโอโอโอโอ

**0 0**

15

TENENBARIO 1

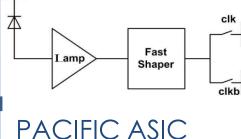

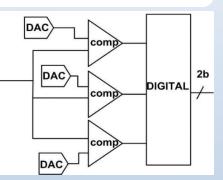

### SciFi Tracker (SiPMs)

#### SiPM arrays coupled to fibres, 250um pitch

clk

Gated integrator

Gated \_\_\_\_\_

IGLOO2 flash FPGA, forms clusters

Radiation tested at CHARM (mixed field) SEUs corrected by TMR No SELs No change in power consumption Speed degradation as predicted (not critical) Lose programmability quite early (~ 20 Gy)

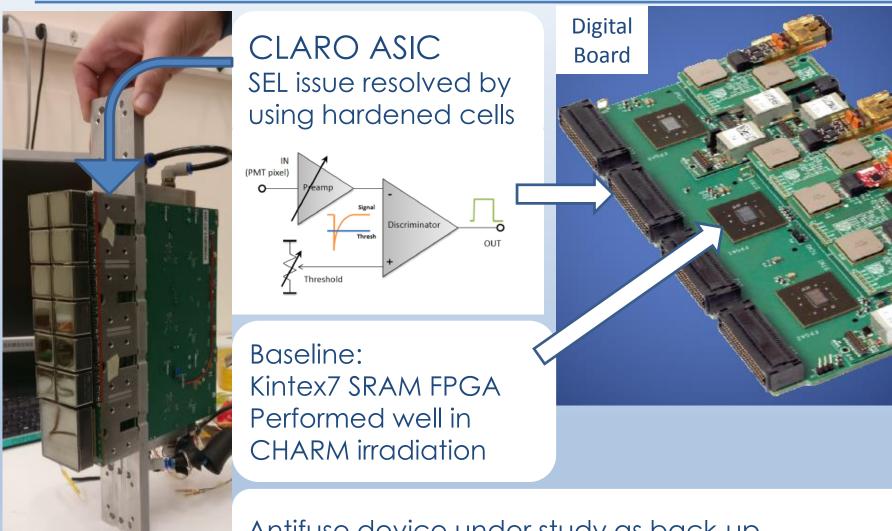

### RICH (MAPMTs)

Antifuse device under study as back-up Mezzanine approach to safeguard special components

Ken Wyllie, CERN

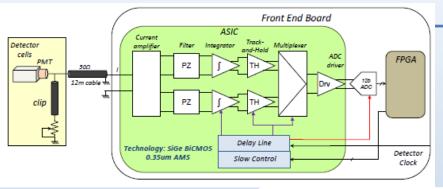

### Calorimeter (PMTs)

ICECAL ASIC Production testing ongoing

x 1

#### FEB: data TX IGLOO2 flash FPGAs

200

#### 3CU: fast/slow control

#### eLinks connect via crate backplane

x 16

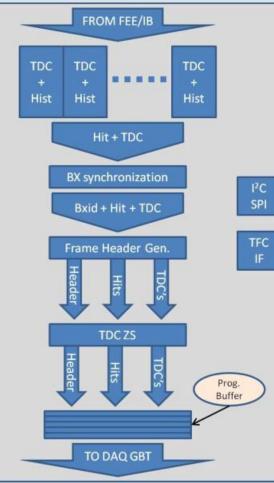

MUONS (MWPCs)

#### Re-use front-end ASICs on chambers

New readout modules

#### New TDC ASIC: fully digital, 1.56 ns resolution In production now

#### GBTX **nSYNC** VTTX VTRX GBT-SC DC-DC LVDS Converte Receivers

#### New control & calibration modules Based on IGLOO2

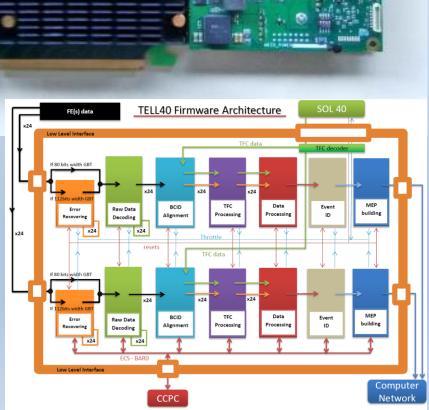

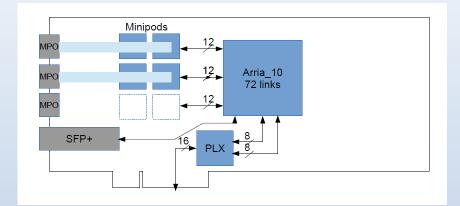

# Common module for data readout & controls: PCIe40

Challenges: new & complex FPGA, power & cooling

Production of ~ 670 modules starting now

See talk by J-P. Cachemiche on Wednesday

Different firmware recipes Centrally coordinated architecture + custom blocks per sub-system

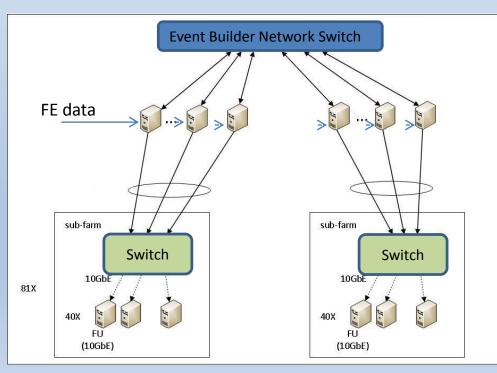

### Infrastructure

Farm of PC servers in data-centre on surface (ordered).

350m optical fibres bringing data up from cavern (tendering now).

Long-term BER testing continuing successfully.

Re-use existing power supplies (hoping for maintenance contract to continue.....) Re-use existing cabling (minimal additions) Re-use rack infrastucture

Sub-detectors implemented global architecture Heavy use of GBT, VL & DC-DC developments Most ASICs & front-end modules in production Widespread use of FPGAs in front-ends Infrastructure in preparation

On target for LS2.....

Discussion started on further upgrades

### Back-ups

### Motivation for upgrade

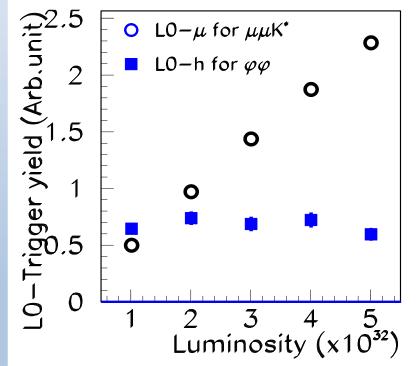

- At L = 2(+) x  $10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>, beyond 5 fb<sup>-1</sup>, statistics don't improve much

- Big statistical improvement if:

- increase L to  $2 \times 10^{33}$ , AND

- improve efficiency of trigger algorithms

BUT ..... with current L0 trigger:

rate & latency limited by electronics (1 MHz, 4  $\mu$ s) => saturation

#### BUT.... efficient trigger decisions require:

- long latencies (>> 4  $\mu$ s)

- computational power

- data from many (all) sub-detectors (momentum, impact parameter .....)

- $\Rightarrow$  Trigger in software

- $\Rightarrow$  Use data from every bunch crossing

- $\Rightarrow$  Upgrade electronics + DAQ <u>for LS2</u>

Architectural choices

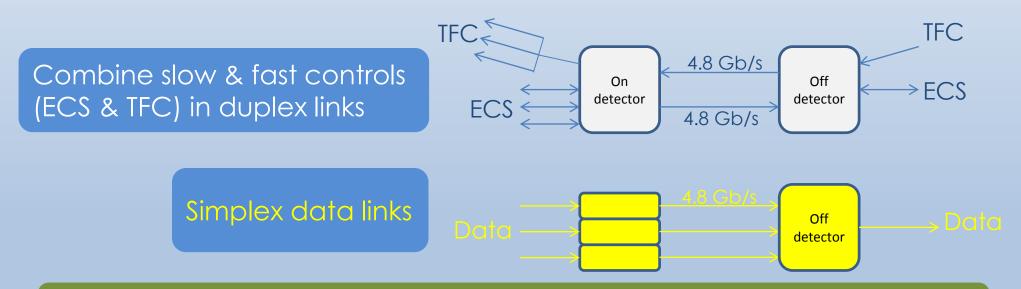

Data compression on front-end to minimize links: ~ 15,000 links (4.8 Gbit/s)

Flexibility: 4 of 6 sub-detectors will use FPGAs in front-ends

Backend is PCIe form factor in event-building farm

Ken Wyllie, CERN

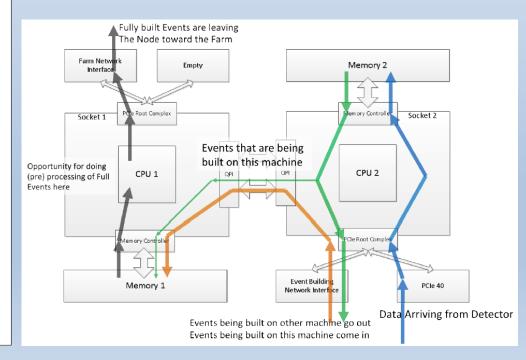

### Use PC memory & processors for event building

### Choose network interface at last moment (cheapest)

### All data in a box