#### **System's Performances in Bl**

Volker Schramm on behalf of the BI group

Special thanks to:

Enrico Bravin, Ewald Effinger, Rhodri Jones, Tom Levens, Georges Trad, William Viganò, Manfred Wendt, Christos Zamantzas

Volker Schramm BE-BI-BL volker.schramm@cern.ch

07/12/2017

- AFT statistics 2017 & previous years

- Faults analysis

- BI past and future efforts

- Conclusion

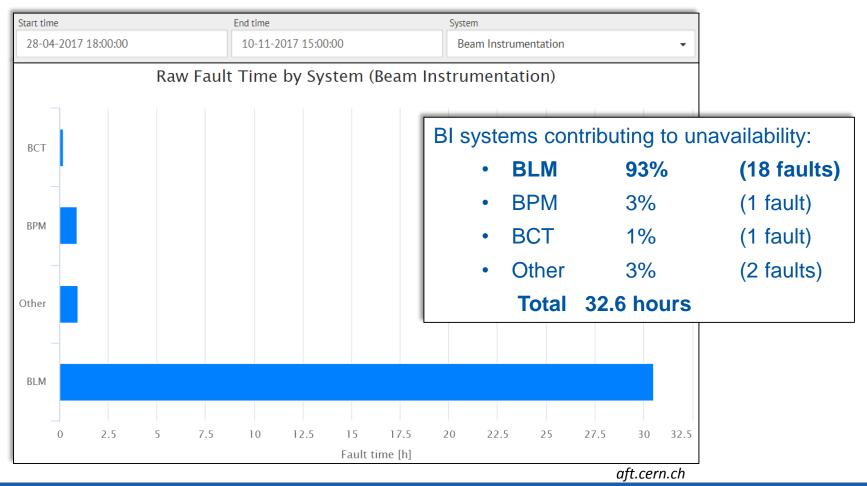

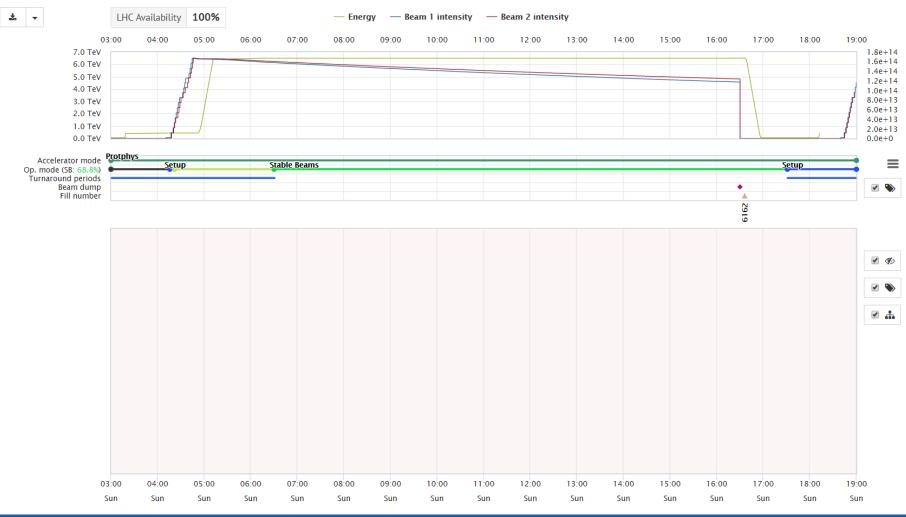

### AFT statistics - 2017

Registered 22 BI faults in 2017 which account to 32h LHC downtime

The main unavailability contributor is the Beam Loss Monitoring system

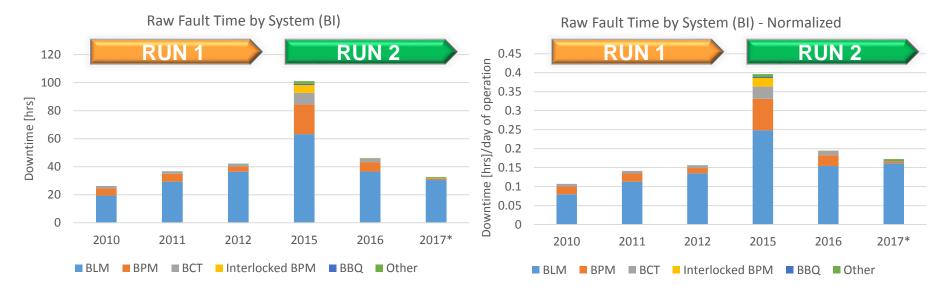

# AFT statistics – previous years

- BI availability increased for the 2<sup>nd</sup> year in a row (all systems!)

- 2017: Highest availability ever achieved for BPMs and BCTs

- Strong positive trend since 2015 (consistent AFT recording since 2015)

- The BLM normalized downtime is almost constant during 2016 and 2017

#### → Focus on the performance of the BLM

\*2017: 28/04 - 10/11

### Faults Analysis - BLM

|                                 | .017. |     |            |     |

|---------------------------------|-------|-----|------------|-----|

|                                 |       |     |            |     |

|                                 |       |     |            |     |

| Issue                           |       |     | 2017       |     |

|                                 | #     | %   | downtime   | %   |

| SEU (surface)                   | 4     | 22% | 04h 40m    | 15% |

| VME Power Supply Fail           | 1     | 6%  | 07h 47m    | 25% |

| Connection Lost: FESA/VME/CPU   | 1     | 6%  | 00h 04m    | 0%  |

| HV Power Supply Drop            |       |     |            |     |

| HV Power Supply Noise           |       |     |            |     |

| Sanity Error: Communication/VME | 4     | 22% | 01h 23m    | 5%  |

| Sanity Error: IC                | 1     | 6%  | 00h 29m    | 2%  |

| Sanity Error: LIC               |       |     |            |     |

| Sanity Error: SEM               | 3     | 17% | 13h 54m    | 46% |

| BLECF optical link issues       | 4     | 22% | 02h 13m    | 7%  |

| BLETC optical link issues       |       |     |            |     |

| Other optical link issues       |       |     |            |     |

| Other                           |       |     |            |     |

|                                 | 18    |     | 1d 06h 32m |     |

Detailed BLM faults in 2017:

Failed transformer

#### ~50% Sanity Check related faults

Failed Connectivity Test

## Faults Analysis - BLM

Detailed BLM faults of previous years: separate AFT & BI-BL accounting

- Throughout all years high number of Optical Link and Sanity Check related faults

- Own accounting helps to identify weak parts and to react earlier (e.g. Optical Link)

| Issue                           | 20         | 12 2015 |            | 15   | 2016       |      | 20         | 17   |

|---------------------------------|------------|---------|------------|------|------------|------|------------|------|

|                                 | AFT        | Jira    | AFT        | Jira | AFT        | Jira | AFT        | Jira |

| SEU (surface)                   | 3          | 3       | 2          |      | 1          |      | 4          |      |

| VME Power Supply Fail           | 1          | 1       |            |      | 1          |      | 1          |      |

| Connection Lost: FESA/VME/CPU   |            | 6       | 7          |      | 1          |      | 1          |      |

| HV Power Supply Drop            |            | 4       |            |      |            |      |            |      |

| HV Power Supply Noise           |            |         | 3          |      | 2          |      |            |      |

| Sanity Error: Communication/VME | 3          | 9       | 6          |      | 2          |      | 4          |      |

| Sanity Error: IC                |            | 3       | 1          |      |            |      | 1          |      |

| Sanity Error: LIC               |            | 6       |            |      |            |      |            |      |

| Sanity Error: SEM               | 5          | 10      | 5          |      | 4          |      | 3          |      |

| BLECF optical link issues       | 1          | 7       |            |      |            |      | 4          |      |

| BLETC optical link issues       | 3          | 11      | 1          |      | 4          |      |            |      |

| Other optical link issues       | 2          | 10      |            |      |            |      |            |      |

| Other                           | 2          |         | 2          |      | 1          |      |            |      |

|                                 | 25*        | 70      | 27         |      | 16         |      | 18         |      |

|                                 | 1d 12h 28m |         | 2d 15h 16m |      | 1d 12h 36m |      | 1d 06h 32m |      |

#### 3 main fault cases:

- Power supplies: Constant low failure rate

- SEMs (at the dump):

Constant high failure rate

Decreased, then in Run2 constant low failure rate

<sup>&</sup>gt; Optical links:

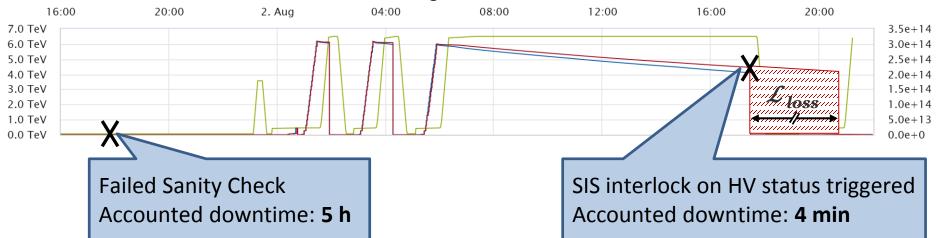

# Faults Analysis – 1 example

#### 2 BLM failures within 30 hours this August:

- System fault detected before it can lead to a dump (function fulfilled)

- *L*<sub>loss</sub>? → 'Equivalent to 5hours of scheduled operation'

- Fault lead to unscheduled beam dump (false dump)

- $\mathcal{L}_{loss}$ ?  $\rightarrow$  'Equivalent to >>4min of scheduled operation' ?

- How to quantify the luminosity loss?

- How to scale availability and luminosity?

# Faults Analysis – 1 example

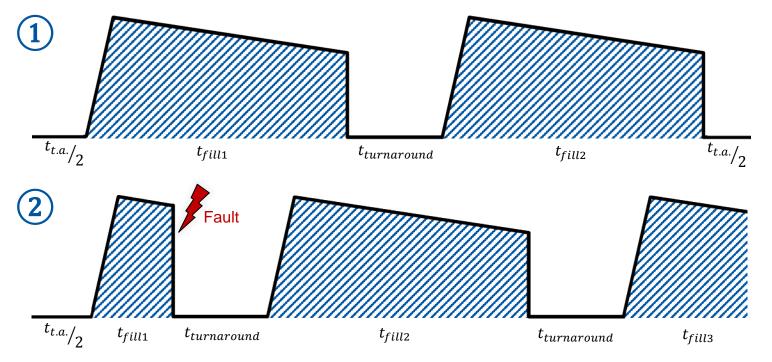

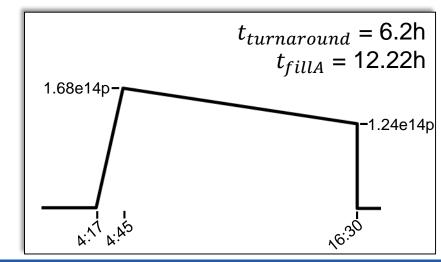

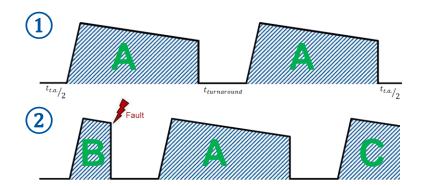

Example of two 12-hour fills as intended and the same scenario with a fault in the first fill:

By using intensities of a typical 12h13min fill at 6.5 TeV [03/09/2017,4:17am] as well as  $t_{turnaround} = 6.2h$  the integrated area below the fills is **≥14%** bigger for the 1<sup>st</sup> scenario

CFR

#### It is worth to invest in diagnostics and continuous system checks

### Past Efforts – LHC BLM

Channel with

amage Risk and

10pA check

Channel DR 10pA

0=4.5e-9 w=2.94e-7

Card

2.L.1

4.L.6

7.C.5

3.R.14

Channel with

Damage Risk and

Mission check

Channel DR M

Q=7.55e-7 w=1.26e-7

CF Ser

0488

0371 0328

0492

0642 0591

0803 0682

Channel with

Damage Risk

Channel DR Y

Q=4.24e-6 w=1.77e-9

TC Ser

16429131501618539521

10664523978582786561

10736581572621763841

9151314503787382017

and Yearly check

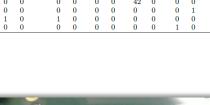

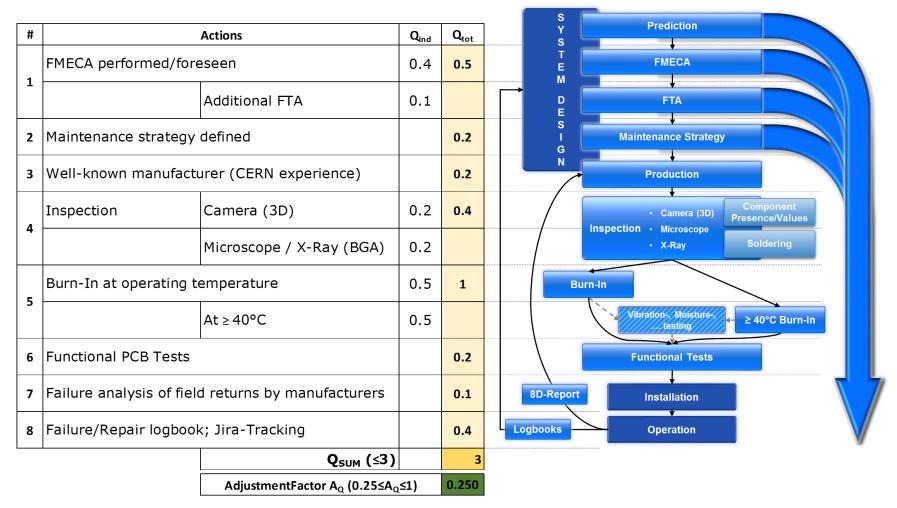

- **2005** > Dependability analysis:

- Prediction

- $\circ$  FMECA

- o FTA

- o Sensitivity Analysis

- 2008 > Redesign of the backend mezzanine

- **2012** > Preventive system fault analysis

- Daily automatic mails

- Jira failure logging

- **2013**  $\succ$  1<sup>st</sup> big maintenance intervention:

- Preventive exchanges: Cables, detectors, cards, fans

- Acquisition electronics modification & recalibration

- Clean-up: Optical adaptors, connectors

- Shuffle of optical links & firmware modification

- **2017** > Dependability analysis update (PhD)

Damage Risl

01 DR

0=502e-6w=436e

Digital FEE with

Damage Risk and

Mission check

DigitalFEE\_DR\_M

Q=193e-8 w=3 22e-9

CS Ser

1743793781554746342

16861477063165457409

14267403677825781249

7854277808467274753

BEE with

Logging check

BEE DR I

Q=515a-13 w=1.85a-9

Optical link errors

CRC COMP

BEE with Damage

BEE DR M

=924e-11 w=1.54e-1

Damage Risk and Risk and Mission

Crate with

Damage Risk and

Logging check

Crate DR

Q=1.52a-12 v=5.89a-

LK1 Err

BABABAB

Gianluca Guaglio, PhD thesis, 2005

LK2 Err

Crate with

Damage Risk and

Mission check

0=6.74e-9 w=1.12e-9

LK1 Lost

To run with Qave

igital FEE with

Damage Risk

and 10pA check

DichAFEE DR. 10pf

Q=3.45a-11 w=2.24a-9

(LS1)

Level

Level

LK2 Lost

FID COME

A B

0

0 0

0 0

0

### Past Efforts – LHC BLM

Ongoing PhD to study and improve the LHC BLM system. Results will be projected to enhance the injector's upgrade and the new VFC processing card:

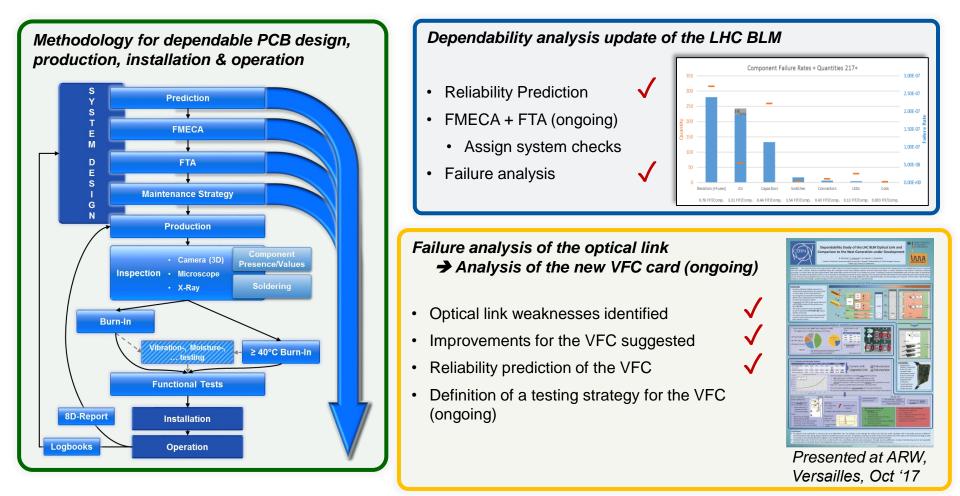

# Future Efforts – VFC upgrade

Installation of the VFC card to upgrade the surface processing card

- Eliminate system weaknesses

- Adding extra functionalities

- Testing and qualification prior to installation ! Demonstrate low failure rate !

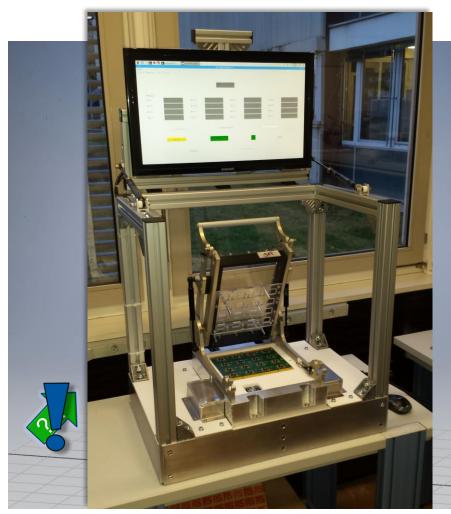

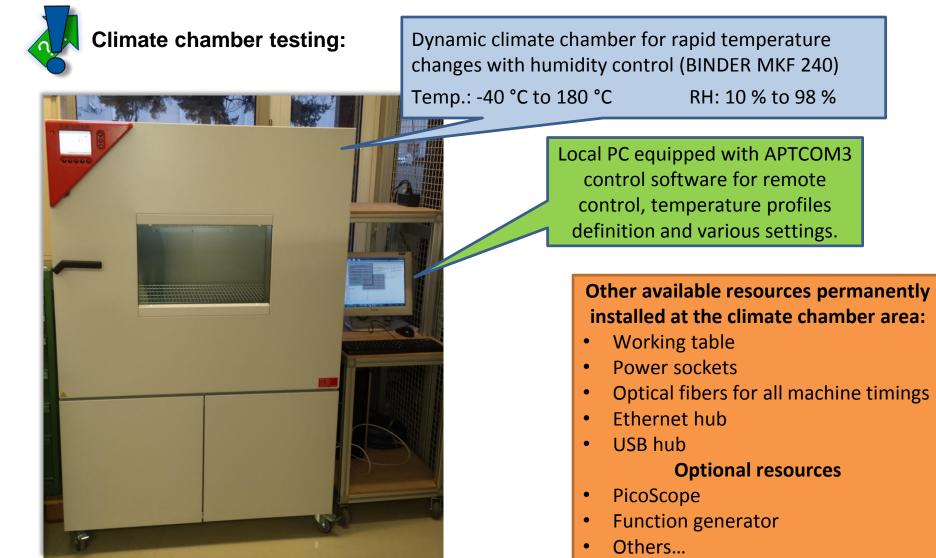

## **Future Efforts – Testing**

#### Functional and reliability tests:

Functional tester for the VFC-HD card

Reliability tester of VFC power supplies

# **Future Efforts – Testing**

## Future Efforts – Sanity Check

Optimising the Sanity Check sequence:

- Merge 5 sequence steps into 4

- Enable to perform checks of only 1 group

- Upgrades of the code in the long term

| 🍝 Status Appli                                            | cation      |                                  |             |          |                      |              |          |         | -          |          | Х   |

|-----------------------------------------------------------|-------------|----------------------------------|-------------|----------|----------------------|--------------|----------|---------|------------|----------|-----|

| Beam monitor                                              |             |                                  |             |          |                      |              |          |         |            |          |     |

| Accelerator N                                             | lode:       |                                  |             |          |                      | Beam 1 Pre   | sent:    |         |            |          |     |

| Beam Mode:                                                |             |                                  |             |          |                      |              |          |         |            |          |     |

| beam woue.                                                |             |                                  |             |          |                      | Dedili 2 Pre | sent.    |         |            |          |     |

|                                                           |             |                                  |             |          | <b>Global Status</b> |              |          |         |            |          |     |

| Check being run at the moment 06.12.2017 10:47:07         |             |                                  |             |          |                      |              |          |         |            |          |     |

|                                                           | Checks      | s connected to BIS Expert checks |             |          |                      |              |          |         | BIS team   | m        |     |

|                                                           | MCS         | Sanity                           | Checks      |          |                      |              |          |         |            |          |     |

|                                                           |             |                                  | Internal    |          |                      |              |          |         |            | External |     |

| Crates                                                    | Consistency | Connectivity                     | Beam Permit | CFC_TEST | RST_DAC              | RST_GOH      | RST_FPGA | STOP_HV | MANUAL_CTR | Beam Per | mit |

| SR1.L                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR1.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR1.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR2.L                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR2.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR2.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR2.I                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR3.L                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR3.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR3.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SX4.L                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SX4.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SX4.R<br>SR5.L                                            |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR5.L<br>SR5.C                                            |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR5.C<br>SR5.R                                            |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR5.R<br>SR6.L                                            |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR6.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR6.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR7.L                                                     |             |                                  |             |          |                      |              |          |         |            |          | -   |

| SR7.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR7.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR7.E                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR8.L                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR8.C                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR8.R                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| SR8.I                                                     |             |                                  |             |          |                      |              |          |         |            |          |     |

| Legend: OK <12h OK Block BP BP removed Under Test No Data |             |                                  |             |          |                      |              |          |         |            |          |     |

- → 20% time saving

- → Up to **75%** time saving

#### **Checks sequence:**

- 1. Each point center crate

- 2. Each point left crate

- 3. Each point right crate

- 4. Injection crate

- 5. Extra crate in point 7

#### $\rightarrow$ Merge steps 4 and 5

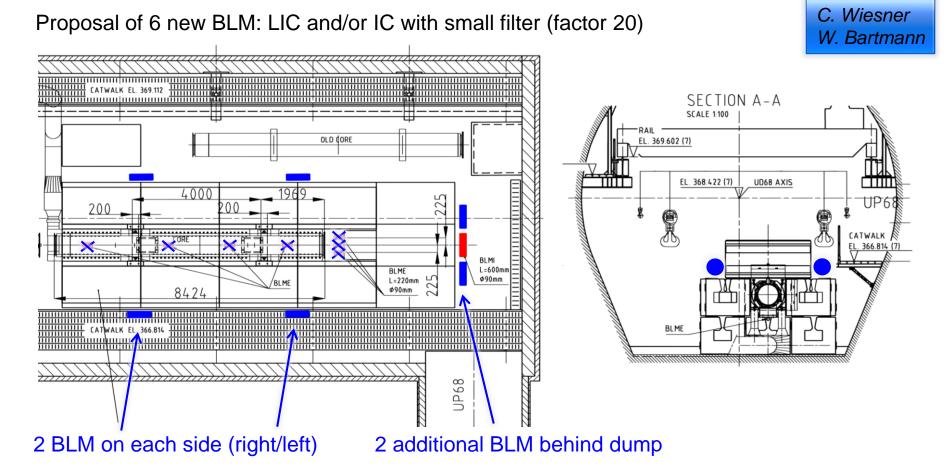

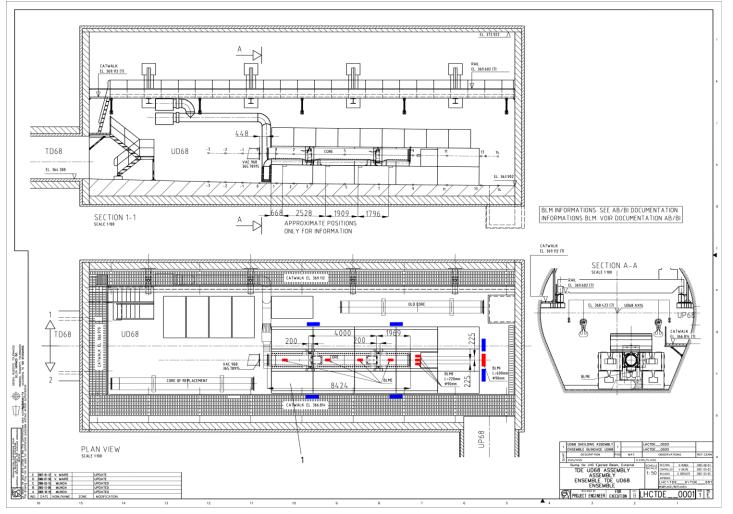

# Future Efforts – Dump Upgrade

$\rightarrow$  Exact positions have been defined with ABT. Radiation tolerant cabling to be added locally.

#### Conclusion

- In 2017 a <u>better availability</u> was achieved than in previous years

- Very strong performance of BCTs and BPMs

- Future efforts need to focus on the BLM which contributed >90% of BI downtime

- Various measures are put in place:

- Constant maintenance and exchange of less reliable systems

- Preventive system fault analysis & failure logging

- System upgrades which include:

- Functional tests before installation

- Component reliability testing

- System burn-in-/reliability testing

- Diagnostics and performing system checks can reduce availability <u>but</u> can in the same way increase luminosity

#### Thank you for your attention

www.cern.ch

Calculation of the ~ 14% reduced luminosity:

•

$$\mathcal{L}_{loss} = 2A - (A + B + C) = A - B - C$$

•

$$t_{total} = 2 * 12h + 2 * 6.2h = 36.4h$$

•

$$t_C = 36.6h - 12h - 2.5 * 6.2h - t_B \rightarrow t_B + t_C = 9.1h \rightarrow \text{Highest } \mathcal{L} \text{ for } t_B = t_C = 4.55h$$

•

$$A = \frac{0.46h*1.68e14p}{2} + 11.75h*1.24e14p + \frac{11.75h*0.44e14p}{2} = 17.55e14h*p$$

•

$$B = C = \frac{0.46h + 1.68e14p}{2} + 4.08h + 1.24e14p + \frac{4.08h + 0.44e14p}{2} = 6.35e14h + p$$

• (1)

$$2A = 35.1e14$$

(2)  $A + B + C = 30.24e14$

$$> "\mathcal{L}_{loss}" = 4.85e14 \qquad \approx 14\%$$

#### Example of a 12-hour fill at 6.5 eV:

#### Methodology PCB design:

#### Dump Region with BLM:

C. Wiesner W. Bartmann