#### Introduction to Field Programmable Gate Arrays

Hannes Sakulin CERN / EP-CMD

ESIPAP school, Archamps, France, 27th February, 2018

# What is a **F**ield **P**rogrammable **G**ate **A**rray ? ... a quick answer for the impatient

- An FPGA is an integrated circuit

- Mostly digital electronics

- An FPGA is programmable in the in the field (=outside the factory), hence the name "field programmable"

- Design is specified by schematics or with a hardware description language

- Tools compute a programming file for the FPGA

- The FPGA is configured with the design (gateware / firmware)

- Your electronic circuit is ready to use

With an FPGA you can build electronic circuits ... ... without using a bread board or soldering iron ... without plugging together NIM modules ... without having a chip produced at a factory

# Outline

- Quick look at digital electronics

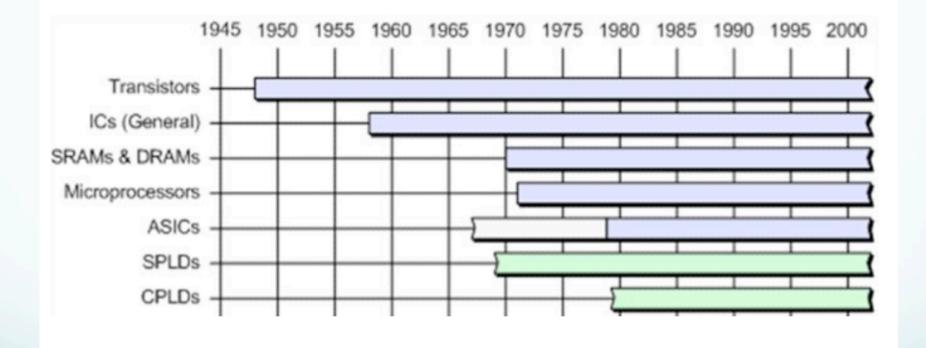

- Short history of programmable logic devices

- FPGAs and their features

- Programming techniques

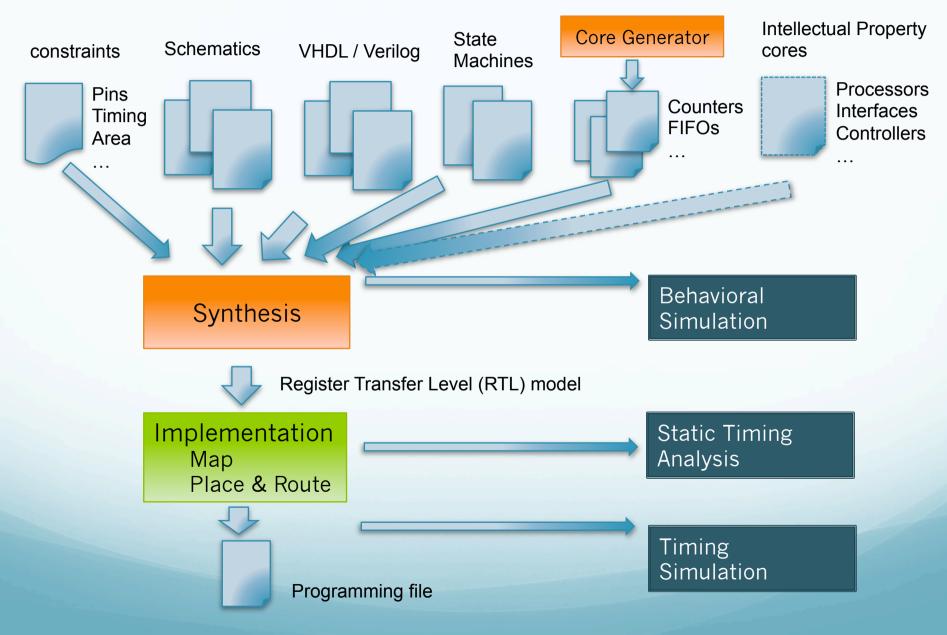

- Design flow

- Example Applications in the Trigger and DAQ domain

# Acknowledgement

Parts of this lecture are based on material by Clive Maxfield, author of several books on FPGAs. Many thanks for his kind permission to use his material!

#### Re-use

Re-use of the material is permitted only with the written authorization of both Hannes Sakulin (<u>Hannes.Sakulin@cern.ch</u>) and Clive Maxfield.

#### **Digital electronics**

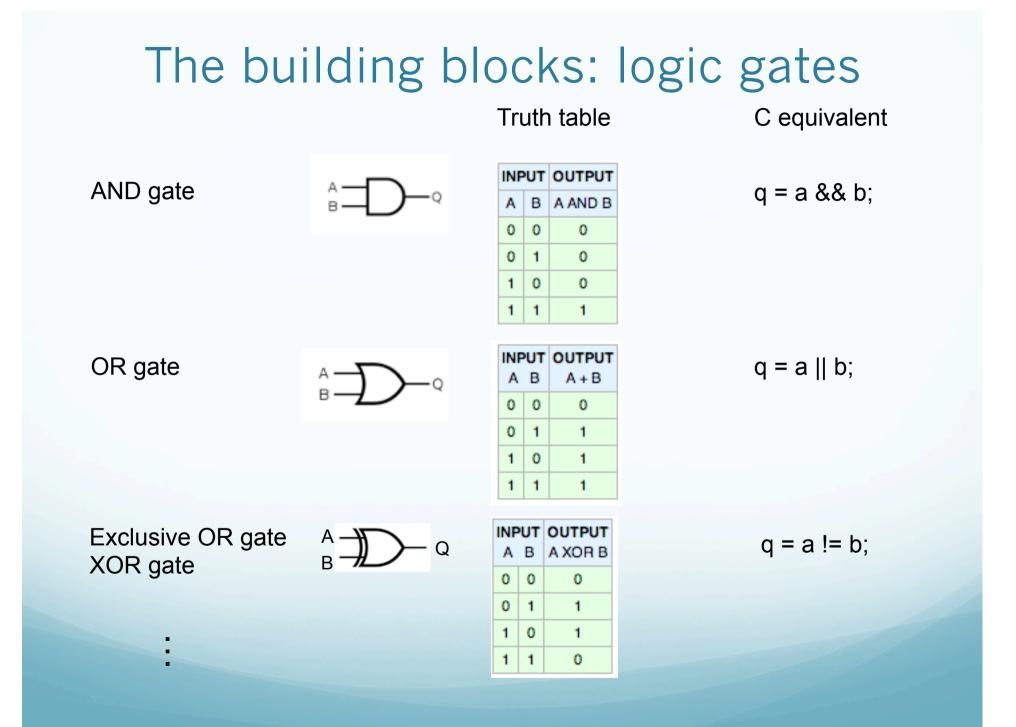

#### Combinatorial logic (asynchronous)

Outputs are determined by Inputs, only

Example: Full adder with carry-in, carry-out

| Α | В | <b>C</b> <sub>in</sub> | S | C <sub>out</sub> |

|---|---|------------------------|---|------------------|

| 0 | 0 | 0                      | 0 | 0                |

| 1 | 0 | 0                      | 1 | 0                |

| 0 | 1 | 0                      | 1 | 0                |

| 1 | 1 | 0                      | 0 | 1                |

| 0 | 0 | 1                      | 1 | 0                |

| 1 | 0 | 1                      | 0 | 1                |

| 0 | 1 | 1                      | 0 | 1                |

| 1 | 1 | 1                      | 1 | 1                |

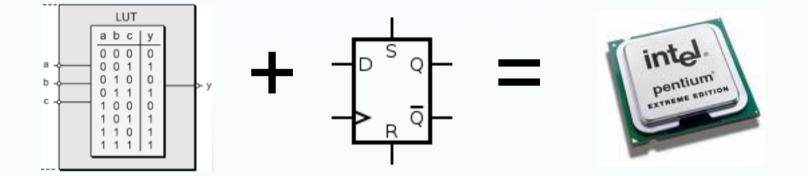

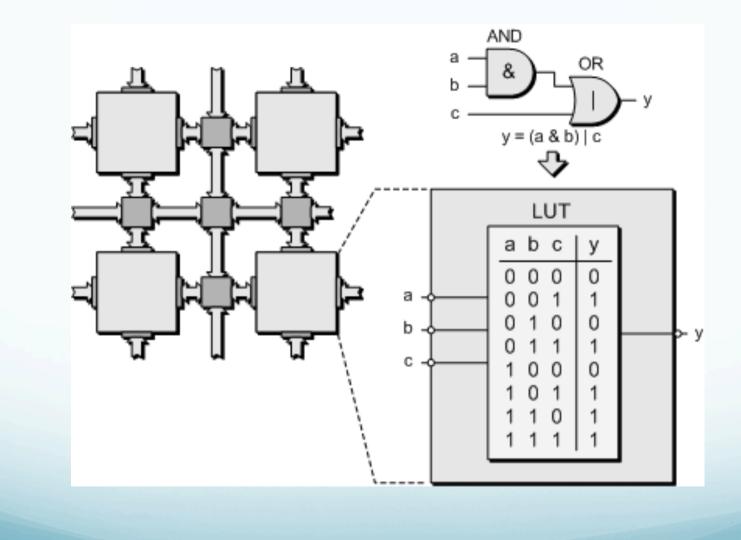

Combinatorial logic may be implemented using Look-Up Tables (LUTs)

LUT = small memory

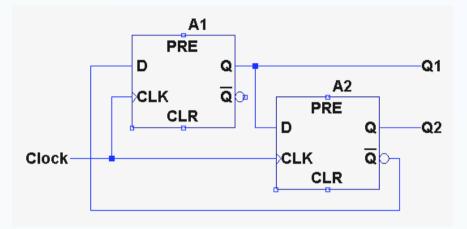

#### (Synchronous) sequential logic

Outputs are determined by Inputs and their History (Sequence) The logic has an internal state

2-bit binary counter

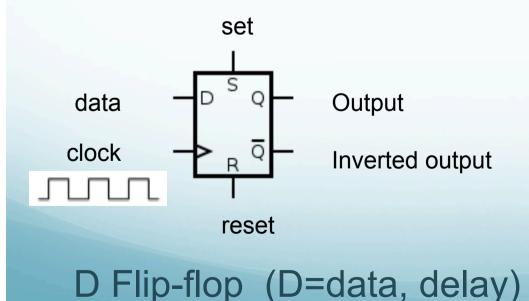

#### D Flip-flop:

samples the data at the rising (or falling) edge of the clock

The output will be equal to the last sampled input until the next rising (or falling) clock edge

# Synchronous sequential logic

Using Look-Up-Tables and Flip-Flops any kind of digital electronics may be implemented

Of course there are some details to be learnt about electronics design ...

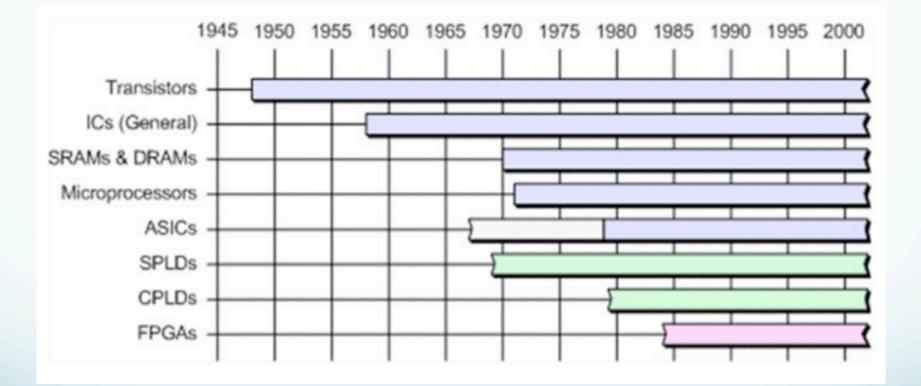

Programmable digital electronics

# Long long time ago ...

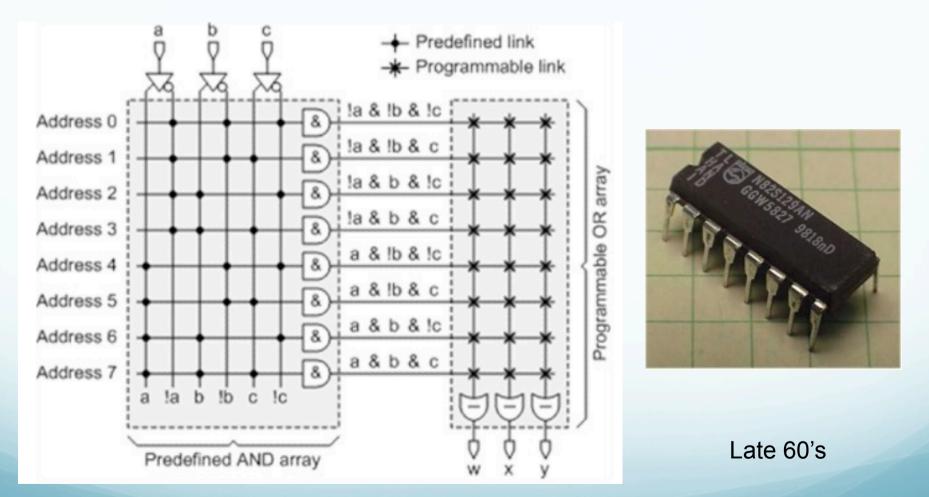

#### Simple Programmable Logic Devices (sPLDs) a) Programmable Read Only Memory (PROMs)

**Unprogrammed PROM (Fixed AND Array, Programmable OR Array)**

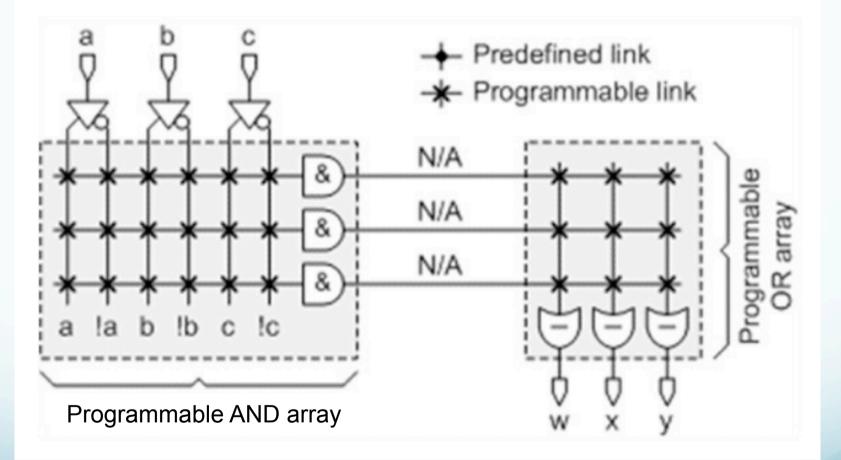

#### Simple Programmable Logic Devices (sPLDs) b) Programmable Logic Arrays (PLAs)

**Unprogrammed PLA (Programmable AND and OR Arrays)**

Most flexible but slower

1975

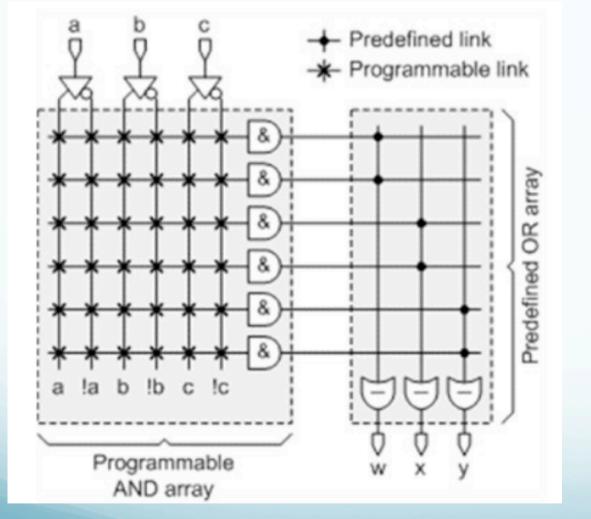

#### Simple Programmable Logic Devices (sPLDs) c) Programmable Array Logic (PAL)

**Unprogrammed PAL (Programmable AND Array, Fixed OR Array)**

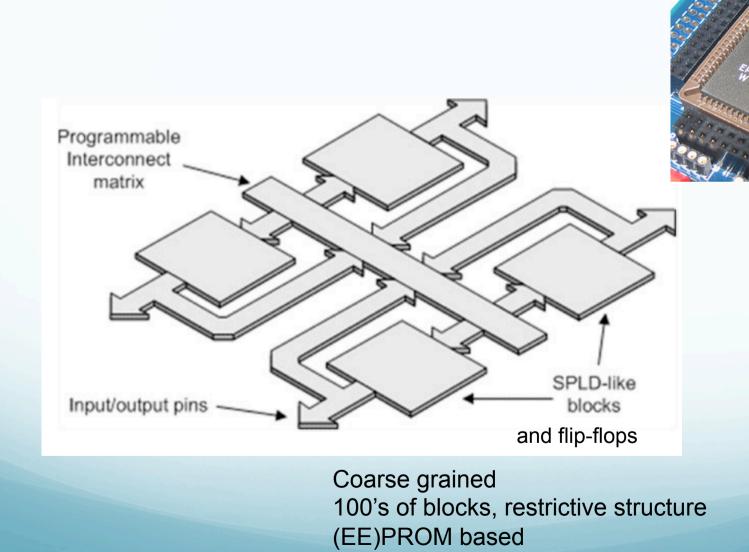

# Complex PLDs (CPLDs)

Millin

FPGAs ...

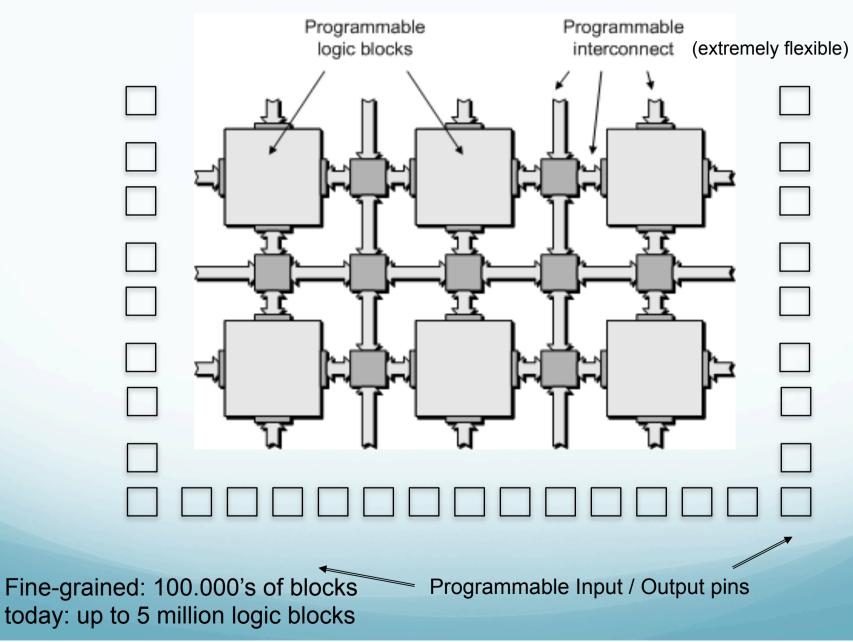

#### FPGAs

#### LUT-based Fabrics

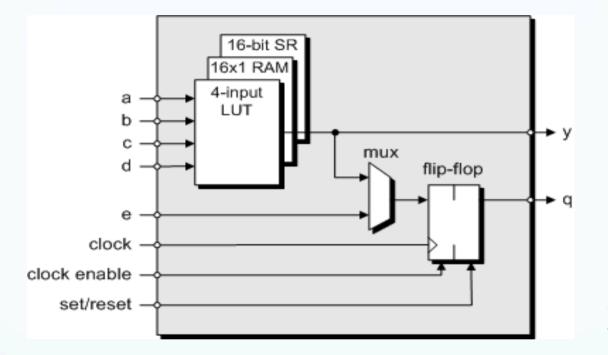

# Typical LUT-based Logic Cell

Xilinx: logic cell, Altera: logic element

- LUT may implement any function of the inputs

- Flip-Flop registers the LUT output

- May use only the LUT or only the Flip-flop

- LUT may alternatively be configured a shift register

- Additional elements (not shown): fast carry logic

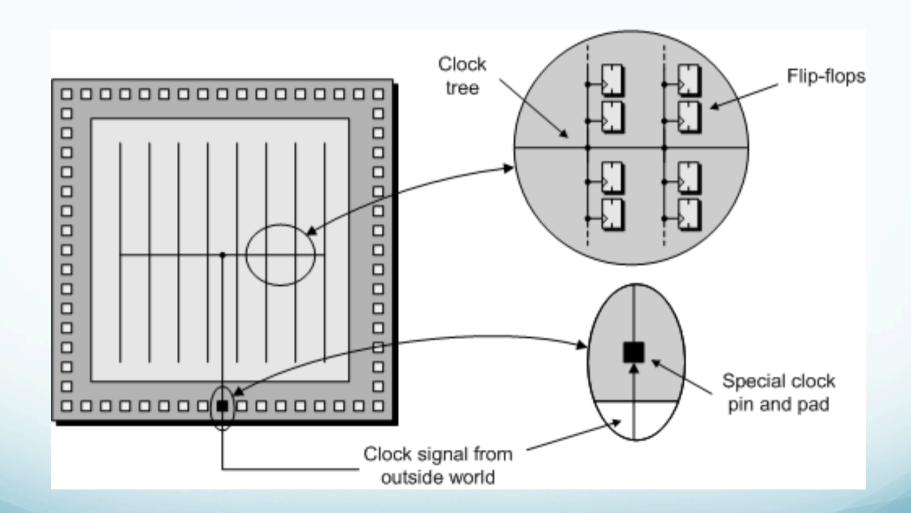

#### **Clock Trees**

Clock trees guarantee that the clock arrives at the same time at all flip-flops

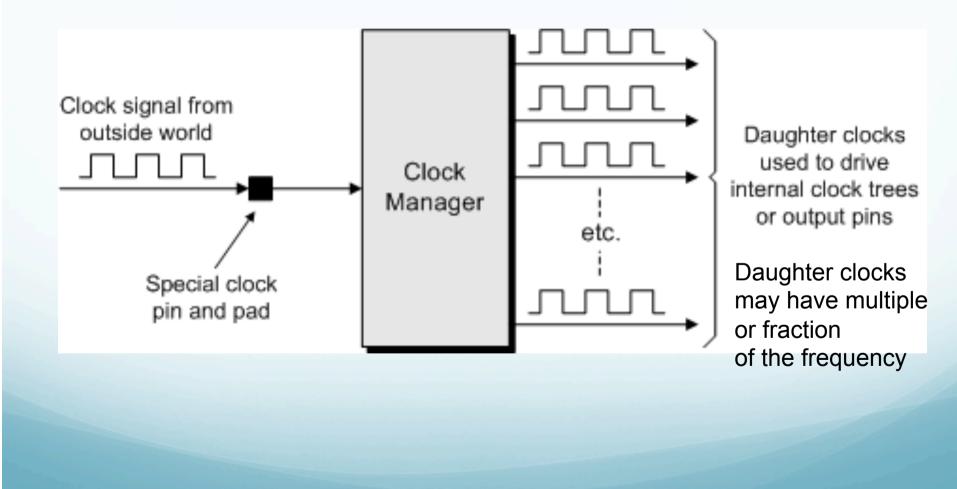

# **Clock Managers**

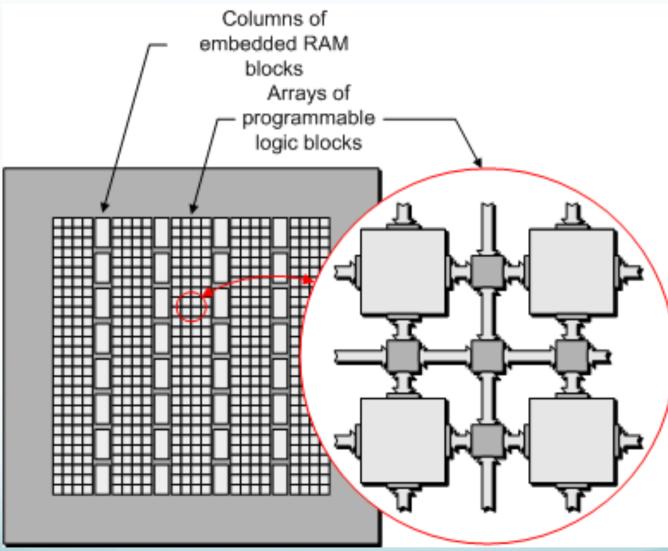

#### Embedded RAM blocks

Today: Up to ~500 Mbit of RAM

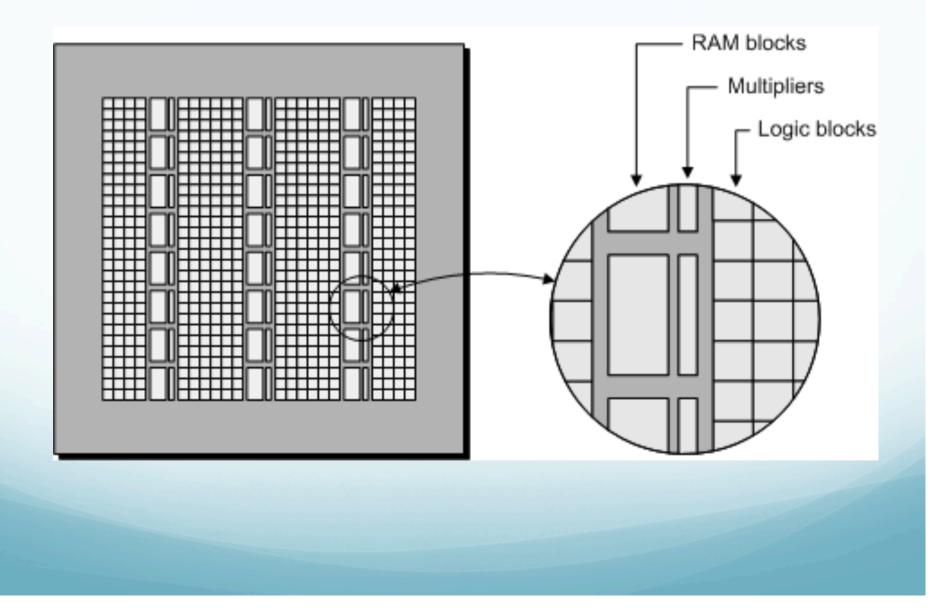

#### Embedded Multipliers & DSPs

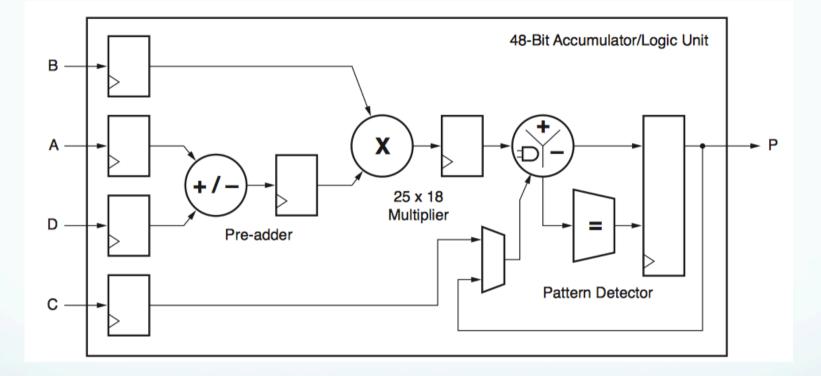

#### Digital Signal Processor (DSP)

DSP block (Xilinx 7-series) Up to several 1000 per chip

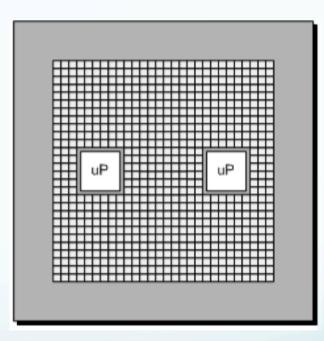

#### Soft and Hard Processor Cores

- Soft core

- Design implemented with the programmable resources (logic cells) in the chip

- Hard core

- Processor core that is available in addition to the programmable resources

- E.g.: Power PC, ARM

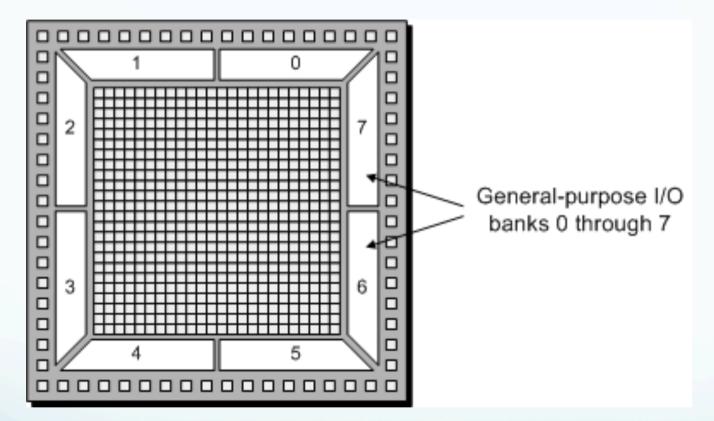

#### General-Purpose Input/Output (GPIO)

Today: Up to 1200 user I/O pins Input and / or output Voltages from (1.0), 1.2 .. 3.3 V Many IO standards Single-ended: LVTTL, LVCMOS, ... Differential pairs: LVDS, ...

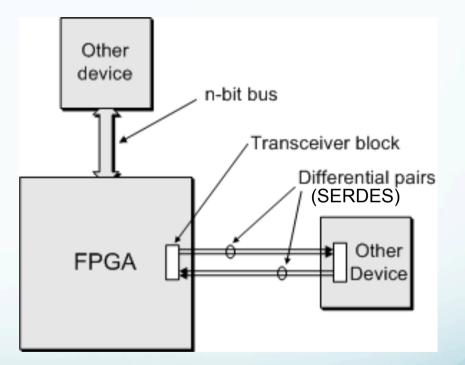

#### High-Speed Serial Interconnect

- Using differential pairs

- Standard I/O pins limited to about 1 Gbit/s

- Latest serial transceivers: typically 10 Gb/s, 13.1 Gb/s,

- up to 32.75 Gb/s

- up to 56 Gb/s with Pulse Amplitude Modulation (PAM)

- FPGAs with multi-Tbit/s IO bandwidth

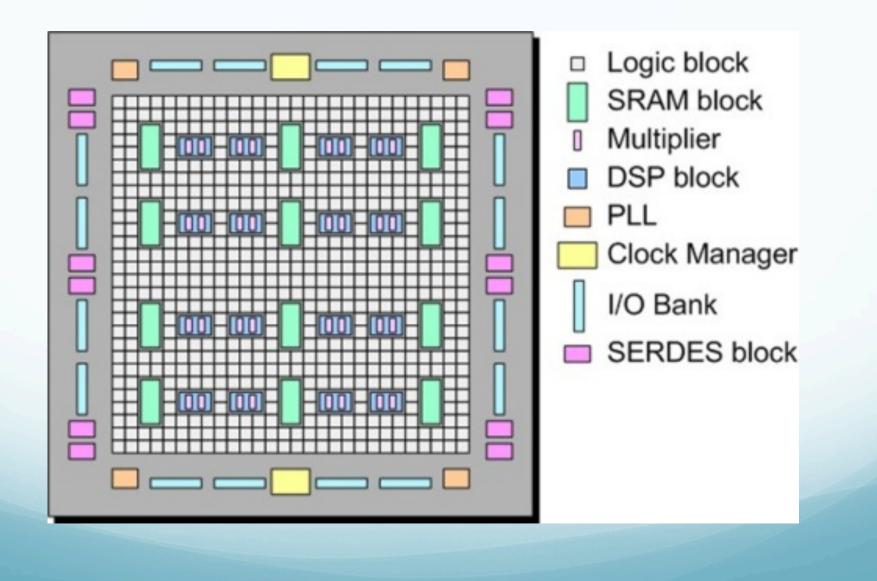

#### Components in a modern FPGA

#### **Programming techniques**

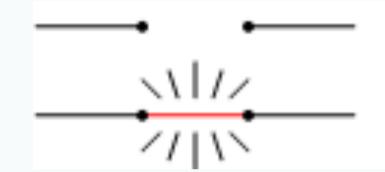

# Fusible Links (not used in FPGAs) Unprogrammed link \\*\\* Programmed link 2/11

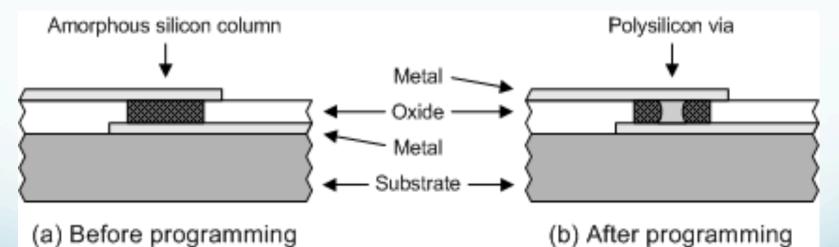

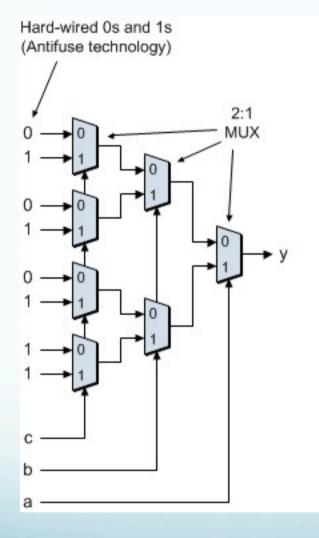

# Antifuse Technology

Unprogrammed link

Programmed link

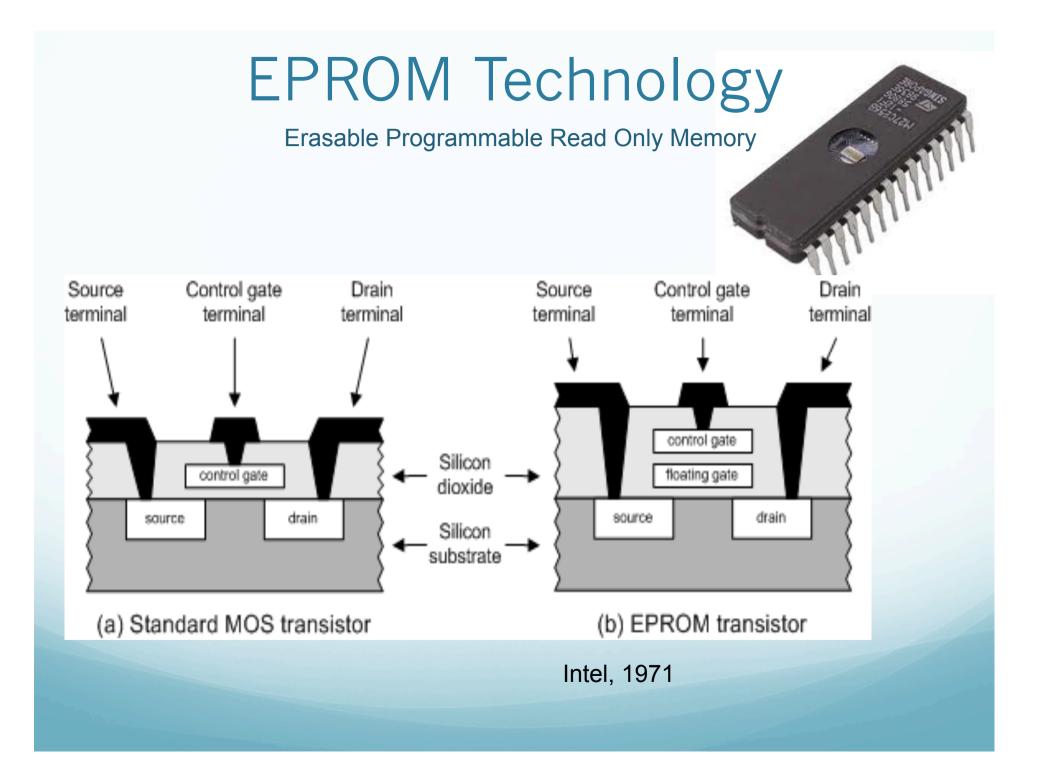

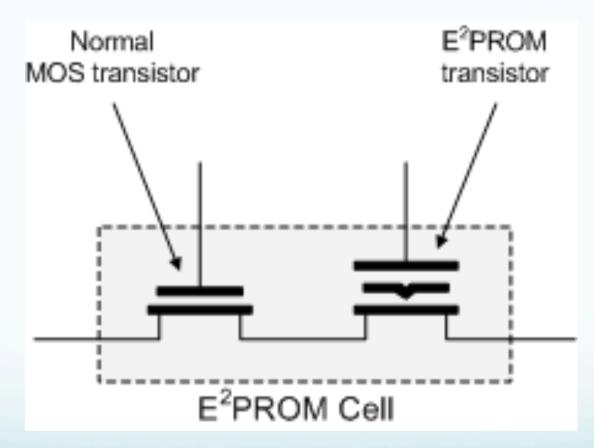

#### **EEPROM and FLASH Technology**

Electrically Erasable Programmable Read Only Memory

EEPROM: erasable word by word FLASH: erasable by block or by device

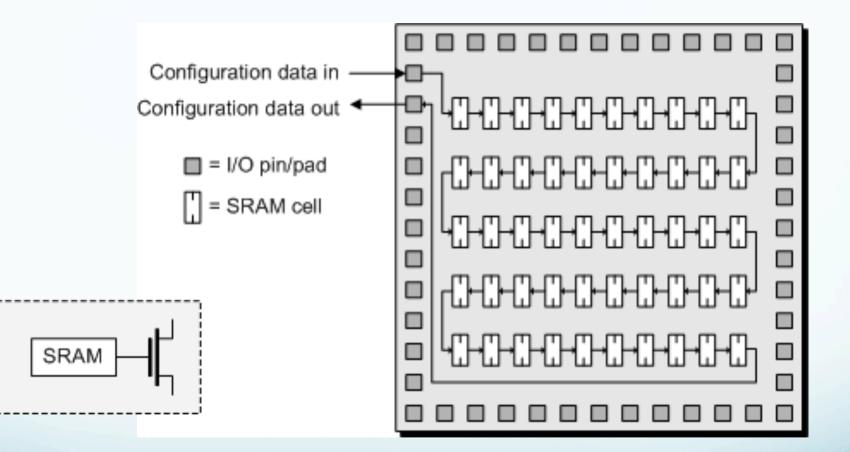

#### **SRAM-Based Devices**

Multi-transistor SRAM cell

#### Programming a 3-bit wide LUT

# Summary of Technologies

| Technology                    | Symbol       | Predominantly<br>associated with |                           |

|-------------------------------|--------------|----------------------------------|---------------------------|

| Fusible-link                  | _~~_         | SPLDs                            |                           |

| Antifuse                      |              | FPGAs                            | Rad-tolerant secure       |

| EPROM                         | ΗĽ           | SPLDs and CPLDs                  |                           |

| E <sup>2</sup> PROM/<br>FLASH | -1× <b>L</b> | SPLDs, CPLDs,<br>and FPGAs       | Rad-tolerant (e.g. Alice) |

| SRAM                          |              | FPGAs (some CPLDs)               | Used in most FPGAs        |

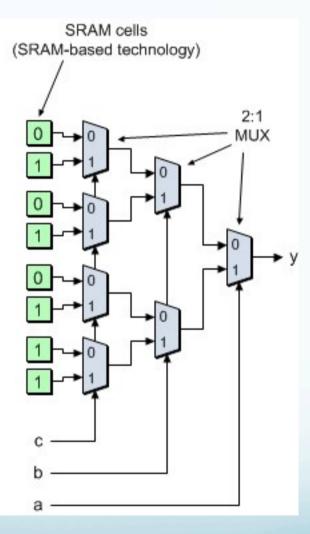

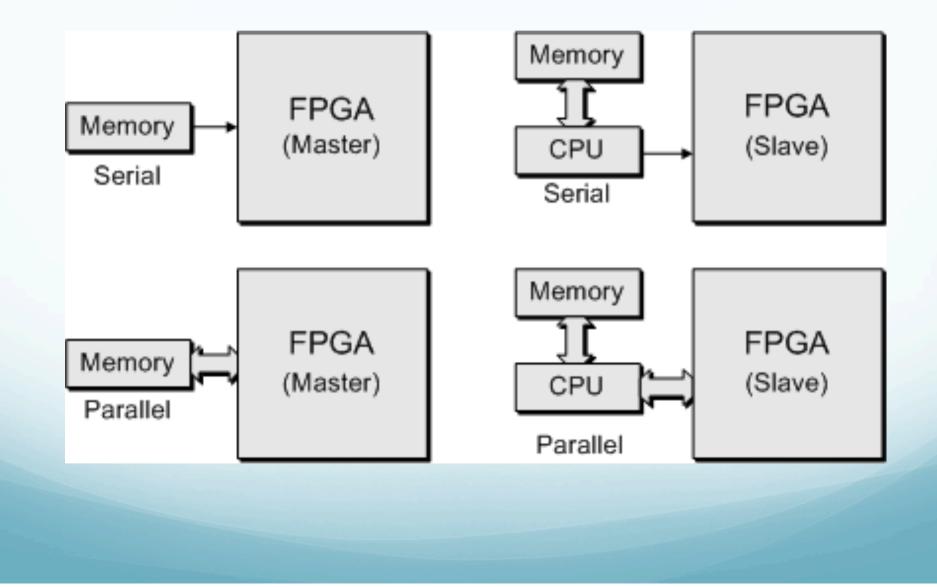

#### Design Considerations (SRAM Config.)

### Configuration at power-up

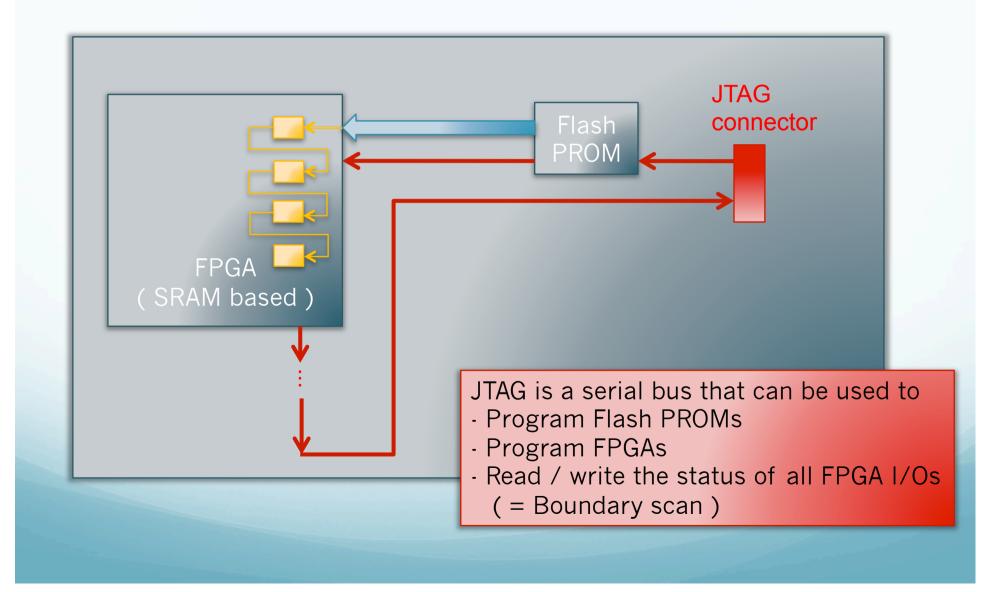

## Programming via JTAG

#### Joint Test Action Group

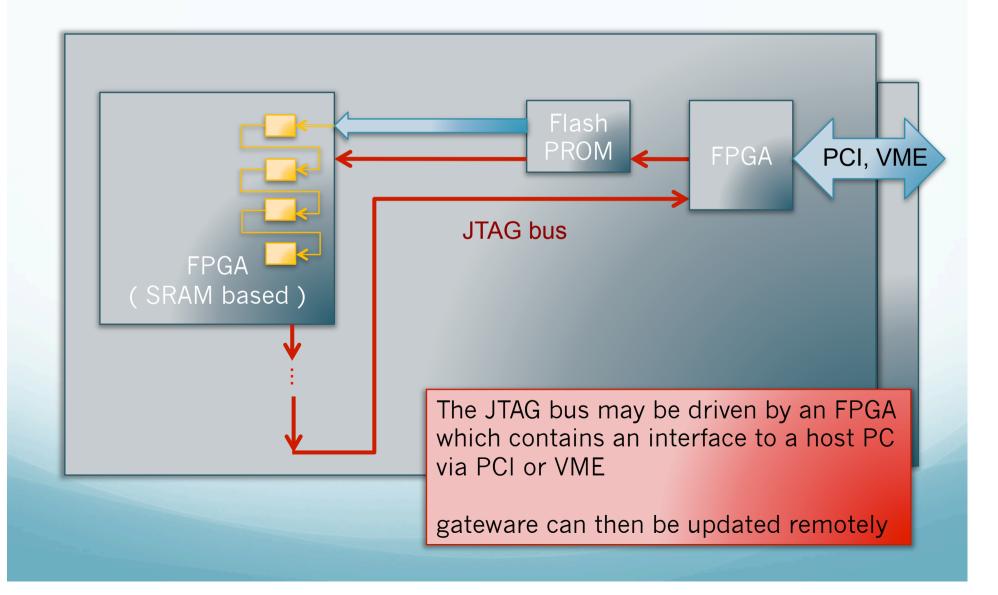

### Remote programming

# Major Manufacturers

- Xilinx

- First company to produce FPGAs in 1985

- About 55% market share, today

- SRAM based CMOS devices

- Intel FPGA (formerly Altera)

- About 35% market share

- SRAM based CMOS devices

- Microsemi (Actel)

- Anti-fuse FPGAs

- Flash based FPGAs

- Mixed Signal

- Lattice Semiconductor

- SRAM based with integrated Flash PROM

- low power

**E** XILINX.

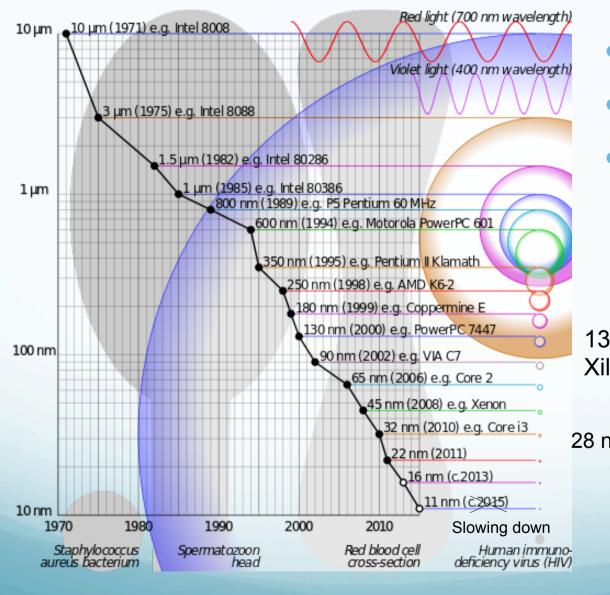

### **Ever-decreasing feature size**

- Higher capacity

- Higher speed

- Lower power consumption

130 nm Xilinx Virtex-2

28 nm Xilinx Virtex-7 / Altera Stratix V 16 nm Xilinx UltraScale + 14 nm Intel Stratix 10

> 5.5 million logic cells 4 million logic cells

## Trends

- Speed of logic increasing

- Look-up-tables with more inputs (5 or 6)

- Speed of serial links increasing (multiple Gb/s)

- Integrated High Bandwidth Memory (HBM) in-package

- Additional Flip Flops in routing resources

- More and more hard macro cores on the FPGA

- PCI Express

- Gen2: 5 Gb/s per lane

- Gen3: 8 Gb/s per lane up to 8 lanes / FPGA

- Gen4: 16 Gb/s per lane

- 10 Gb/s, 40 Gb/s, 100 Gb/s Ethernet

- Sophisticated soft macros

- CPUs

- Gb/s MACs

- Memory interfaces (DDR2/3/4)

Processor-centric architectures – see next slides

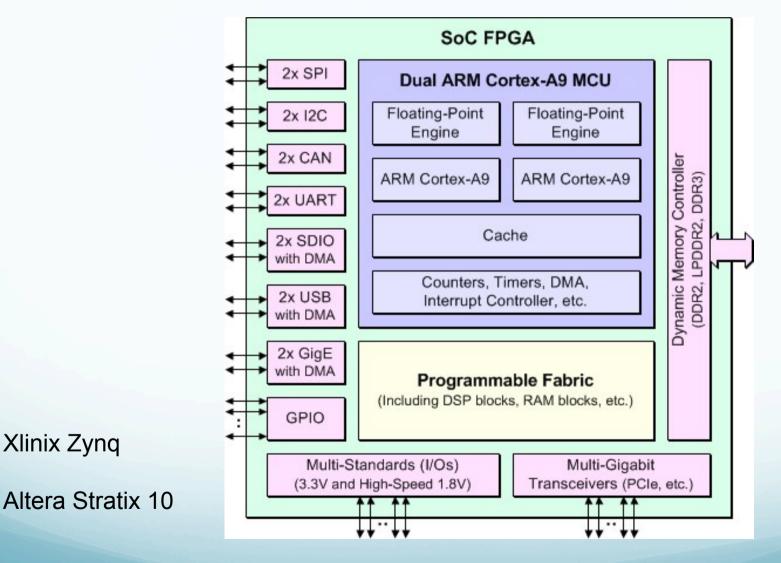

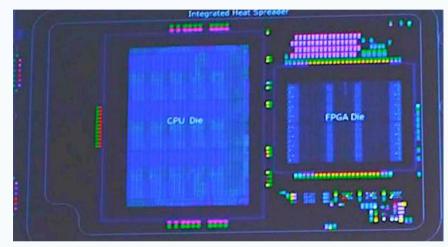

### System-On-a-Chip (SoC) FPGAs

CPU(s) + Peripherals + FPGA in one package

#### FPGAs in Server Processors and the Cloud

- Since 2016: Intel Xeon Server Processor with FPGA in socket

- Intel acquired Altera in 2015

- FPGAs in the cloud

- Amazon Elastic Cloud F1 instances

- 8 CPUs / 1 Xlinix UltraScale+ FPGA

- 64 CPUs / 8 Xlinix UltraScale+ FPGA

# FPGA – ASIC comparison

#### FPGA

- Rapid development cycle (minutes / hours)

- May be reprogrammed in the field (gateware upgrade)

- New features

- Bug fixes

- Low development cost

- You can get started with a development board (< \$100) and free software

#### ASIC

- Higher performance

- Analog designs possible

- Better radiation hardness

- Long development cycle (weeks / months)

- Design cannot be changed once it is produced

- Extremely high development cost

- ASICs are produced at a semiconductor fabrication facility ("fab") according to your design

- Lower cost per device compared to FPGA, when large quantities are needed

### **FPGA development**

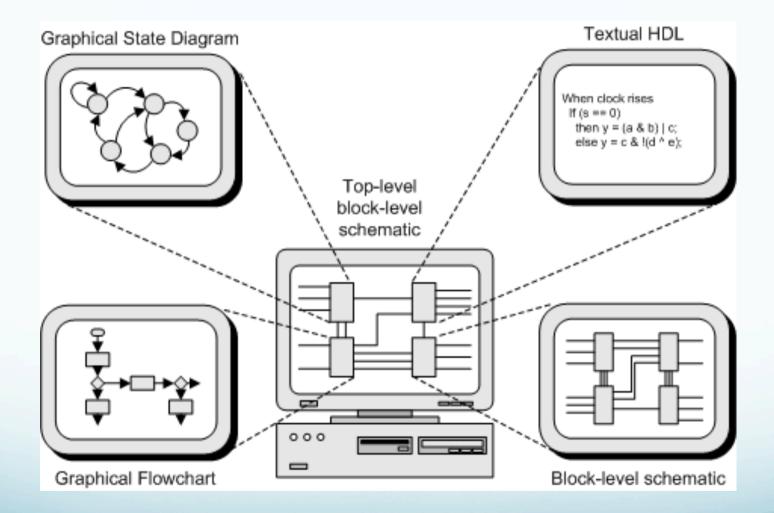

# Design entry

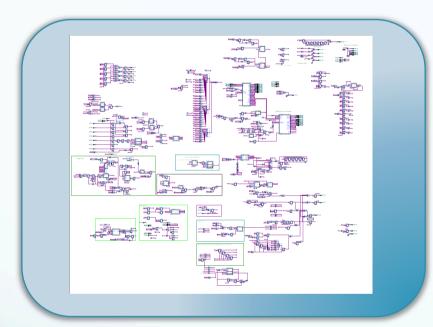

#### Schematics

- Graphical overview

- Can draw entire design

- Use pre-defined blocks

Hardware description language VHDL, Verilog

- Can generate blocks using loops

- Can synthesize algorithms

- Independent of design tool

- May use tools used in SW development (SVN, git ...)

Mostly a personal choice depending on previous experience

### Schematics

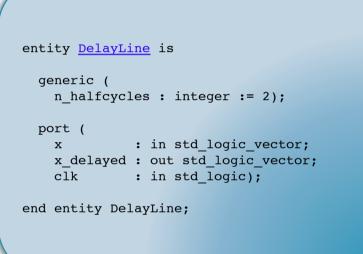

### Hardware Description Language

- Looks similar to a programming language

- BUT be aware of the difference

- Programming Language => translated into machine instructions that are executed by a CPU

- HDL => translated into gateware (logic gates & flip-flops)

- Common HDLs

- VHDL

- Verilog

- AHDL (Altera specific)

#### Newer trends

- C-like languages (handle-C, System C)

- Labview

```

Example: VHDL

architecture behavioral of VMEReg is

signal vme_en_i : std_logic;

signal 0 : std_logic_vector(15 downto 0);

Looks like a

begin -- behavioral

programming

vme_addr_decode : process (vme_addr, vme_en) is

variable my_addr_vec : std_logic_vector(vme_addr'high downto 0);

language

variable selected : boolean:

begin -- process vme_addr_decode

my_addr_vec := std_logic_vector( TO_UNSIGNED ( my_vme_base_address, vme_addr'high+1 ) );

selected := my_addr_vec(vme_addr'high downto 1) = vme_addr(vme_addr'high downto 1);

vme_en_i <= '0' :

if selected then

vme_en_i <= vme_en;</pre>

All statements

end if:

end process vme_addr_decode;

executed in

reg: process (vme_clk, reset) is

parallel, except

begin -- process reg

if reset = '1' then

-- asynchronous reset

inside

0 <= init_val;</pre>

vme_en_out <= '0';</pre>

elsif vme_clk'event and vme_clk = '1' then -- rising clock edge

processes

vme_en_out <= vme_en_i;</pre>

if vme_en_i = '1' and vme_wr = '1' then

0 <= vme_data;

end if:

end if:

end process reg;

data \leq 0:

vme_data_out <= Q;

end behavioral;

```

### Schematics & HDL combined

# Design flow

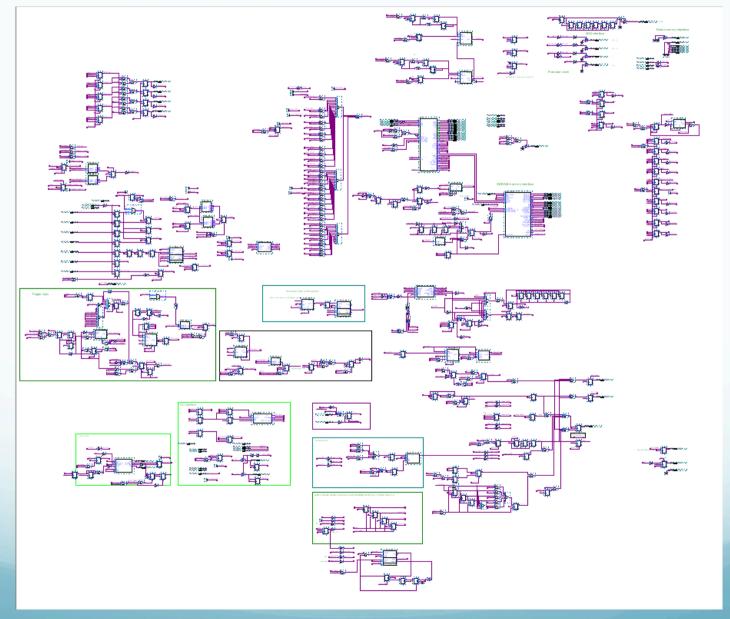

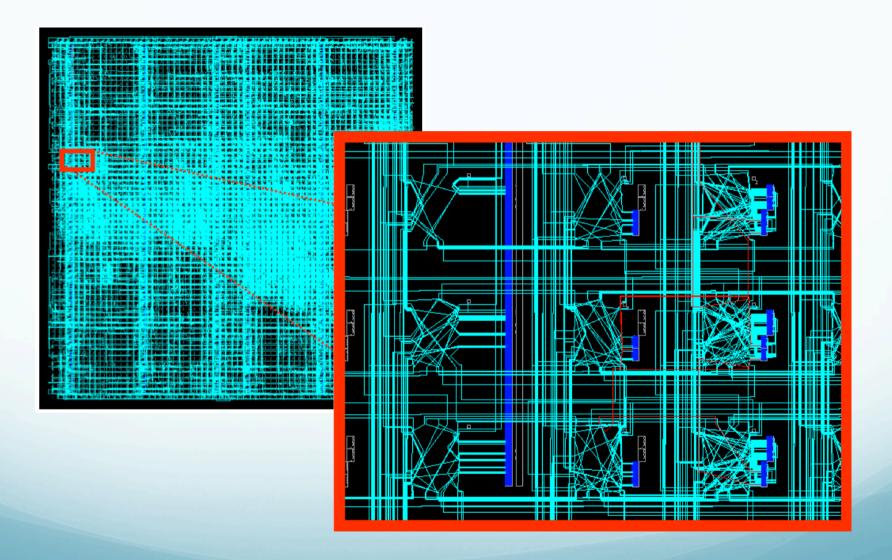

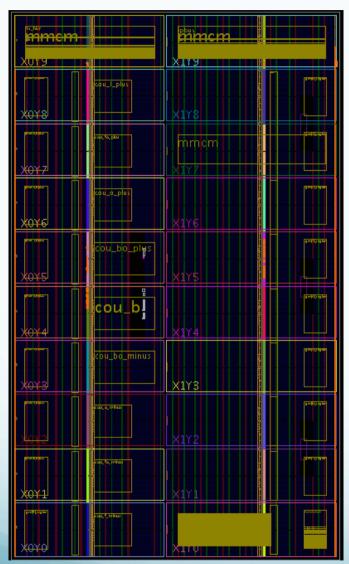

### Floorplan (Xlinx Virtex 2)

### Manual Floor planning

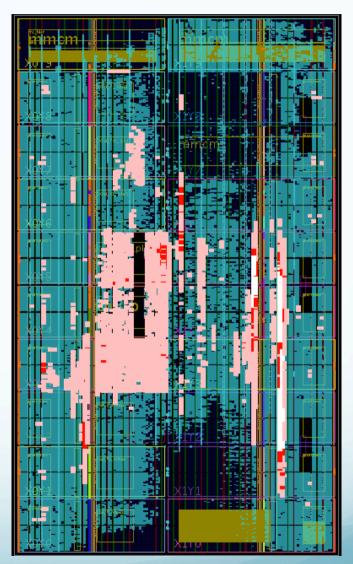

For large designs, manual floor planning may be necessary

Routing congestion Xilinx Virtex 7 (Vivado)

### Simulation

|                          |              |          | _gx_kit/fpga/PCle_optic       |                                               | [ <i>III</i> CMS_                       | _GIII_dev/Fed_ | cms_luminosity/ve                         | r_used/dma_M                            | 64_dt0.vwf]                                                                                                     |                                     |              |                        |                                         |                                         |             |

|--------------------------|--------------|----------|-------------------------------|-----------------------------------------------|-----------------------------------------|----------------|-------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|------------------------|-----------------------------------------|-----------------------------------------|-------------|

|                          |              |          | nents Processing Tools W      | /indow Help                                   |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         | _ 8 ×       |

|                          | 🛎 🛛 🖉 🖉      | 8        | top 🗠 🗈 🗈                     |                                               | _ 🔄 💥 🖉                                 | ' 🏈 🧇 🕴        | 📴 🕨 💐 🌬 隆                                 | ) () 🖹 🖗                                | 👋 🖷 📀                                                                                                           |                                     |              |                        |                                         |                                         |             |

| 👔 top.bd                 | lf           |          | 😔                             | w Summary 🛛 🕴 🕸 decoder_pck.tdf               |                                         |                | 📔 🔝/mmu_ctrl/mmu.bdf                      |                                         |                                                                                                                 | /./CMS_GIII_dev/Fed/dma_M64_dt0.vwf |              |                        |                                         |                                         |             |

| Maste                    | er Time Bar: |          | 1.5274 us                     | Pointer:                                      |                                         | 358.4 ns       | Interval:                                 |                                         | -1.17 us                                                                                                        | Start                               |              |                        | End                                     |                                         |             |

|                          |              |          | 0 ps 160,0 ns                 | 320,0 ns                                      | 480,0 ns                                | 640,0 ns       | 800,0 ns                                  | 960,0 ns                                | 1.12 us                                                                                                         | 1.28 us                             | 1.44 us      | 1.6 us 1.              | 76 us 1.92 us                           | 2.08 us                                 | ^           |

| A                        | Name         |          |                               | · · · · · · · · · · · · · · · · · · ·         |                                         |                |                                           |                                         |                                                                                                                 |                                     | -25.6 ns4    | 1 us +182.8 ns         |                                         |                                         |             |

| <del>∭</del> ⊛0          |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     | Ī            | THE THE                |                                         |                                         |             |

| ⊕ 1                      |              |          | Խուսուսուսու                  | ոսուսուսու                                    | սոսոսու                                 | www.www        | munnm                                     | www.                                    | mmm                                                                                                             | տուսուսուսու                        | wwww         | ոսուսուսուսո           | www.www.ww                              | nnnnn                                   | mm          |

|                          |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        | *****                                   | ********                                | <u>۲</u>    |

| M 🚳 4                    |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| ☆ <mark>@</mark> 5<br>@6 |              | sult     |                               |                                               |                                         |                | <del>                              </del> |                                         |                                                                                                                 |                                     | -            |                        |                                         |                                         |             |

| ∑ 🗗 7                    |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| →<br>0 ●8                |              | tor      |                               | Idle_m                                        |                                         |                |                                           | M data                                  |                                                                                                                 | ldle_m                              | YMY M        | data Xidle_mXXXX       | M data                                  |                                         | V Idle m    |

| 1                        |              |          | (Idle ){1_dat,XIdle )[_da)(dk | €XI_daX Idle                                  | XX_de>                                  |                |                                           | Idle                                    | ^                                                                                                               |                                     |              |                        | Idle                                    |                                         |             |

| 1<br>                    |              | H 0(     | ZZ()/ZZZZZZ)(#0074/\$/()#     |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        | ĴŨŨŒŨŒŒŒŨŨŒŨŒŒ<br>ĨĴŨŒŨŒŒŒŒŨŨŒŨŒŒŒ      | 00000000000                             | 7777777     |

| —<br>४ज<br>२००१          |              | uit H Ul |                               | 0000¢())(000000)(ZZZZ<br>00 \¢)()(         00 | 2222/1000455/2<br>XXXX 00 XZ            |                | C and a low a g a g a g                   | ZZ                                      | NUNNAN WAR                                                                                                      | XX 00 XZXX 00 X                     |              |                        |                                         | X51 00 X2                               | 200 00      |

| XE 🐼 1                   |              |          |                               |                                               | XXX 00 X2                               | zxX oo XzzX    | X0022X1K                                  | 00                                      | ×                                                                                                               | 200 00 XZXX 00 X                    | ZZ XXX       | 00 <u>X ZZ X</u> X     | 00                                      | 00 X4X                                  | X2X0X 00    |

| XE @1                    |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         | J           |

| Ale 🚳 1                  | 61 IRDY      |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         | ·           |

| ∰<br>∑c @1               |              | ult      |                               |                                               |                                         |                |                                           |                                         | ×                                                                                                               |                                     |              |                        |                                         |                                         |             |

|                          |              | ult      |                               | +                                             |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| 1                        |              |          |                               |                                               | <u> </u>                                |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

|                          |              | sult     |                               | <u>.</u>                                      |                                         |                | V                                         |                                         | <del></del>                                                                                                     |                                     |              |                        |                                         |                                         |             |

| 號 @●1                    | 68P~res      |          |                               |                                               | ×                                       | ×              | u                                         |                                         |                                                                                                                 | tt State St                         |              | -0                     |                                         |                                         | J++++       |

| <b>2</b> ↓               |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| <ul> <li>1</li> </ul>    | 71 last_c    |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

|                          |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| @1                       |              | sult     |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| 1                        |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              | ~~~                    |                                         |                                         |             |

|                          |              |          | ****                          |                                               |                                         |                | ***                                       |                                         |                                                                                                                 |                                     | 889          | **                     |                                         |                                         |             |

| ·@ 1                     | 78 user107   | ·        |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

|                          |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| <b>■</b> 1               | 81 UCLK      | •        |                               | ກ່ານການການການການການການການການການການການການກາ    | www.ww                                  | www.ww         | unnnnn                                    | www.ww                                  | ການນັ້ນການນ                                                                                                     | ການການການການການ                     | mmmm         | unnnnnn                |                                         | www.ww                                  | www         |

| 1                        |              |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| @1                       |              | H AI     |                               | 00                                            | 000000000000000000000000000000000000000 | 0              |                                           | x0x0x0x                                 | DED CERCIERD | ODECED CONCER                       | A00001000000 |                        |                                         | 000000000000000000000000000000000000000 | KOKEGOGI    |

| 2                        |              | _        |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| @ 2<br>@ 2               |              | '        |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| <b>a</b> 2               | 52 🗉 inst58  |          |                               | 000000                                        | 00                                      |                | XX                                        | 00000000                                | X                                                                                                               | A0000100                            | x x          | C III                  | 00000000                                |                                         |             |

| 2                        |              |          |                               | 000000                                        | 00                                      |                |                                           | იიოიოიოოო                               | <u>พากการการ</u>                                                                                                | 00000000                            |              | (F)()()() 00000008 )(F | Ⴛოოიიიოიოოოიიიო                         | ለስለሰብ በሰብ በ                             | 1\000003F   |

| - 3 C                    |              | e l      |                               | 00000                                         | ~                                       |                |                                           | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                                                                                                                 | 0000000                             |              | KANA COOLOGO A         | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                                         | CACCOCCUCIE |

| @ 3<br>@ 3               | 20 wp_boo    | t i      |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         |             |

| <                        |              | >        | <                             |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        |                                         |                                         | >           |

| For Help, pre            | ess F1       |          |                               |                                               |                                         |                |                                           |                                         |                                                                                                                 |                                     |              |                        | J 🔁 → 🖿 → 📖 🛛 36%                       | • 00:08:49                              | NUM         |

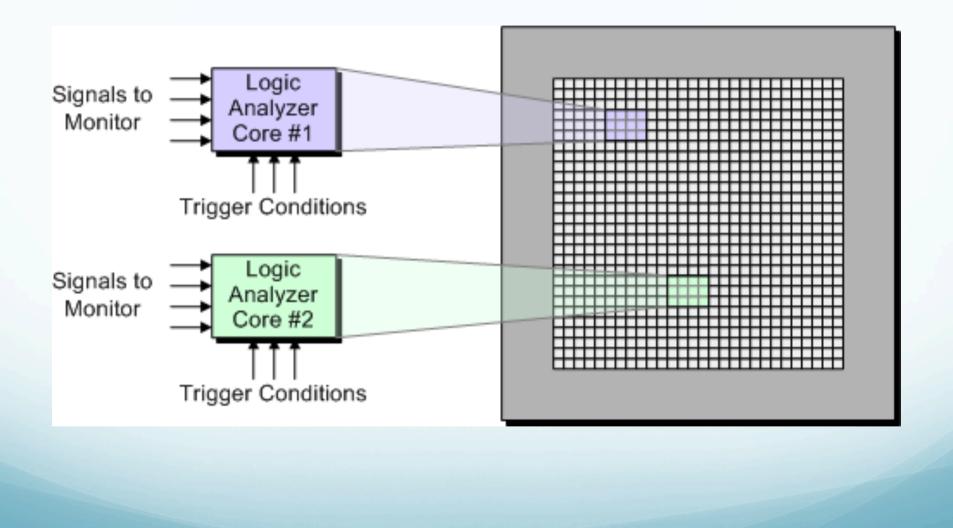

### Embedded Logic Analyzers

# FPGA applications in the Trigger & DAQ domain

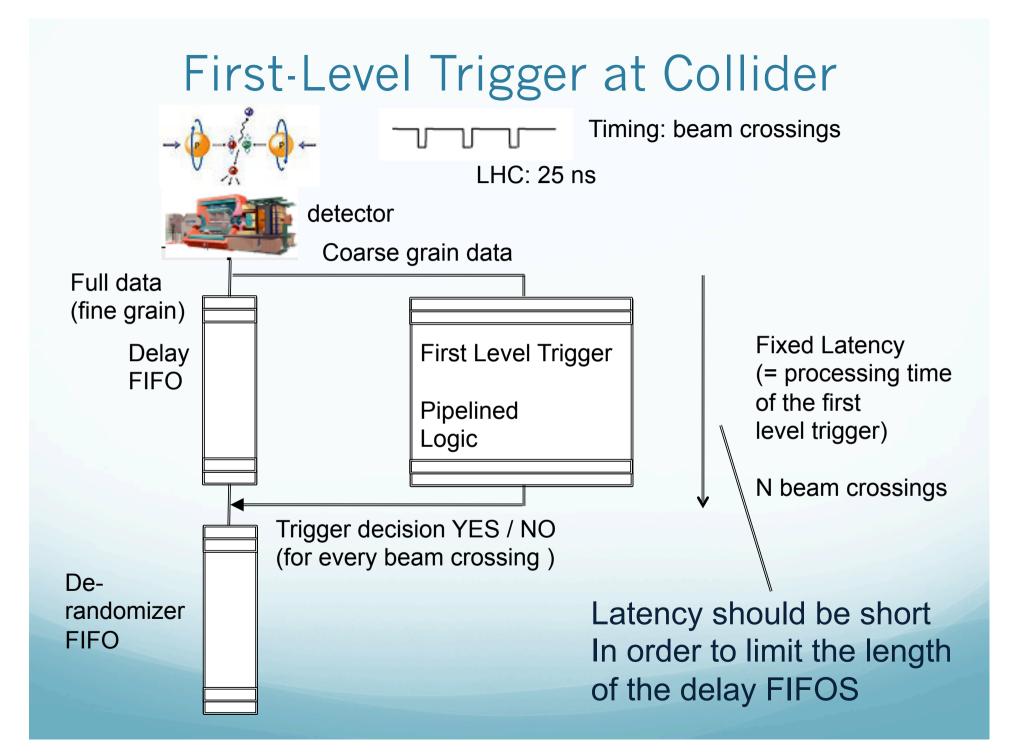

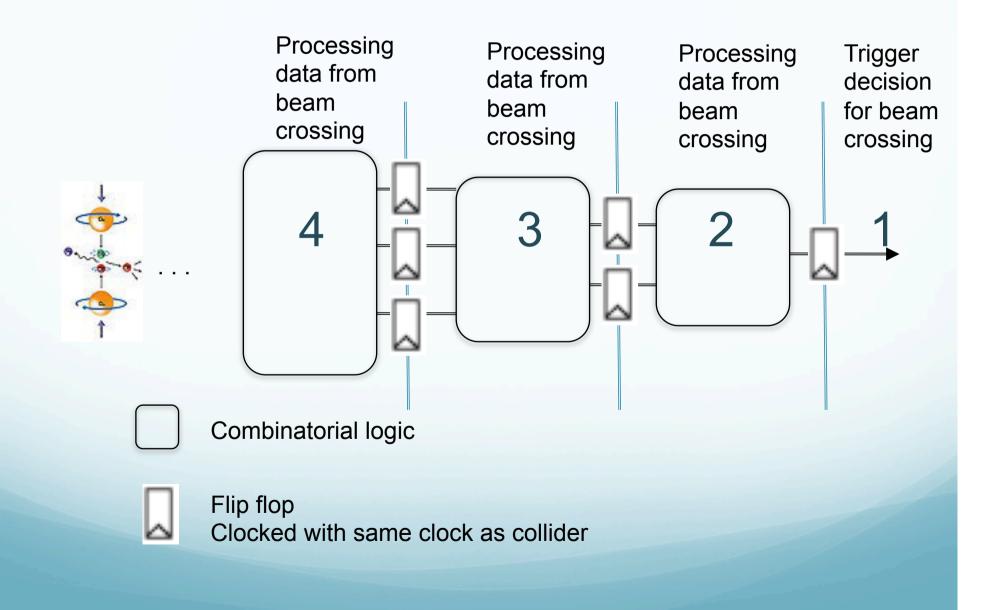

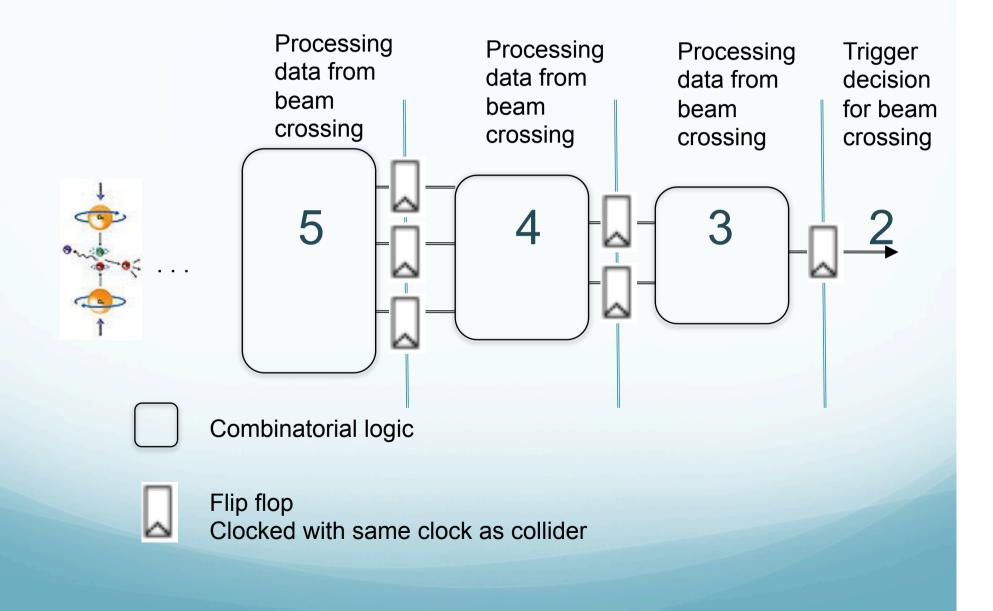

#### Pipelined Logic

#### Pipelined Logic – a clock cycle later

#### Why are FPGAs ideal for First-Level Triggers ?

- They are fast

- Much faster than discrete electronics (shorter connections)

- Many inputs

- Data from many parts of the detector has to be combined

- All operations are performed in parallel

Can build pipelined logic

- Can build pipelined logic

- They can be re-programmed

- Trigger algorithms can be optimized

High performance

Low latency

#### Trigger algorithms implemented in FPGAs

- Peak finding

- Pattern Recognition

- Track Finding

- Energy summing

- Sorting

- Topological Algorithms (invariant mass)

- Trigger Control system

- Fast signal merging

Many more ...

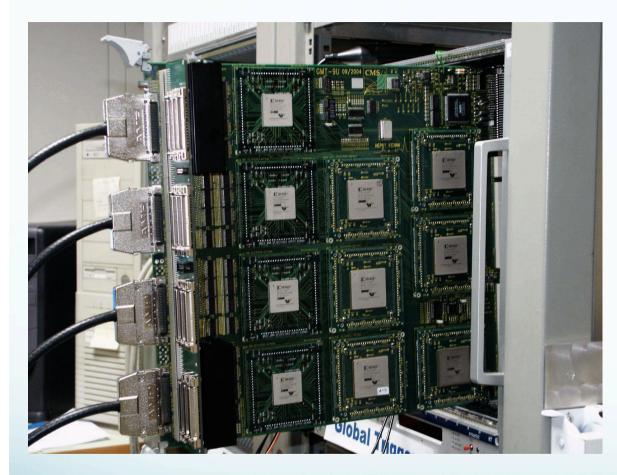

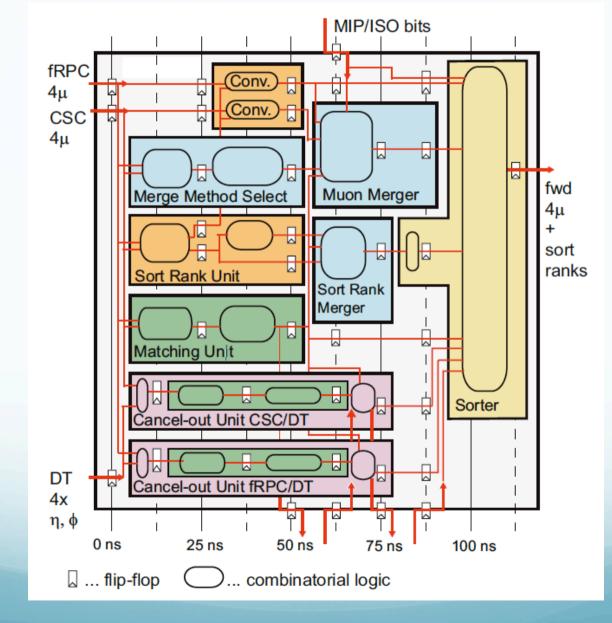

#### Example 1: CMS Global Muon Trigger

• The CMS Global Muon trigger received 16 muon candidates from the three muon systems of CMS

It merged different measurements for the same muon and found the best 4 over-all muon candidates

- Input: ~1000 bits

@ 40 and 80 MHz

- Output: ~50 bits @ 80MHz

- Processing time: 250 ns

- Pipelined logic one new result every 25 ns

- 10 Xilinx Virtex-II FPGAs

- up to 500 user I/Os per chip

- Up to 25000 LUTs per chip used

- Up to 96 x 18kbit RAM used

- In use in the CMS trigger 2008-2015

#### CMS Global Muon Trigger main FPGA

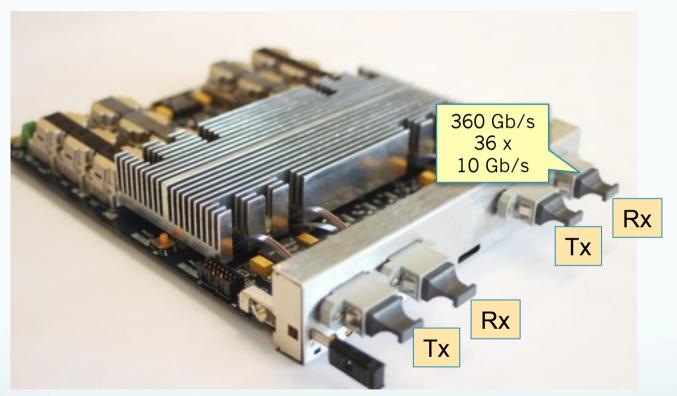

#### Example 2: New µTCA board for CMS trigger upgrade based on Virtex 7

MP7, Imperial College

Virtex 7 with 690k logic cells 80 x 10 Gb/s transceivers bi-directional 72 of them as optical links on front panel 0.75 + 0.75 Tb/s Being used in the CMS trigger since 2015 Input/output: up to 14k bits per 40 MHz clock

Same board used for different functions (different gateware) Separation of framework + algorithm fw

#### FPGAs in Data Acquisition

- Frontend Electronics

- Pedestal subtraction

- Zero suppression

- Compression

- ...

- Custom data links

- E.g. SLINK-64 over copper

- Several serial LVDS links in parallel

- Up to 400 MB/s

- SLINK/SLINK-express over optical

- Interface from custom hardware to commercial electronics

- PCI/PCIe, VME bus, Myrinet, 10/40/100 Gb/s Ethernet etc.

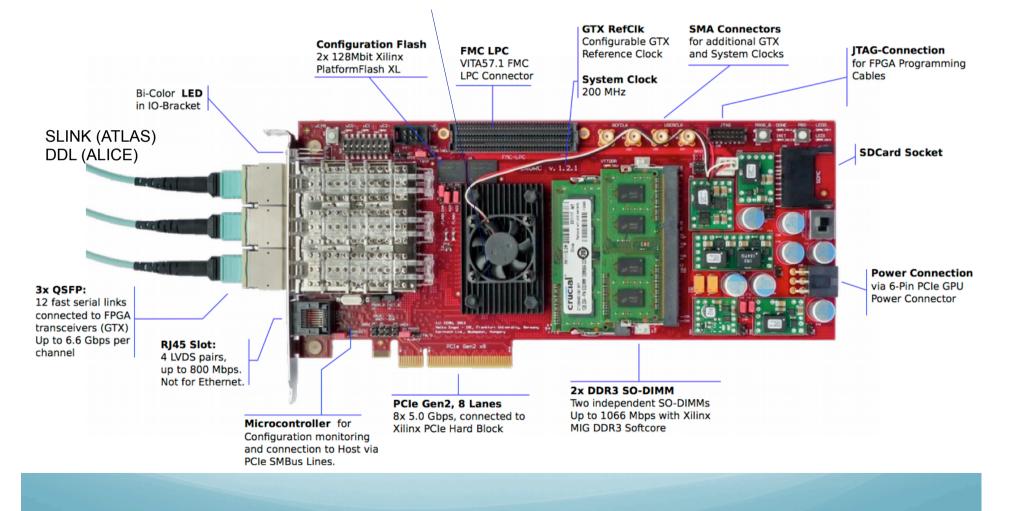

#### C-RORC (Alice) / Robin NP (ATLAS) for Run-2

#### Xilinx Virtex-6 FPGA

#### Example 3: CMS Front-end Readout Link (Run-1)

- SLINK Sender Mezzanine Card: 400 MB / s

- 1 FPGA (Altera)

- CRC check

- Automatic link test

Commercial Myrinet Network Interface Card on internal PCI bus

- Front-end Readout Link Card

- 1 main FPGA (Altera)

- 1 FPGA as PCI interface

- Custom Compact PCI card

- Receives 1 or 2 SLINK64

- 2nd CRC check

- Monitoring, Histogramming

- Event spy

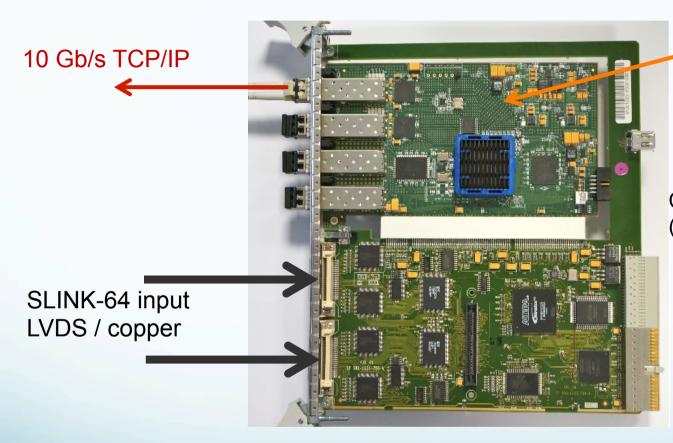

#### Example 4: CMS Readout Link for Run-2 in use since 2015

Myrinet NIC replaced by custom-built card ("FEROL")

Cost effective solution (need many boards) Rather inexpensive FPGA + commercial chip to combine 3 Gb/s links to 10 Gb/s

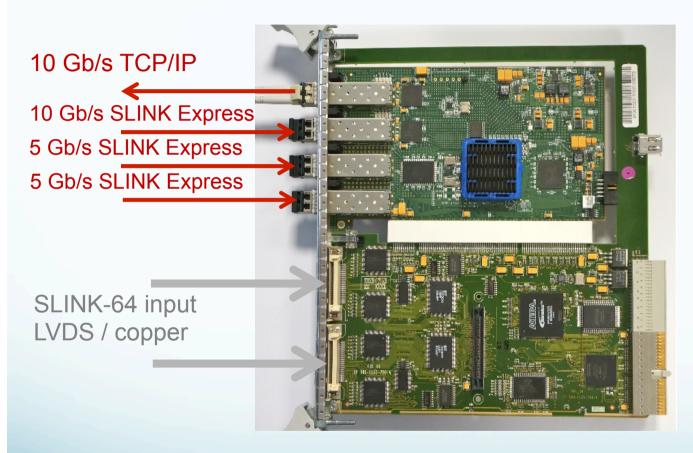

#### FEROL (Front End Readout Optical Link)

Input:

1x or 2x SLINK (copper) 1x or 2x 5Gb/s optical 1x 10Gb/s optical

Output: 10 Gb/s Ethernet optical TCP/IP sender in FPGA

#### Example 4: CMS Readout Link for Run-2

#### FEROL (Front End Readout Optical Link)

Input:

1x or 2x SLINK (copper) 1x or 2x 5Gb/s optical 1x 10Gb/s optical

Output: 10 Gb/s Ethernet optical TCP/IP sender in FPGA

## FPGAs in other domains

- Medical imaging

- Advanced Driver Assistance Systems (Image Processing)

- Speech recognition

- Cryptography

- Bioinformatics

- Aerospace / Defense

- Bitcoin mining

- ASIC Prototyping

- High performance computing

- Accelerator cards

• Server processors w. FPGA