# Upgrade of the ATLAS **Thin Gap Chamber Electronics for HL-LHC**

Prototype

LHCP2019, 20-25 May, 2019 Puebla in Mexico Haruka Asada (Nagoya University) on behalf of the ATLAS Collaboration

## Introduction

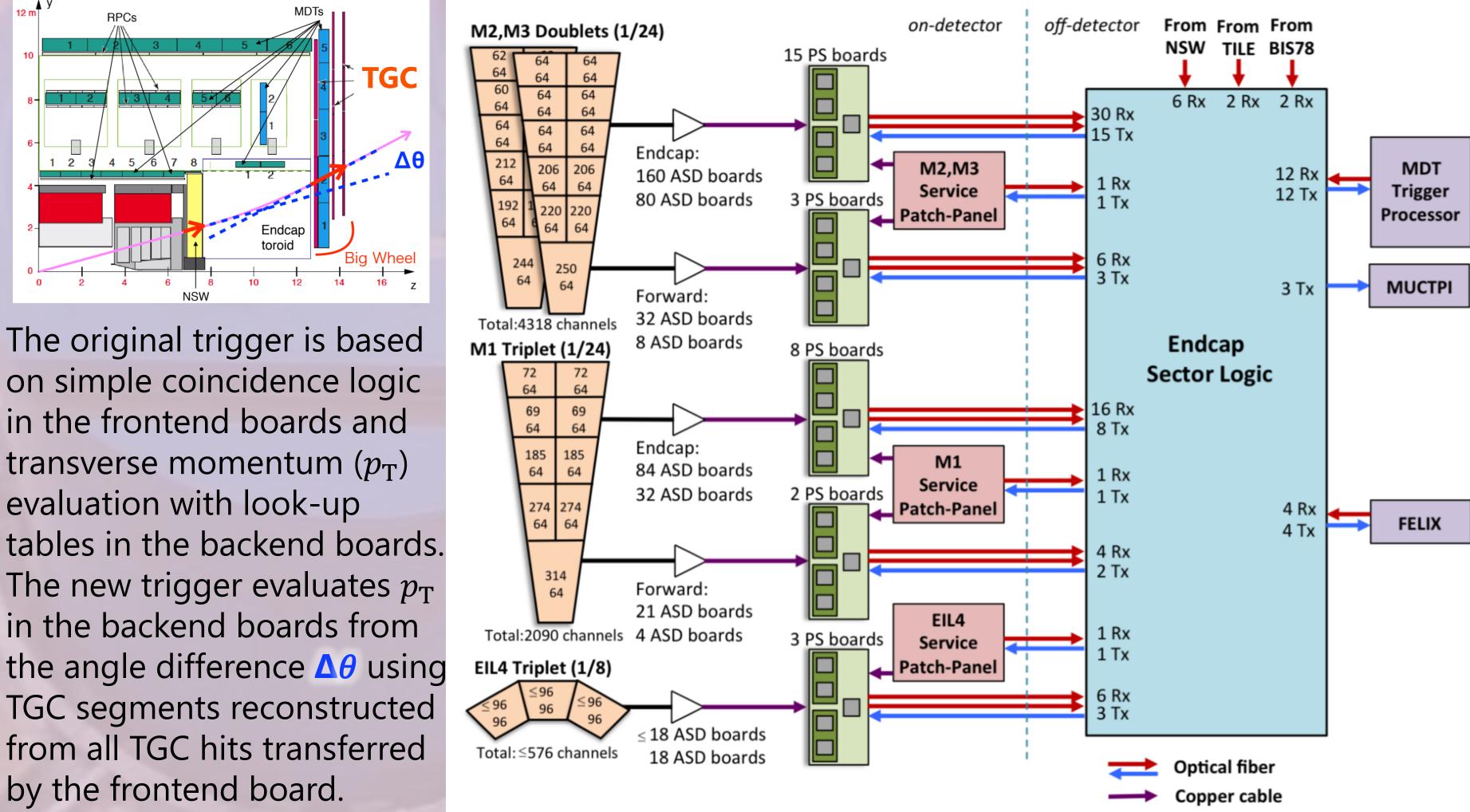

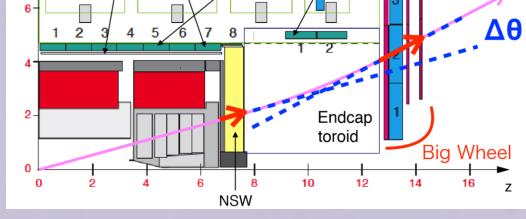

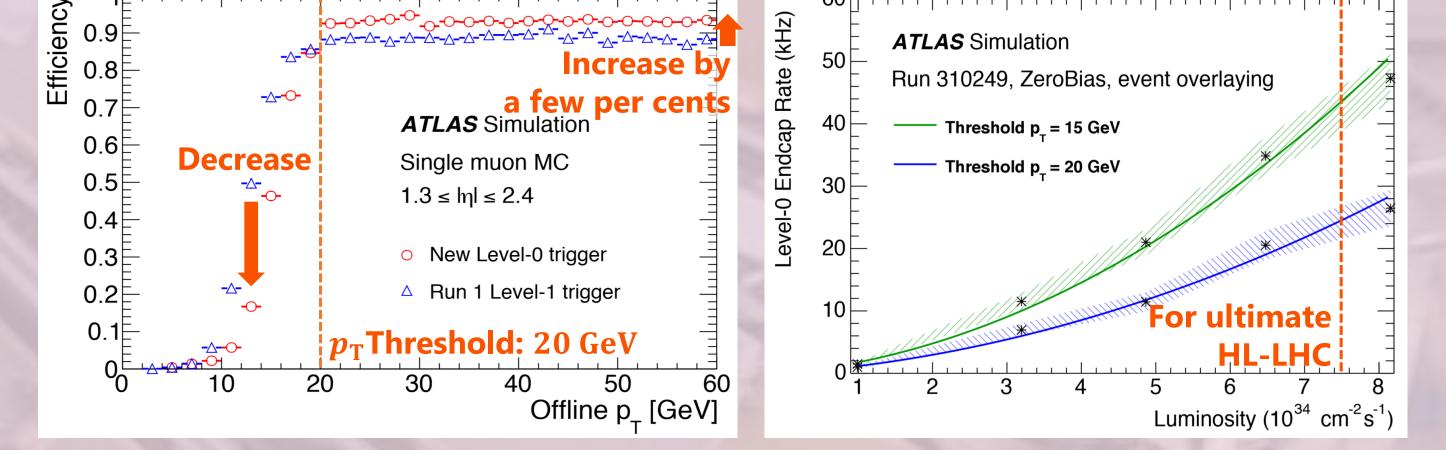

High-Luminosity LHC (HL-LHC) [1] is planned to start the operation in 2026 with instantaneous luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. To cope with protonproton collision rate higher than LHC, the trigger and readout electronics of ATLAS Thin Gap Chamber (TGC) [2] will be replaced. In the new trigger system, all TGC hit data are transferred from frontend to backend boards and exploited by advanced first-level muon trigger based on a fast tracking [3,4].

# **TGC electronics for HL-LHC**

**TGC**: multi-wire proportional chamber at endcap (pseudorapidity  $\eta$  range 1.05 – 2.4) of the ATLAS muon detector.

- Measures two-dimensional position using signals from wires and strips orthogonal to the wires.

- Consists of three stations. Station M1 has three layers. M2 and M3 have two layers, respectively.

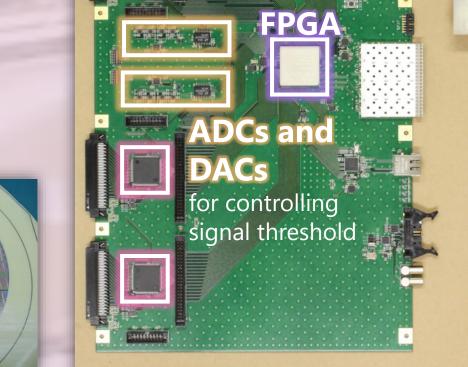

Frontend: **PS board**

- Hit timing alignment by Patch-Panel (PP) ASICs

- Hit data transfer at \_ 16 Gbps and ADC/DAC

control by FPGA PS board prototype has full functions for HL-LHC. Mass production of new PP ASICs in 2019.

#### Backend: Endcap Sector Logic (SL)

- Trigger process, e.g. TGC segment reconstruction

- Data readout

SL communicates with electronics of various detectors. Main functions of SL is implemented on one FPGA. The Virtex UltraScale(+) FPGAs provided Xilinx [5] are assumed for the FPGA on SL.

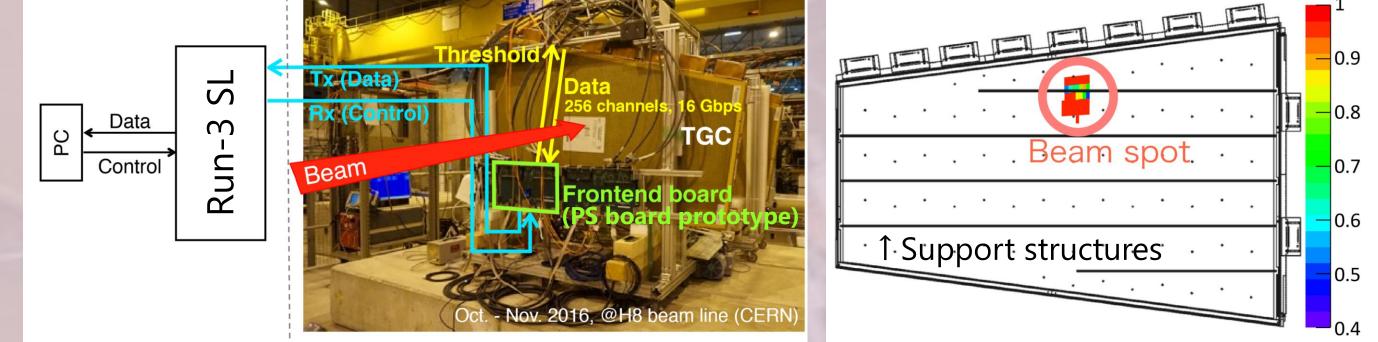

## **Demonstration with PS board prototype**

Functions of FPGA on PS board have been tested with beams.

Full TGC readout chain

Efficiency

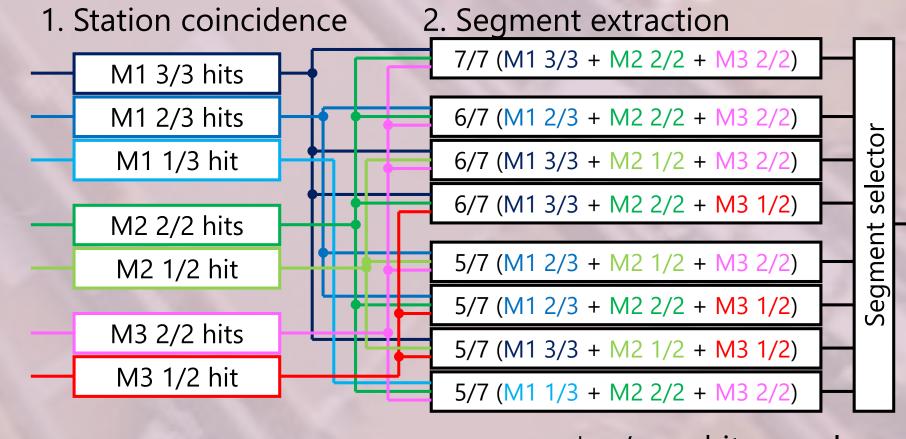

## **TGC** segment reconstruction

Segment reconstruction with a pattern matching is under study [4].

The new algorithm has been studied with MC and data samples.

- **PS board prototype provided stable data transfer with 2 × 8 Gbps**.

- The validity of the transferred data has been confirmed by evaluating the efficiency for each channel.

- Signal threshold control based on FPGA has been demonstrated.

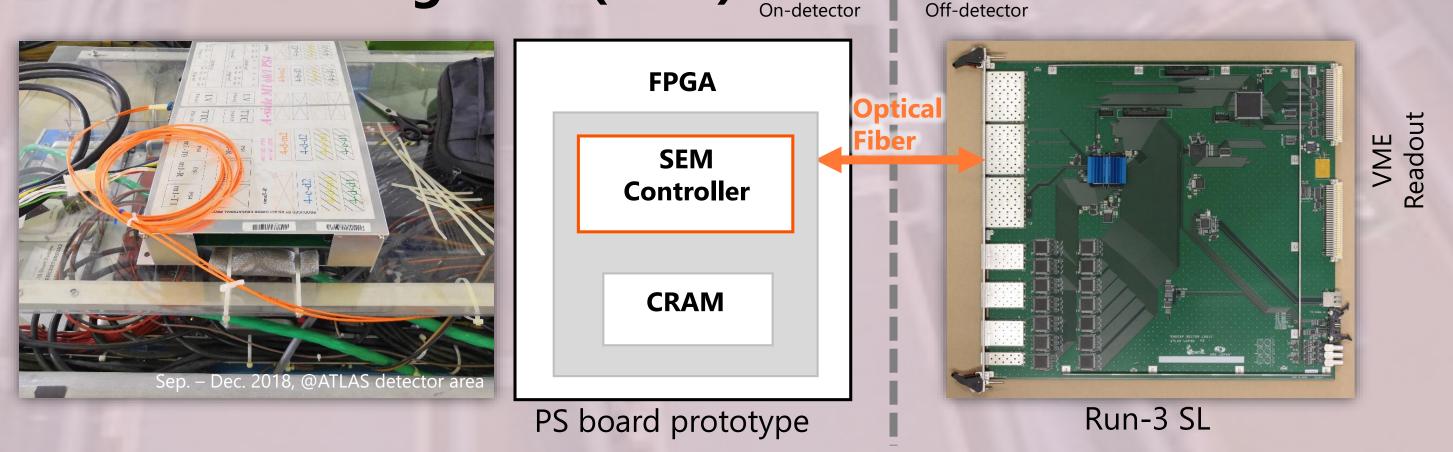

#### Soft Error Mitigation (SEM)

A PS board prototype was installed on the top of TGC about 13 m away from the beam axis. SEM demonstration was performed for about nine weeks.

However, the channel list used in the performance studies cannot be implemented on an FPGA because of its huge size. Therefore TGC segment reconstruction based on two-step pattern matching is proposed.

\* x / y : x hits on y layers

The Diagram is shown for wires. Similar logic is assumed for strips.

- The list implemented on RAMs is used in the second step.

- Majority of memory resources will be spend by the list.

The resource estimation is an R&D item. Preliminary estimation of the list size per SL is about one-third of 345.9 Mb of a RAM resource on the baseline Virtex UltraScale+ FPGA. The demonstration with an FPGA on an evaluation board is proceeding.

**16 Single Event Upsets (SEUs) have been found** on one Kintex-7 FPGA of PS board prototype in operation of 12.6  $fb^{-1}$ .

- All SEUs were one bit errors.

- All errors were automatically corrected by the SEM controller [6].

- No GTX communication error was observed.

| 20 [                                      |  |

|-------------------------------------------|--|

| ATLAS Muon Operations                     |  |

| 15 Phase II Upgrade Study, vs = 13 TeV    |  |

| XC7K325T-2FFG900C                         |  |

| Big Wheel, R ~ 13 m                       |  |

|                                           |  |

| 0 2 4 6 8 10 12                           |  |

| Integrated luminosity (fb <sup>-1</sup> ) |  |

## Conclusion

Hardware development of the ATLAS TGC electronics for HL-LHC is ongoing. The PS board prototype has been successfully demonstrated. The tracking trigger with pattern matching algorithm is expected to improve the endcap trigger performance.

#### Reference

[1] G. Apollinari, I. Bejar Alonso, O. Bruning, P. Fessia, M. Lamont, L. Rossi and L.Tavian, High-Luminosity Large Hadron Collider (HL-LHC) : Technical Design Report V. 0.1, CERN-2017-007-M. [2] The ATLAS Collaboration, The ATLAS Experiment at the CERN Large Hadron Collider, JINST 3 (2008) \$08003.

[3] The ATLAS Collaboration, Technical Design Report for the Phase-II Upgrade of the ATLAS Muon Spectrometer, CERN-LHCC-2017-017.

[4] The ATLAS Collaboration, Technical Design Report for the Phase-II Upgrade of the ATLAS TDAQ system, CERN-LHCC-2017-020. [5] Xilinx Inc., https://www.Xilinx.com/ (accessed on April 25<sup>th</sup>, 2019). [6] Xilinx Inc., Soft Error Mitigation Controller v4.1 LogiCORE IP Production Guide, PG036 April 4, 2018.