# The CHIPIX65 asynchronous front-end for the HL-LHC experiment upgrades

L. Gaionia,c, F. De Canioa,c, M. Manghisonia,c, L. Rattib,c, V. Rea,c, G. Traversia,c

<sup>a</sup>Università di Bergamo Dipartimento di Ingegneria e Scienze Applicate

bUniversità di Pavia

Dipartimento di Ingegneria Industriale e

dell'Informazione

cINFN Sezione di Pavia

#### **Motivation**

- Development of an analog front-end in a 65 nm CMOS mixed-signal chip for readout of high granularity silicon pixel sensors for particle tracking in the innermost layers of ATLAS and CMS at HL-LHC: the international RD53 collaboration and the INFN CHIPIX65 group

- Demanding specifications for noise, threshold dispersion, minimum threshold, power dissipation, area, tolerance to extremely high levels of ionizing radiation,...

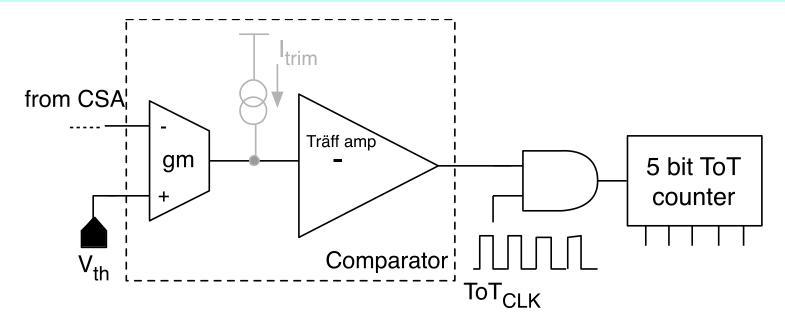

- This paper will discuss one of the proposed solutions for the front-end: an asynchronous analog pixel cell with continuous time charge sensitive preamplifier and discriminator for ToT-based A/D conversion, local DAC for threshold adjustment

- This front-end was integrated in single channel prototypes, in the CHIPIX65 demonstrator and in the RD53A large scale demonstrator: discussion of test results available so far

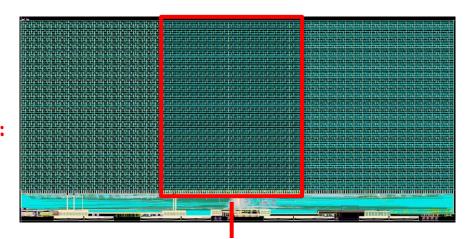

#### The CHIPIX65 demonstrator chip

3.5 mm 5.1 mm

64x64 matrix, 50x50 µm² pixel

- Two analog front-end architectures

- 5-bit ToT signal digitization, max ToT = 400 ns

- Minimum threshold < 600 e-, In-time threshold

- < 1200 e<sup>-</sup>

- Noise ~100 e rms with no sensor connected

- 2x2 Analog Islands on 4x4 pixel region digital architecture

- FE & IP-blocks developed in RD53

INFN (Bari, Lecce, Milano, Padova, Pavia, Perugia, Pisa and Torino)

"Analog island" concept

# The CHIPIX65 demonstrator chip and its two analog front-ends

- The CHIPIX65 demonstrator served the goal of testing design solutions (analog and digital) on a small-scale 65 nm CMOS chip, allowing for a performance evaluation before the integration of the large scale RD53A chip

- Two different analog front-end architectures were integrated in the pixel cells of the CHIPIX65 chip:

- a synchronous one with an autozero comparator (Torino)

- an asynchronous one (Bergamo/Pavia) implementing a linear pulse amplification in front of the discriminator, which compares the pulse to a threshold voltage (locally adjusted by a DAC)

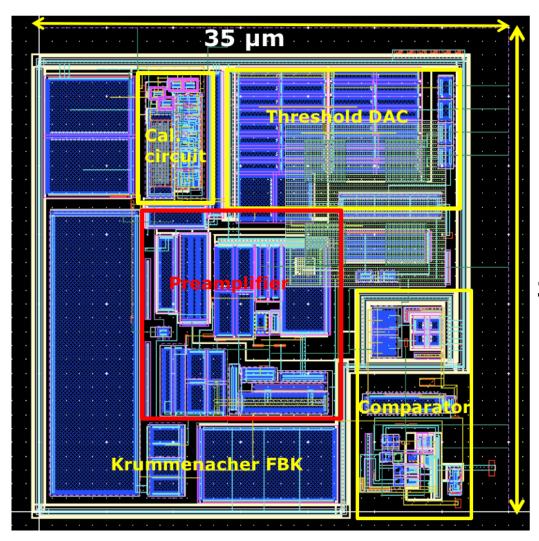

- Both front-ends were designed according to RD53A requirements, among which the capability of operating at a minimum threshold of 600 e<sup>-</sup>, with a power consumption not exceeding 4  $\mu$ W in a silicon area of 35  $\mu$ m  $\times$  35  $\mu$ m

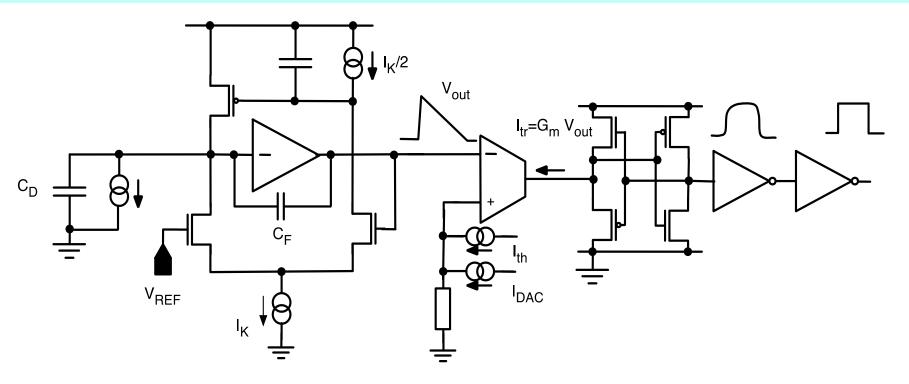

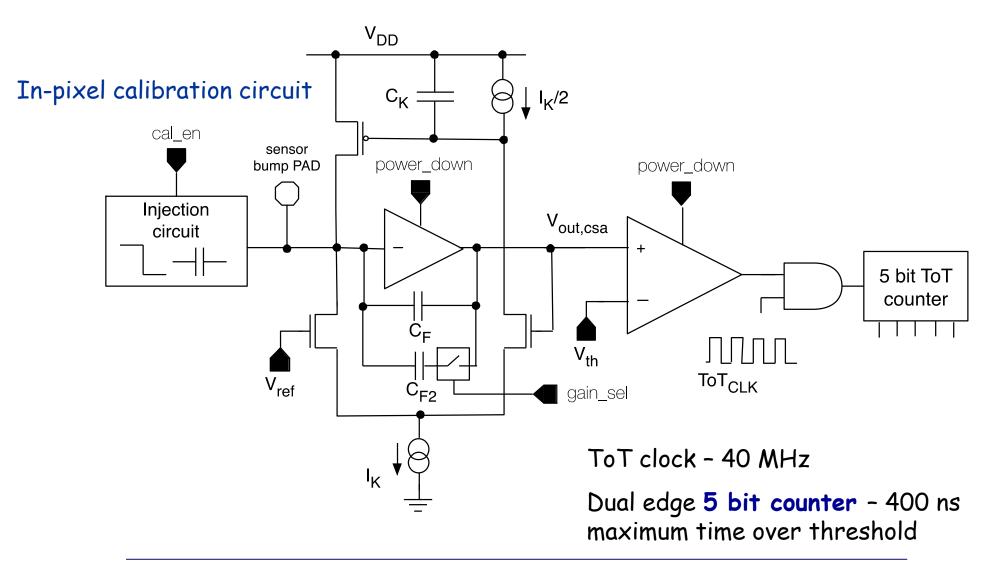

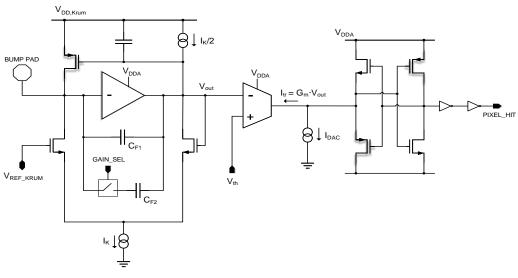

#### The asynchronous analog front-end in the CHIPIX65 demo chip

- Single amplification stage for minimum power dissipation

- Krummenacher feedback to comply with the expected large increase in the detector leakage current

- High speed, low power current comparator

- 4 bit local DAC for threshold tuning

- 30000 electrons maximum input charge, ~450 mV preampli output dynamic range

- Selectable gain and recovery current

- Overall current consumption: ~4 μA

#### The asynchronous analog front-end in the CHIPIX65 demo chip

### Layout of the asynchronous analog cell

- · Analog FE in DNW

- Local routing M1,M2,M3

M3 pins to Digital FE

35 µm

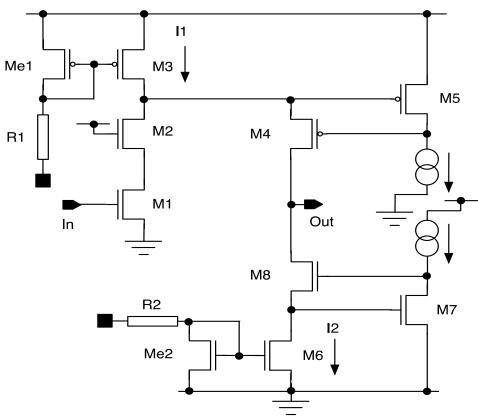

#### Schematics

#### **Preamplifier**

• Gain stage based on a **folded cascode** configuration (~3  $\mu$ A absorbed current) with a regulated cascode load

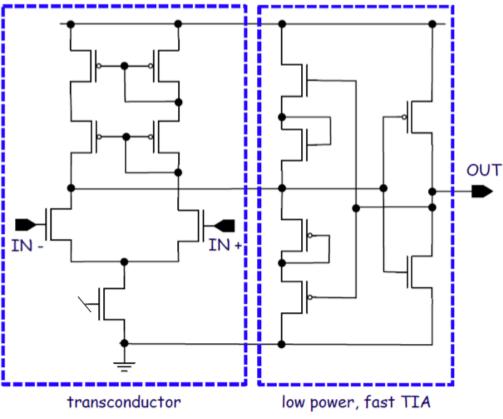

#### Comparator

Low power, fast discriminator ( $\sim 1~\mu A$  absorbed current) including Gm stage and a transimpedance amplifier providing a low impedance path for fast switching

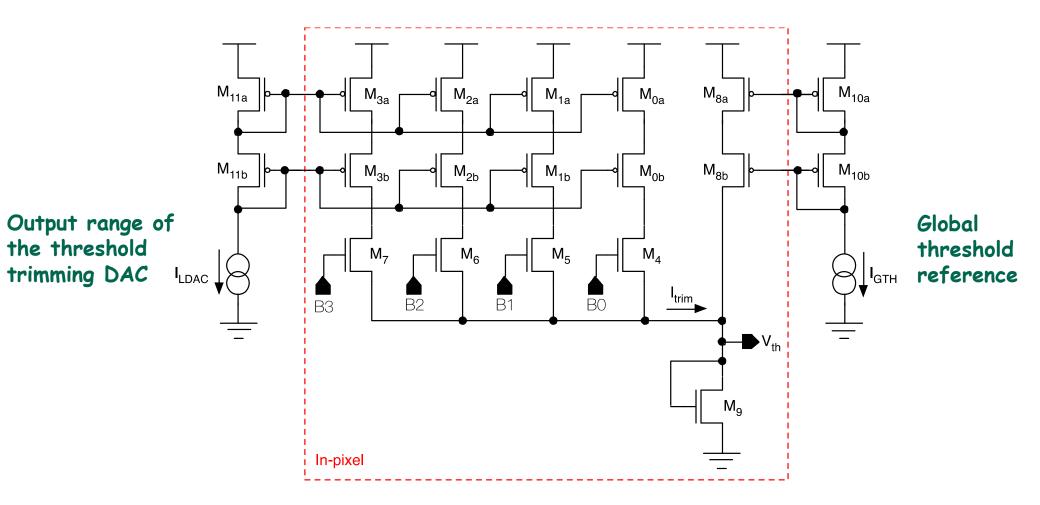

#### 4-bit Threshold DAC

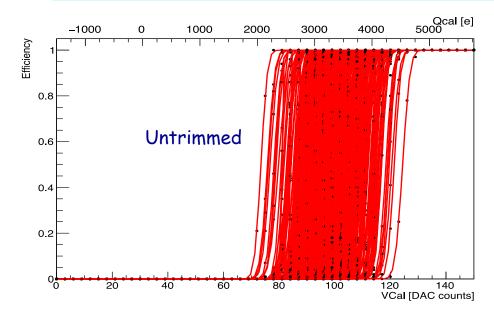

#### Experimental results: threshold dispersion and noise

Injected charge [e-]

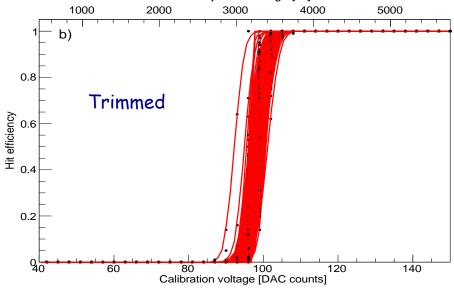

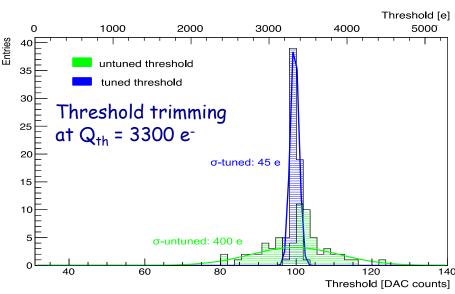

- All pixels tested and fully working

- $\approx$  400 e rms untrimmed threshold dispersion

- per-pixel DAC codes extracted from untrimmed S-curves using a set of ROOT macros and then loaded into the chip

- ≈ 45 e rms trimmed threshold dispersion, in good agreement with CAD simulations

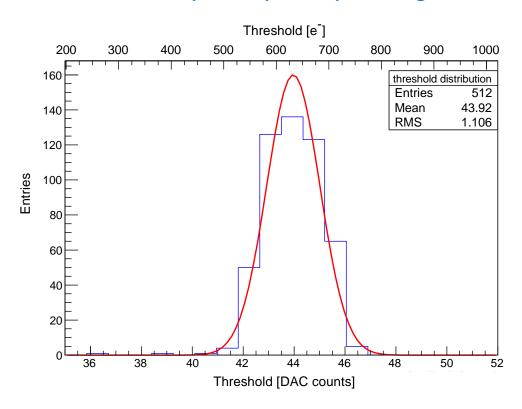

#### Threshold dispersion at $Q_{th} \approx 600$ electrons

#### The capability of operating at low threshold settings is demonstrated

Threshold dispersion [e rms] ILDAC [DAC counts]

Threshold dispersion  $\sigma(Q_{th}) \approx 55$  e rms after tuning at 600 electrons threshold  $Q_{th}$

Optimum threshold DAC range at about 2000 electrons corresponding to about  $5 \times \sigma(Q_{th})$  before tuning

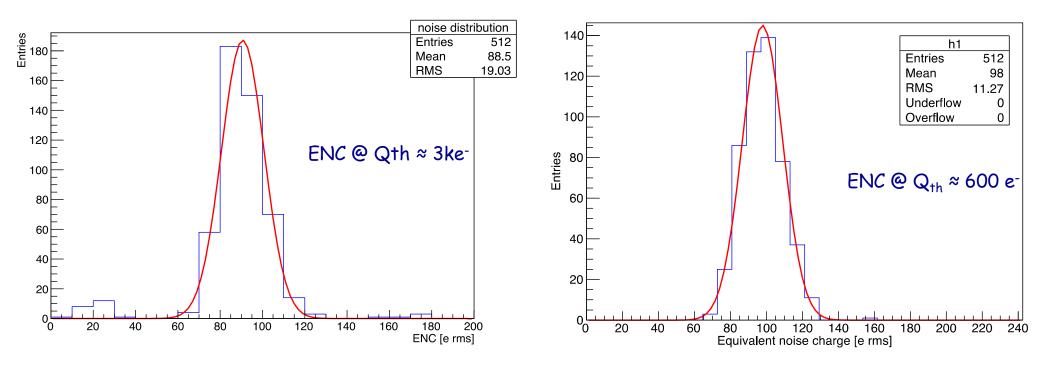

#### Low noise operation at low threshold setting

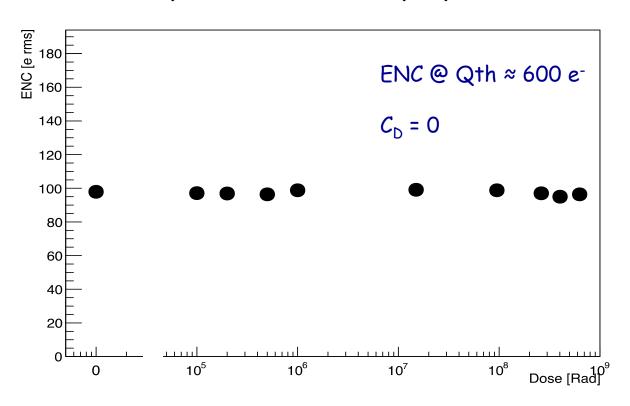

Mean ENC ≈ 90 e rms before irradiation (no sensor connected)

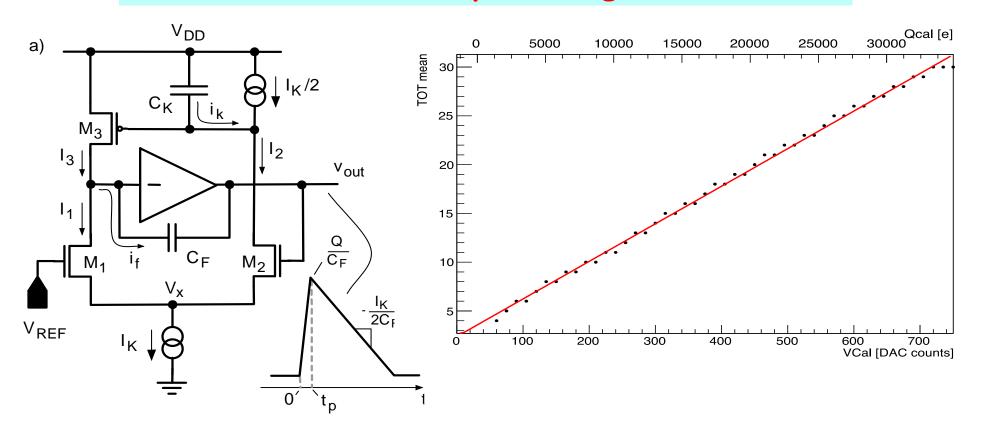

# Time-over-Threshold linearity as a function of the input charge

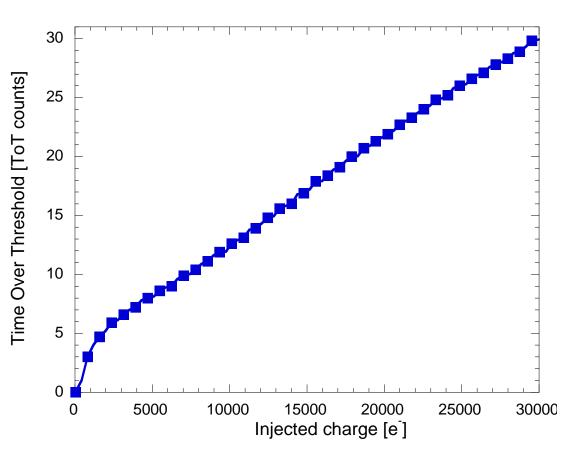

- ToT as a function of the injected charge for a single pixel of the matrix

- very good linearity for the 5-bit ToT, corresponding to a constant current discharge of the preamplifier feedback capacitor (also at relatively small input charges)

# Time-over-Threshold linearity as a function of the input charge

At input charge  $Q_{in}$  large enough to saturate the Krummenacher feedback, the preamplifier feedback capacitor is linearly discharged by a constant current  $I_{\kappa}/2$ :

$$ToT = 2\frac{Q_{in} - Q_{th}}{I_K}$$

The value of  $I_K$  (25 nA) is set according to the maximum ToT (400 ns) over the expected  $Q_{in}$  range (30 ke<sup>-</sup>).

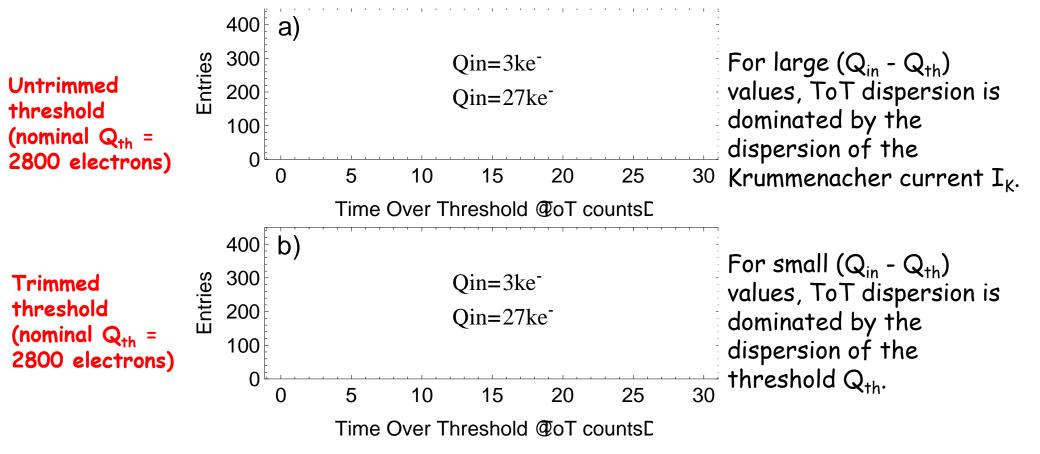

ToT is affected by the threshold dispersion and by channel-to-channel mismatch of the Krummenacher feedback current  $\mathbf{I}_{\mathsf{K}}$

#### Time-over-Threshold dispersion

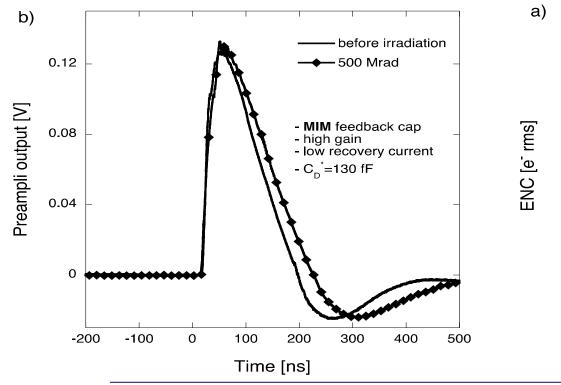

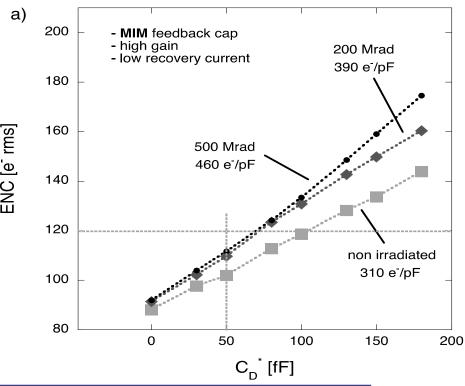

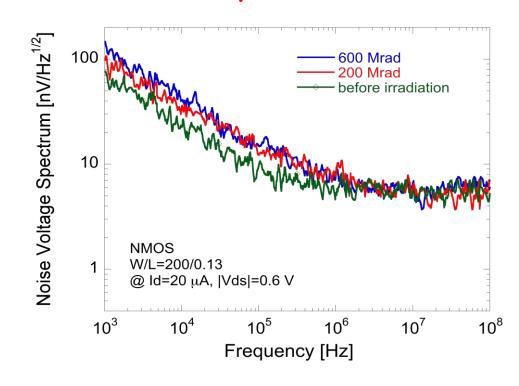

#### Irradiation tests up to 500 Mrad TID: single channels

- Prototypes of the front-end exposed to 3 MeV protons and to 10 keV X-rays (room T)

- The analog channel remains fully functional up to 500 Mrad TID; moderate noise increase is due to 1/f noise degradation in preamplifier input device

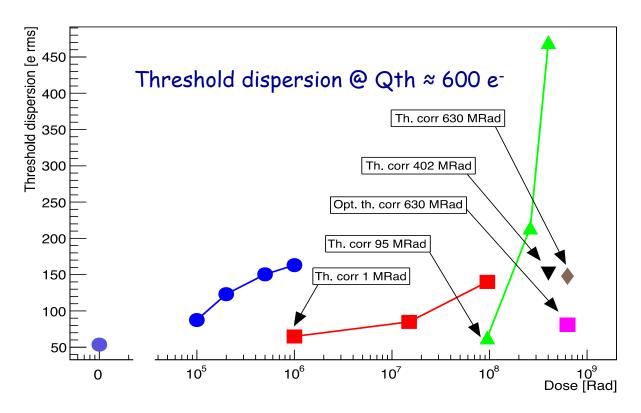

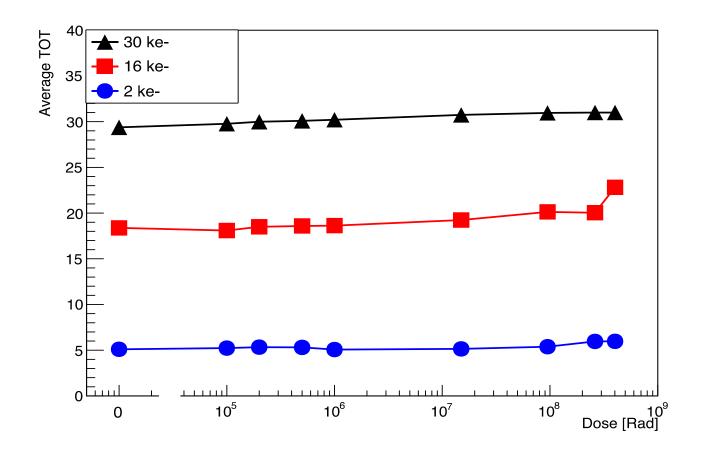

### CHIPIX65 demonstrator chip with the Pavia/Bergamo front-end exposed to 10 keV X-rays up to 630 Mrad

- 1 sample irradiated with X-rays at Padova INFN at room temperature

- Chip biased at nominal operating conditions

- 350 krad/h dose rate for TID < 15 Mrad</li>

- 3.5 Mrad/h dose rate for TID > 15 Mrad

- chip fully-functional at 630 Mrad TID and one week room temperature annealing (need to restore operation of digital readout)

- Threshold trimming performed @ 1Mrad, 95 Mrad, 402 Mrad and 630 Mrad

- After trimming, the threshold dispersion does not exceed about 80 e rms even at the highest TID values

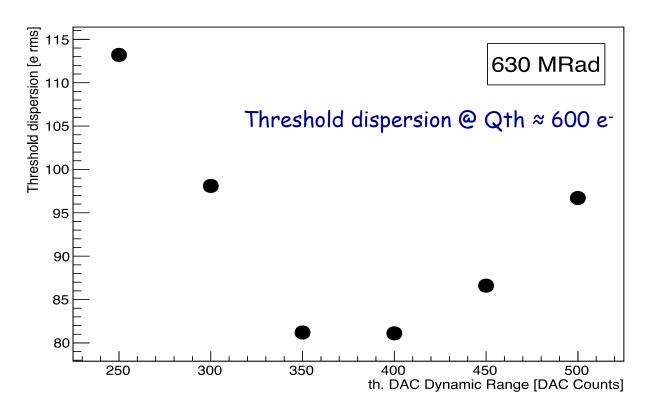

Optimizing threshold dispersion (630 Mrad, 3 weeks annealing at room T)

also requires an adjustment of the threshold DAC dynamic range (up to

3000 electrons)

Average ToT evaluated at 2k, 16k and 30k electrons

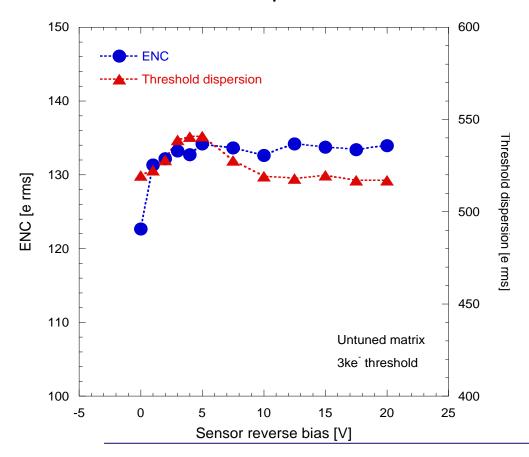

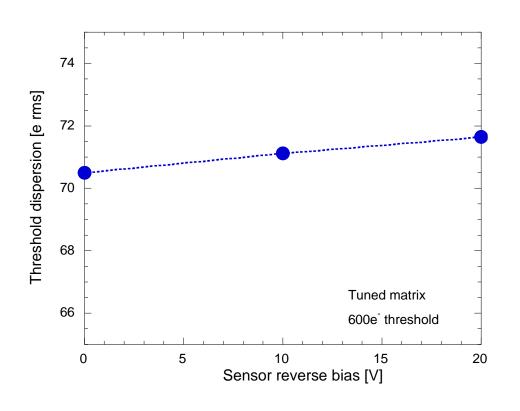

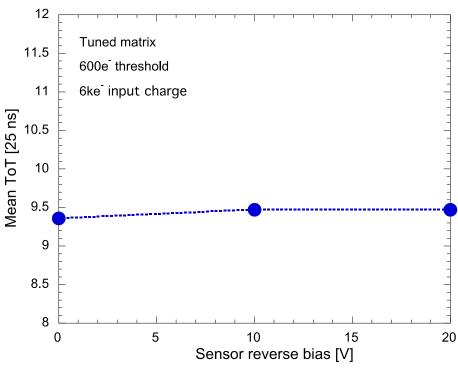

#### Tests with 3D pixel sensors

- bump-bonding performed at SLAC with FBK 3D pixel sensors (2016 wafers) (acknowledgements to G.F. Dalla Betta and M. Meschini, and to INFN Torino group)

- sample prototypes coupled to 50  $\mu$ m  $\times$  50  $\mu$ m pixels, sensor capacitance of about 50 fF (+ about 50 fF from parasitics associated with bumps)

#### Tests with 3D pixel sensors: threshold tuning

The asynchronous analog channel can be operated at low threshold also when it is connected to a sensor

### Front-end integration in RD53A

RD53A is intended to demonstrate in a large format IC ( $20 \times 11.8 \text{ mm}^2$ ) the suitability of the chosen 65nm CMOS technology for HL-LHC upgrades of ATLAS and CMS

RD53A integrates an improved version of the CHIPIX asynchronous (aka "Linear") front-end:

- Isolation strategy: two DNWs (analog+digital) in RD53A / only analog FE in DNW in CHIPIX65

- Dedicated Krummenacher power supply → ToT less sensitive to voltage drop on power suppl lines

- Threshold tuning implemented at the transconductor output node → VTH less sen temperature and TID

- Increased charge sensitivity → improved the dispersion performance

- Analog inverters for most of the configuration

→ improved digital noise immunity

- In-pixel protection diodes for most of the analog bias lines

lay 23, 2018 23

### Threshold trimming in the linear front-end of RD53A

CHIPIX65 asynchronous front-end: tuning range completely defined by the characteristics of the trimming DAC, but threshold setting rather sensitive to temperature. Additional threshold dispersion contribution from gradients across a large chip

RD53A linear front-end: programmable current injected at the output of the transconductance stage of the comparator, instead of generating a threshold voltage at its input; tuning capability also depends on the transconductance of the comparator input device

#### **Conclusions**

- Test results confirm that the proposed continuous-time analog front-end complies with the specifications set by RD53, in view of the development of 65 nm CMOS readout pixel chips for the innermost detector layers of ATLAS and CMS (radiation tolerance, noise, stable low threshold operation)

- This analog front-end was integrated in the large scale demonstrator chip RD53A and in an upgraded version of the CHIPIX65 demo chip; test results will be discussed in the RD53A talk by F. De Canio

- An evaluation of different front-end architectures is required for the next step: the design of the actual chip for the HL-LHC experiments

### **Backup slides**

| RD53A specifications [CERN-RD53-PUB-15-001] |                                                                    |

|---------------------------------------------|--------------------------------------------------------------------|

| Technology                                  | 65 nm CMOS                                                         |

| Pixel size                                  | 50 x 50 um <sup>2</sup>                                            |

| Pixels                                      | 192 x 400 = 76800 (50% of production chip)                         |

| Detector capacitance                        | < 100fF (200fF for edge pixels)                                    |

| Detector leakage                            | < 10nA (20nA for edge pixels)                                      |

| Detection threshold                         | < 600e <sup>-</sup>                                                |

| In-time threshold                           | < 1200e <sup>-</sup>                                               |

| Noise hits                                  | < 10 <sup>-6</sup>                                                 |

| Hit rate                                    | < 3 GHz/cm <sup>2</sup> (75 kHz avg. pixel hit rate)               |

| Trigger rate                                | Max 1 MHz                                                          |

| Trigger latency                             | 12.5 us                                                            |

| Hit loss at max hit rate (in-pixel pile-up) | ≤ 1%                                                               |

| Charge resolution                           | ≥ 4 bits ToT (Time over Threshold)                                 |

| Readout data rate                           | 1-4 links @ 1.28Gbits/s = max 5.12 Gbits/s                         |

| Radiation tolerance                         | 500Mrad, 1 x 10 <sup>16</sup> 1Mev eq. n/cm <sup>2</sup> at -15 °C |

| SEU affecting whole chip                    | < 0.05/hr/chip at 1.5GHz/cm² particle flux                         |

| Power consumption at max hit/trigger rate   | < 1W/cm <sup>2</sup> including SLDO losses                         |

| Pixel analog/digital current                | 4 uA / 4 uA                                                        |

| Temperature range                           | -40°C ÷ 40°C                                                       |

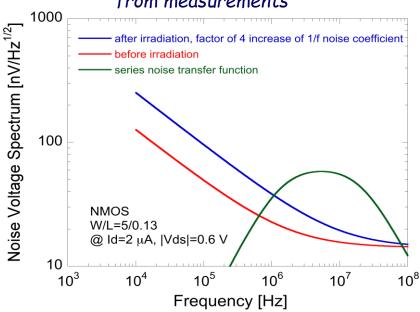

# 65 nm NMOSFETs - up to 600 Mrad low current density

- Moderate 1/f noise increase, no increase in the white noise region is detected

- The behavior as a function of the current density is different at high TID, as compared to 10 Mrad

- At 200 Mrad (and even 600 Mrad), at low I<sub>D</sub> 1/f noise increase with respect to pre-irradiation values is smaller than at 10 Mrad

## Ionizing radiation effects on the signal-to-noise ratio in a pixel readout channel

- The noise data reported here can provide the basis to estimate the performance of an analog front-end for pixel detectors at extremely high TID

- Even at a signal peaking time of 25 ns, radiation-induced 1/f noise increase has an effect in the bandwidth of an analog channel (input transistor operates at very small I<sub>D</sub>, in the low current density region)

- Using realistic parameters for 65nm CMOS pixel front-end prototypes developed in the frame of RD53, a 15 20% ENC increase (from 120 to 140 e rms at 100 fF  $C_D$ ) can be predicted, which is consistent with measurements on irradiated chips

Noise voltage spectrum of NMOS,W/L = 5/0.13, before irradiation and at 600 Mrad TID, calculated using data from measurements

Transfer function of a shaperless front-end with 25 ns peaking time superimposed to the spectra