## The Phase-II Upgrade of the ATLAS **Monitored Drift Tube Detector** and Frontend Electronics

Hubert Kroha - Max-Planck-Institute for Physics, Munich, Germany --- on behalf of the ATLAS Collaboration

#### Goals of the Muon Detector Upgrade for High-Luminosity LHC

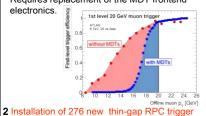

1 Increase of the 1st level muon trigger selectivity and p<sub>T</sub> resolution by factor 10 by implementing a fast track trigger based on the Monitored Drift Tube (MDT) precision tracking chambers Requires replacement of the MDT frontend

chambers with longer lifetime at HL-LH in the barrel inner layer BI, combined with 96 new small-diameter muon drift tube (sMDT) chambers in the small azimuthal (BIS) sectors.

16 BIS 78 chambers already for LHC Run 3

# Improved barrel trigger coverage with more hit coincidences

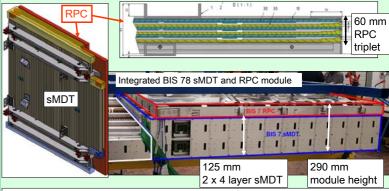

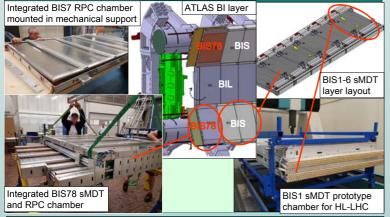

#### Integrated Thin-Gap RPC and sMDT Chambers

Installation of new triplet RPC chambers in the BIS layer requires replacement of the existing MDT chambers by sMDT chambers to provide sufficient radial space Independent interleaved supports on common rail system

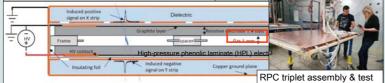

#### **New Thin-Gap Resistive Plate Chambers**

Reduction of gap thickness from 2 mm to 1 mm and new highly sensitive preamplifiers

allow for operation at 5.8 kV instead of 9.6 kV and 15 times lower gas gain.

⇒ increased rate capability of > 10 kHz/cm² and lifetime 2.5 times requirement for HL-LHC. BIS78 RPC construction in progress

Design optimization for Phase-II upgrade

Efficiency vs. HV

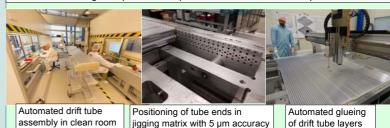

### New Small-Diameter Muon Drift Tube (sMDT) Chambers

Reduction of driftt tube diameter from 30 mm to 15 mm and otherwise unchanged operating conditions increases the rate capability to > 30 kHz/cm<sup>2</sup>.

14 sMDT chambers operated in ATLAS in run 2. 5 µm wire positioning accuracy achieved BIS78 sMDT chamber construction completed (pilot project for the Phase-II upgrade). BIS1-6 sMDT design completed. Serial production in 2020-2023 at two production sites

#### BIS sMDT and RPC Chambers for Run 3 and HL-LHC

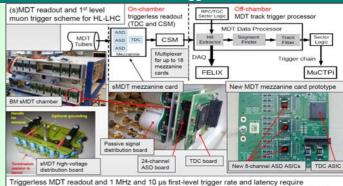

#### MDT Frontend Electronics and Triggerless Readout for HL-LHC

Triggerless MDT readout and 1 MHz and 10 µs first-level trigger rate and latency require — replacement of 20000 MDT and prod. of 2000 new MDT mezzanine cards (prototypes exist), 64 FPGA-based first-level muon track trigger processors, performing pattern recognition and track & momentum reconstr. within 300 ns at HL-LHC bg. rates (demonstrated on prototype HW)

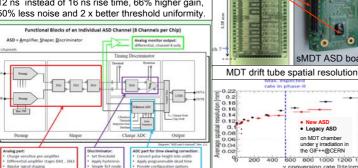

#### New ASD ASIC Functionality and Performance

ASD chip design and engineering run completed in IBM/Global Foundries 130 nm CMOS technology. Same functionality as the legacy chip but with 12 ns instead of 16 ns rise time, 66% higher gain. 50% less noise and 2 x better threshold uniformity.

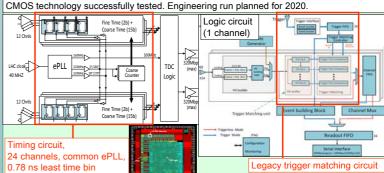

#### New TDC ASIC Functionality and Performance

The TDC chip combines the new continuous readout mode for HL-LHC operation with the legacy triggered mode needed for chamber testing. Full prototype chip in TSMC 130 nm

sMDT ASD board