## A PCI Express board proposed for the upgrade of the ATLAS TDAQ read-out system

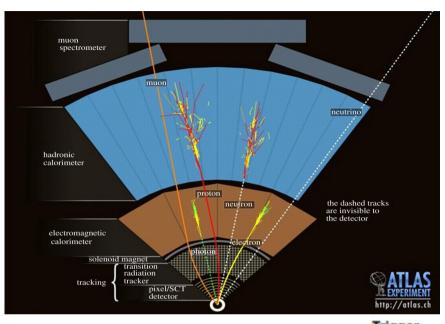

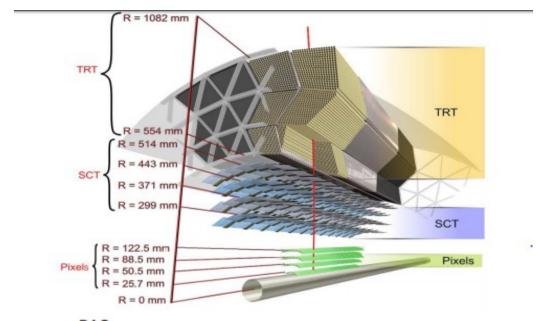

The ATLAS Experiment

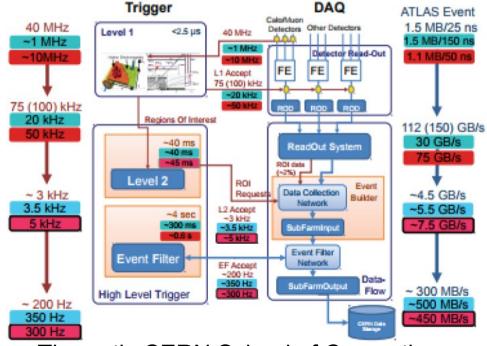

The importance of DAQ upgrade

Hardware proposed for the ATLAS Upgrade (Hardware features) (Low and High level control system)

## The ATLAS Experiment

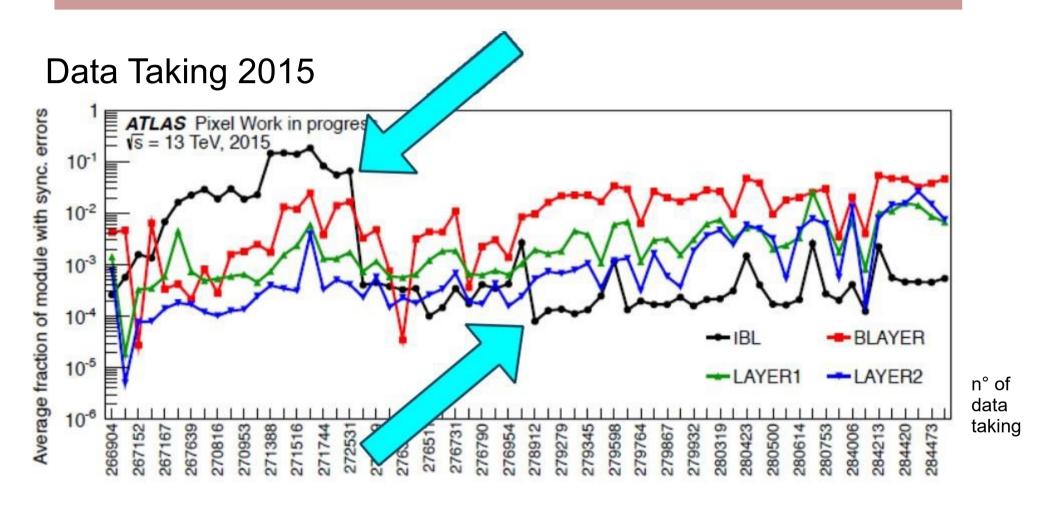

# The Importance of Data Aquisition System Firmware

The black plot show how the synchronization errors goes down after the <u>firmware upgrade</u> of the IBL's ROD. Now the sync errors are below the other ROD's layer that were not yet upgraded

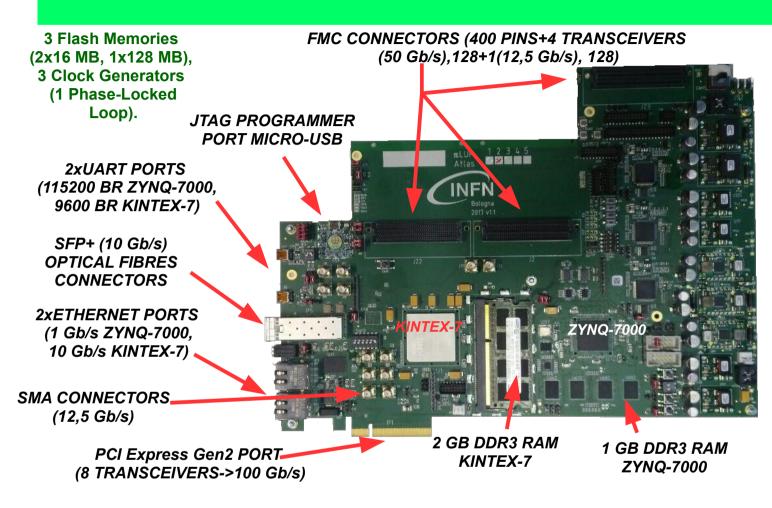

#### Hardware proposal for the ATLAS upgrade (PILUP)

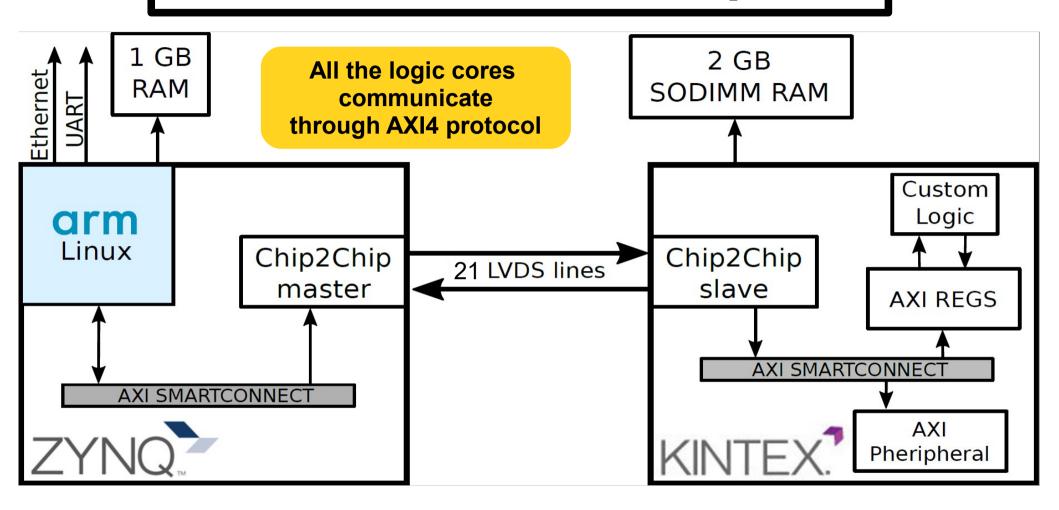

- 28 nm FPGAs (xc7z020-1clg484c & xc7k352t-2ffg900c);

- 21 differential bus at 200

MHz DDR between the FPGAs;

- Zynq-7000=>Master with an <u>ARM Cortex-A9 Dual-</u> <u>Core processor;</u>

- Kintex-7=>Slave with <u>16</u> fast links transceivers up to 12,5 Gb/s.

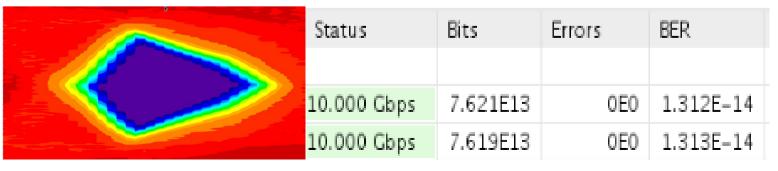

Bit Error Rate of the transceivers I/O (includes the PCI Express Gen2) down to 10<sup>-14</sup> (10 hours of run)

### Structure of the control system

- Embedded Linux system running on the ARM processor;

- Complete **low-level control** from the Zynq-7000 and **high-level management** of the system from external interfaces;

- **AXI4** addressable register block to control custom logic without AXI4 interface.

#### **Protocol Converter**

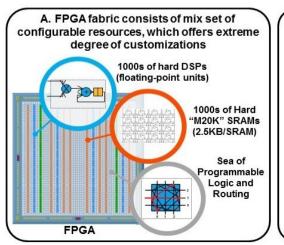

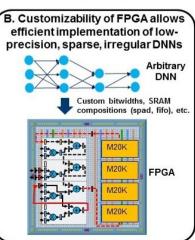

FPGA fabric is great for irregular (and regular) computation