# SEU Mitigation in the ATLAS SCT

Dave Robinson

Cavendish Laboratory, University of Cambridge, UK

On behalf of the SCT Collaboration

The SCT SEU sensitivity Mitigation

Radiation Effects at the LHC Experiments and Impact on Operation and Performance 23-24 April 2018

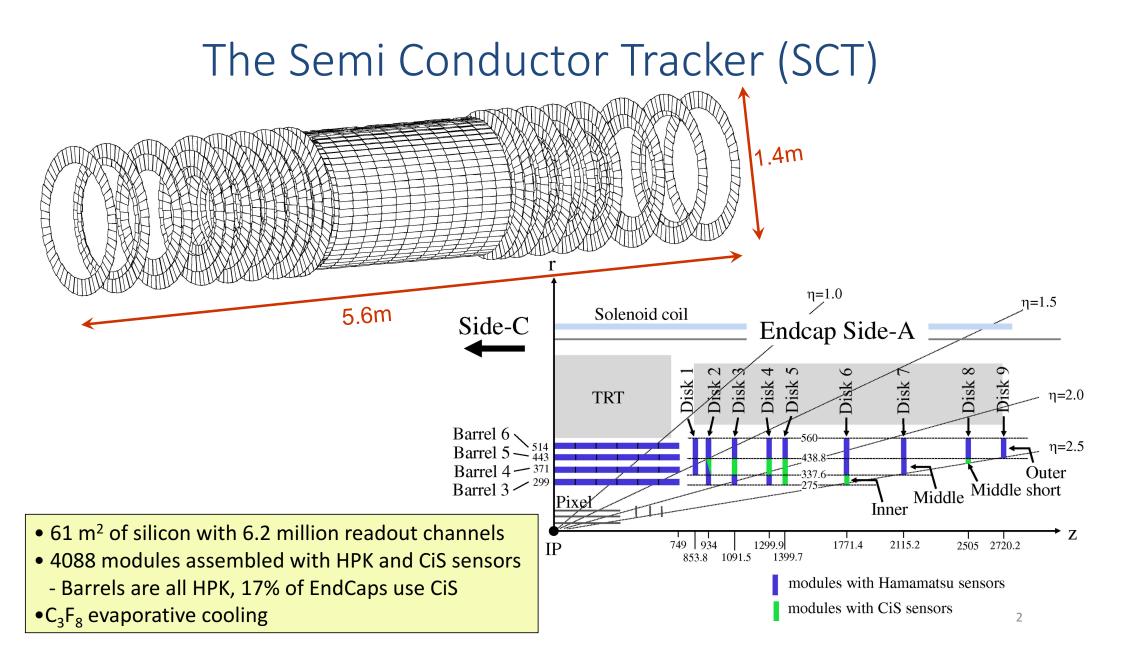

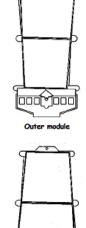

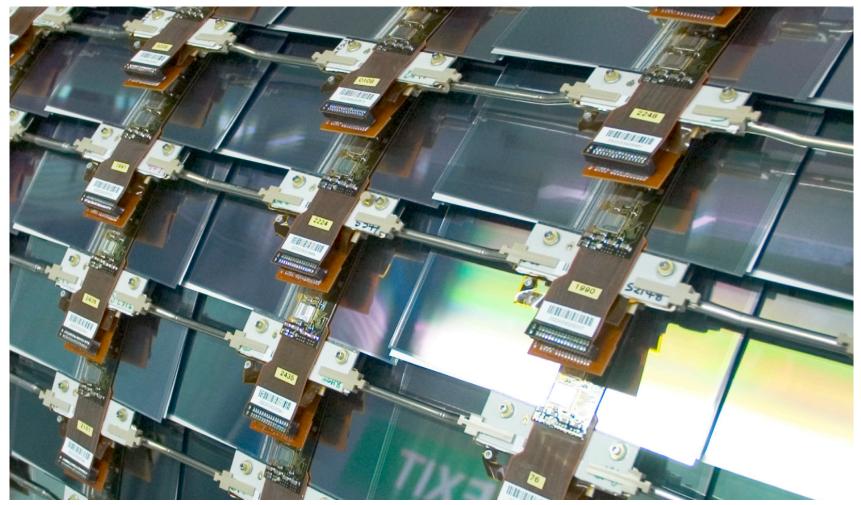

## The SCT Modules

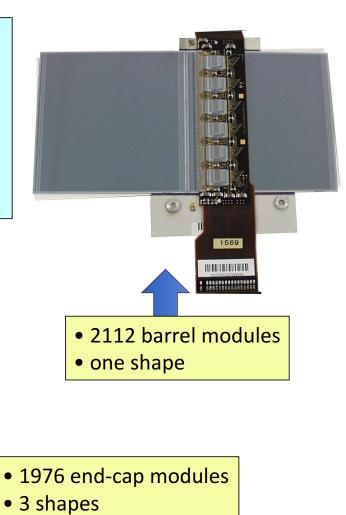

- Back-to-back sensors, glued to highly thermally conductive substrates for mech/thermal stability, wire-bonded to form ~12cm long strips

- 40mrad stereo angle between strips on opposite sides

- 6 FE chips (ABCD3TA) on each side

- One command stream, two data streams

- Nominal HV 150V (standby 50V)

### The ABCD3TA ASICs

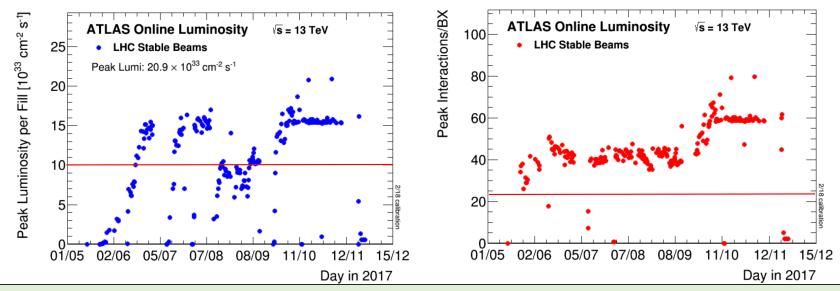

### SCT Operating Conditions at the LHC

- The ATLAS tracker was designed for a nominal luminosity of  $1x10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> with a <µ> of ~23 at 70kHz L1 rate

- This has been routinely exceeded since 2016, with ATLAS striving for a L1 trigger rate of 100Hz to fully exploit physics potential

- Three distinct challenges:

- Online data processing, bandwidth limitations, radiation damage mitigation

## Radiation Damage – Impact on SCT Operations

|                                           | <ul> <li>Leakage Currents</li> <li>Increased by ~5 orders of magnitude since start of Run-1</li> <li>Trip limits adjusted after several months</li> </ul>                                      |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | <ul> <li>Depletion Voltage</li> <li>Type inversion already in innermost barrel</li> <li>We still operate with nominal 150V HV</li> </ul>                                                       |

| Static Configuration<br>updated as needed | <ul> <li>Noise &amp; gain</li> <li>Largely stable, regular calibrations</li> </ul>                                                                                                             |

|                                           | <ul> <li>ABCD Shaper/preamp current</li> <li>Signal amplification and shaping – still with default settings!</li> <li>Optimise noise/gain while scan shaper and preamp DAC settings</li> </ul> |

|                                           | <ul> <li>Chip thresholds</li> <li>Channel trim adjustments every ~few weeks</li> </ul>                                                                                                         |

| Monitored                                 | <ul> <li>On-detector optical system</li> <li>IPINs, VCSEL</li> </ul>                                                                                                                           |

| Addressed on the fly during operations    | <ul> <li>SEU</li> <li>Rate is function of luminosity</li> </ul>                                                                                                                                |

## Radiation Damage – Impact on SCT Operations

| Static Configuration<br>updated as needed | <ul> <li>Leakage Currents         <ul> <li>Increased by ~5 orders of magnitude since start of Run-1</li> <li>Trip limits adjusted after several months</li> </ul> </li> <li>Depletion Voltage         <ul> <li>Type inversion already in innermost barrel</li> <li>We still operate with nominal 150V HV</li> </ul> </li> <li>Noise &amp; gain         <ul> <li>Largely stable, regular calibrations</li> </ul> </li> </ul> |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | <ul> <li>ABCD Shaper/preamp current</li> <li>Signal amplification and shaping – still with default settings!</li> <li>Optimise noise/gain while scan shaper and preamp DAC settings</li> </ul>                                                                                                                                                                                                                              |

|                                           | <ul> <li>Chip thresholds</li> <li>Channel trim adjustments every ~few weeks</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

| Monitored                                 | On-detector optical system     IPINs, VCSEL     Tony Weidberg                                                                                                                                                                                                                                                                                                                                                               |

| Addressed on the fly during operations    | SEU     Rate is function of luminosity     This talk                                                                                                                                                                                                                                                                                                                                                                        |

### SCT SEU vulnerabilities

#### SCT SEU vulnerabilities

- 1. Pipeline single data error

- 2. Static registers, eg configuration

#### Energy deposition in *p-i-n* diode

(*p-i-n* has relatively large active volume so small energy is sufficient before amplification)

#### Trigger is '110'

- bit flip loses trigger, desync of module

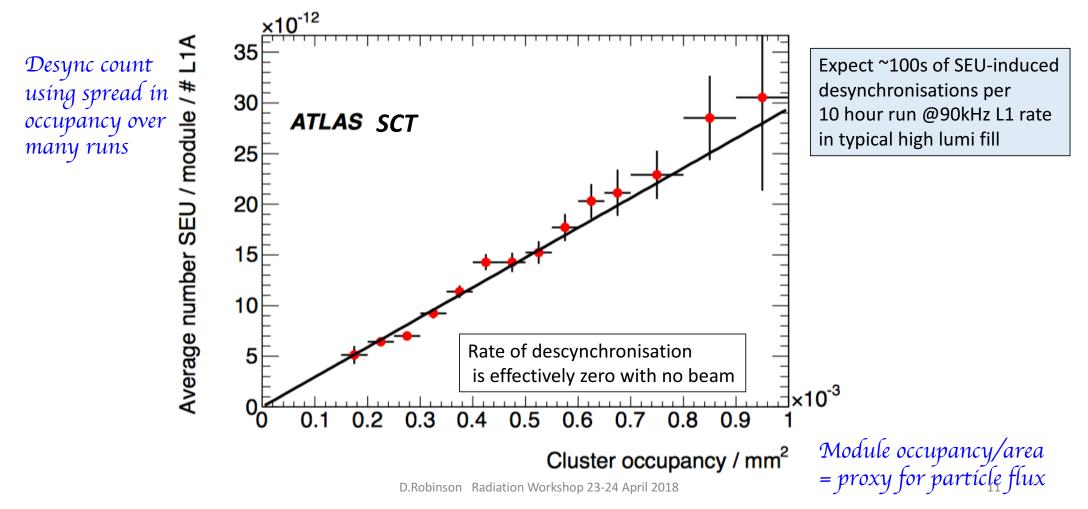

## Evidence for module desynchronisation by SEU

"Smoking gun" is that desync error rate should scale with particle flux...

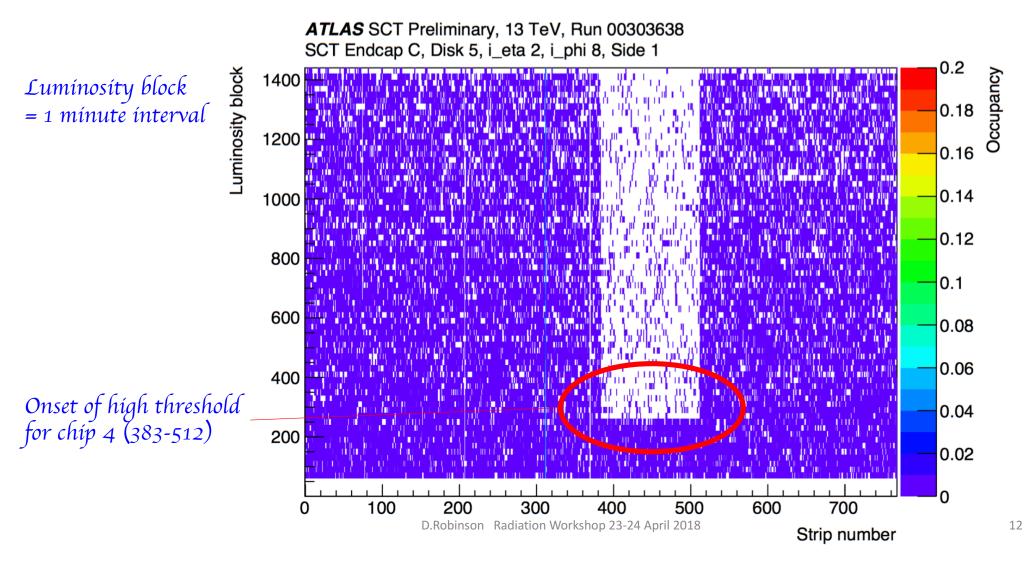

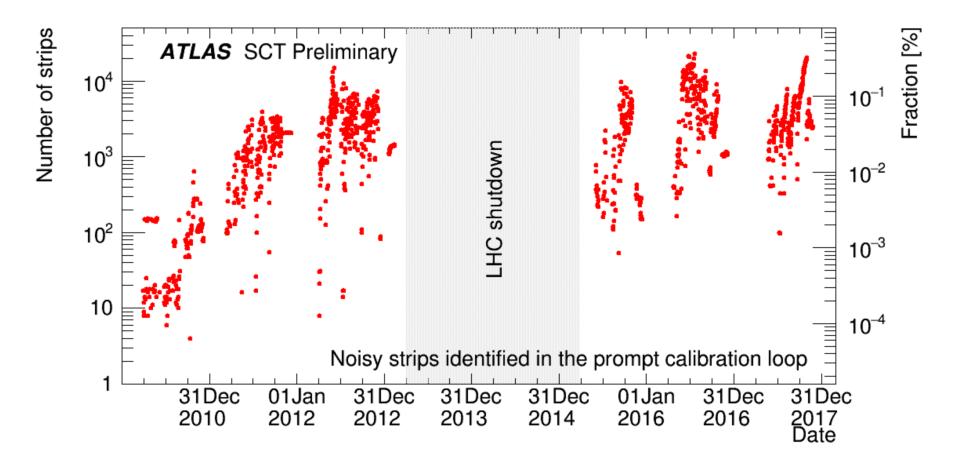

### Evidence for chip configuration bit flip by SEU

## Expected SEU Rates

derived from test beam studies

When SCT was first being designed, we were not aware of SEUs and their potential to disrupt data taking!

- P-i-n diodes in SCT opto packages

- Test beam studies Nucl. Instrum. Meth. A 481 (2002) 575.

- Threshold for energy deposition @ Ipin=100uA for SEU is 2.3MeV

- SEU x-section measurable for 14.1 MeV neutrons, 450 MeV protons and 300-450 MeV pions

- Prediction vs measurement for ~7fb<sup>-1</sup> data sample : 1900 vs 2405

- 2014 JINST 9 C01050

- ABCD configuration registers

- Test beam studies Nucl. Instrum. Meth. A 552 (2005) 292

- Study rate of bit flips with 200MeV pions and 24 GeV protons

- For 3x10<sup>14</sup> hadrons.cm<sup>-2</sup>

- 3x10<sup>-6</sup> SEUs/s/module, ie few hundred bit flips per typical 10 hour run

- Factor ~3 discrepancy between predicted (test-beam) and measured rates

- based on study of bit flips  $1 \rightarrow 0$  in threshold registers, from count of noisy chip rate

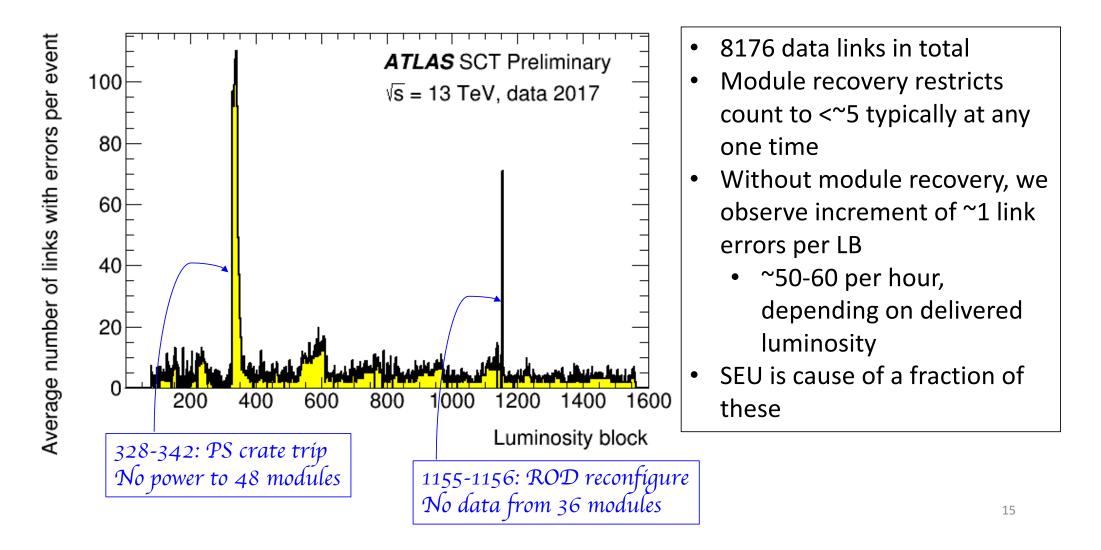

## SEU Mitigation – module desynchronisation

- We sample online HLT-triggered ATLAS data

- Using standard monitoring framework within ATLAS TDAQ

- would be better to trap events in the ROD, but...

- Continuously monitor and publish SCT flagged errors

- Watchdog requests reconfiguration of indiviual module(s) with errors

|                                                     | Action                     | Error(s) on module data link               |              |

|-----------------------------------------------------|----------------------------|--------------------------------------------|--------------|

| Repeat if necessary<br>with reset or<br>power cycle | Normal data taking         | None                                       |              |

|                                                     | SEU provokes desync        | L1 mismatch                                |              |

|                                                     | Mask off link at ROD level | Timeout/mask (empty data)                  |              |

|                                                     | Reconfigure module         | Timeout/mask (empty data)                  | About 10-20s |

|                                                     | Re-enable mask             | BCID mismatch, L1ID mismatch               |              |

|                                                     | Normal data taking         | None (after next BCR and ECR respectively) |              |

Same mechanism for non-SEU configuration issues...

### Suppression of link errors by module recovery

#### Impact of bit flips on ABCD configuration

#### Threshold/Calibration DACs

|                        | -                                              |                                                                                                                                                                                                                                                              |                                               |                                                   |  |  |

|------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--|--|

|                        | 8-bit threshold (15:8) 8-bit calibration (7:0) |                                                                                                                                                                                                                                                              | High noise, or low efficiency                 |                                                   |  |  |

| Configuration Register |                                                |                                                                                                                                                                                                                                                              |                                               |                                                   |  |  |

| Bit                    | Name                                           | Function                                                                                                                                                                                                                                                     |                                               |                                                   |  |  |

| 0-1                    | Readout Mode                                   | Selects the data compression Criteria (see Table 3.6a)                                                                                                                                                                                                       |                                               | FE data compression: Anyhit, X1X, 01X, XXX        |  |  |

| 2-3                    | Cal_Mode<1:0>                                  | Selects the Calibration code (see Table 3.11). The state of these two bits also determines which channels are tested when Test Mode is enabled.                                                                                                              |                                               |                                                   |  |  |

| 4-5                    | Trim DAC range <1:0>                           | Selects the range of the trim DAC (see Table 3.1a)                                                                                                                                                                                                           |                                               | Channel by channel threshold spread               |  |  |

| 6                      | Edge_Detect                                    | Enables the edge detec                                                                                                                                                                                                                                       | tion circuitry in the input stage is enabled. |                                                   |  |  |

| 7                      | Mask                                           | When this bit is set the input register is disabled and the contents of the mask register are routed into the L1 pipeline.                                                                                                                                   |                                               | Invalid data                                      |  |  |

| 8                      | Accumulate                                     | When this bit is set the Accumulate function is enabled.                                                                                                                                                                                                     |                                               | Pipeline bit latched $\rightarrow$ 100% occupancy |  |  |

| 9                      | Input_Bypass                                   | This bit determines which set of token/data inputs are active.                                                                                                                                                                                               |                                               |                                                   |  |  |

| 10                     | Output Bypass                                  | This bit determines which set of token/data outputs are active.                                                                                                                                                                                              |                                               |                                                   |  |  |

| 11                     | Master                                         | When clear the chip acts as a Master providing the masterB input pin<br>has be asserted. This bit is "ored" with the value on the "masterB"<br>input. If the result is "0", the chip is placed into master mode.<br>Otherwise, it is placed into slave mode. |                                               | Chip sequencing $\rightarrow$ loss of chip data   |  |  |

| 12                     | End                                            | When set this bit confi                                                                                                                                                                                                                                      | gures the chip as the end of a readout chain. |                                                   |  |  |

| 13                     | Feed_Through                                   | When clear the chip outputs a 20MHz clock signal but only is the chip has been configured as a Master (see above)                                                                                                                                            |                                               | 20MHz clock if on Master                          |  |  |

| 14-15                  | not used                                       |                                                                                                                                                                                                                                                              |                                               | 16                                                |  |  |

|                        |                                                |                                                                                                                                                                                                                                                              |                                               | 4                                                 |  |  |

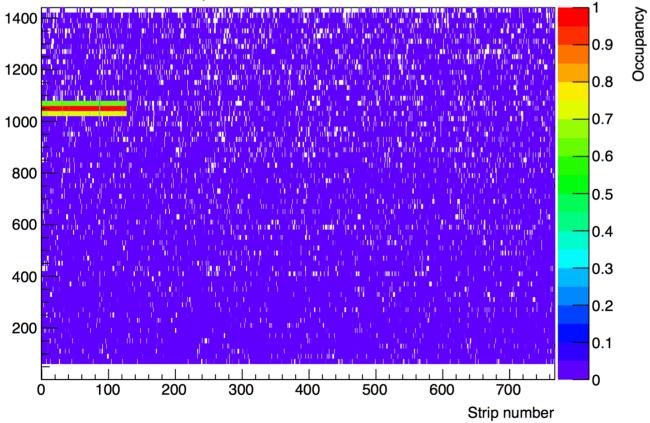

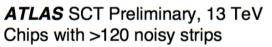

### SEU Mitigation - ABCD

We issue a Global Reconfiguration of the SCT every N lumiblocks (N currently set to 90)

Imposes dead time to ATLAS

for ~1.4 seconds

→ Overall impact on data

taking efficiency is negligible

**ATLAS** SCT Preliminary, 13 TeV, Run 00303638 SCT Barrel 3, i\_eta 5, i\_phi 19, Side 1

D.Robinson Radiation Workshop 23-24 April 2018

17

#### Suppression of SEU-induced ABCD misconfiguration by global recovery

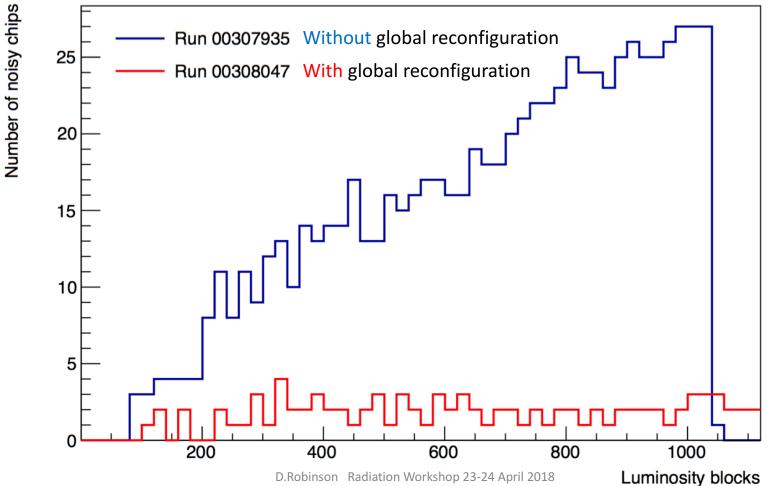

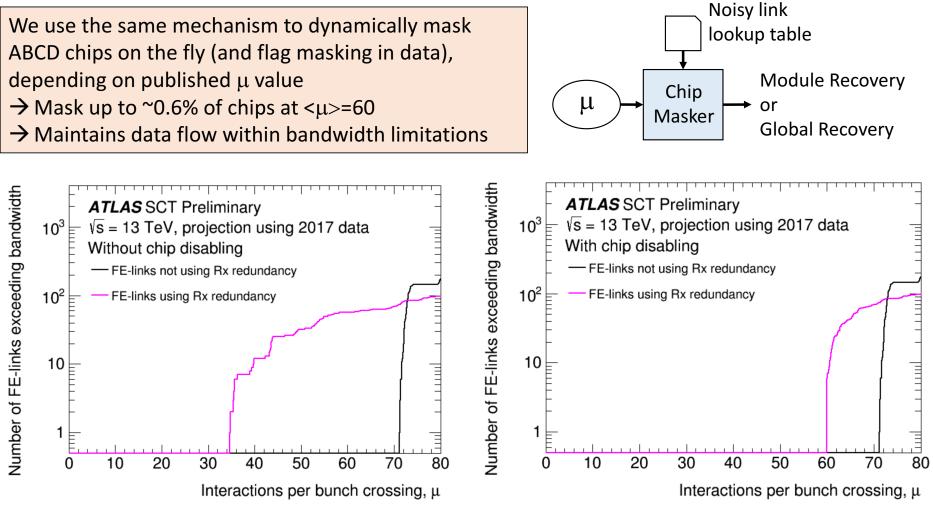

## Dealing with bandwidth constraints

D.Robinson Radiation Workshop 23-24 April 2018

## Summary

- The ATLAS SCT operates routinely at  $<\mu>\sim60$  with L1 rate 70-100kHz

- Recall the design goals were originally <µ> up to ~23

- We observe clear evidence of SEU effects

- Measured rate of SEUs is comparable with predictions from early testbeam tests using pions and protons

- Very effective SEU suppression is in place, combining regular global reconfigurations with targeted module reconfigurations

- Impact of SEUs, and of the mechanisms in place to suppress them, have negligible impact on SCT data taking efficiency and on SCT data quality

- Both >>99.9%

# BACKUP

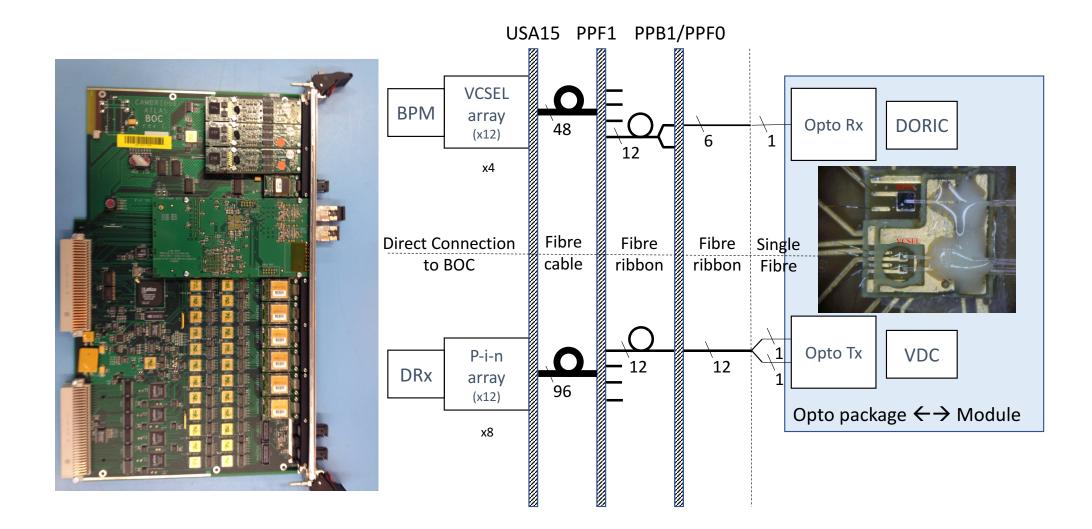

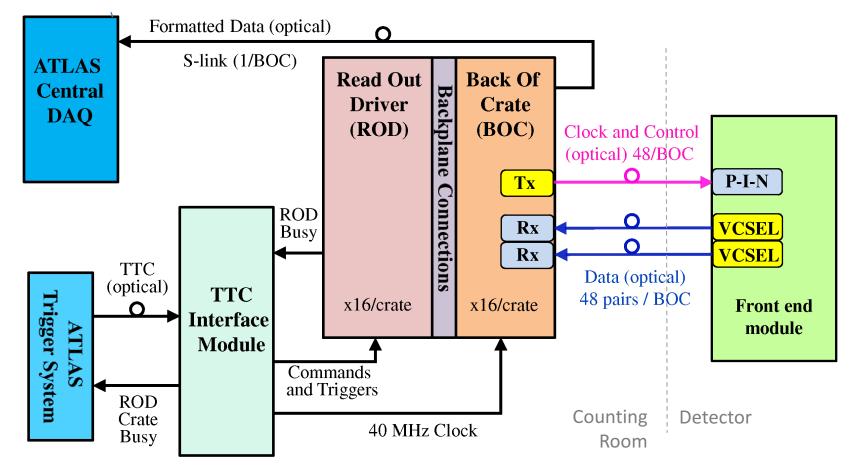

#### SCT DAQ and Optical Communication

D.Robinson Radiation Workshop 23-24 April 2018

D.Robinson Radiation Workshop 23-24 April 2018