A Large Ion Collider Experiment

# Radiation Hardness of Monolithic Active Pixel Sensors and Readout Electronics for the ALICE Inner Tracking System Upgrade

H. Hillemanns, CERN

ALICE | LHC Radiation Effects | April 23, 2018 | Hartmut HILLEMANNS, CERN

# OUTLINE

- 1. Introduction

- 2. Sensor Technology and Architecture

- 3. TID

- 4. NIEL

- 5. SEU

- 6. SEL

- 7. Readout Electronics

- 8. Future

- 9. Summary and Outlook

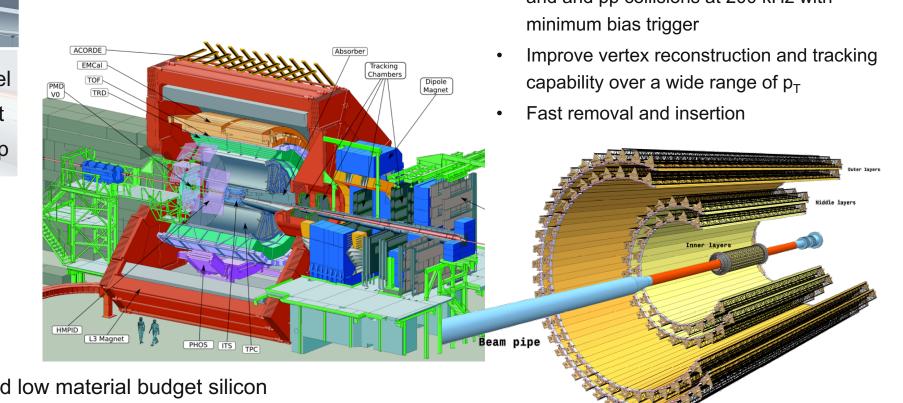

#### THE ALICE ITS UPGRADE PROPOSAL

Goal: precision studies of QGP in heavy ion collisions

2020

Objectives:

Read out of all Pb-Pb interactions at 50kHz and and pp collisions at 200 kHz with minimum bias trigger

Requires a very fast and low material budget silicon tracker detector with high granularity to be installed in

## **ITS UPGRADE DESIGN GOALS AND REQUIREMENTS**

#### **Design Objectives:**

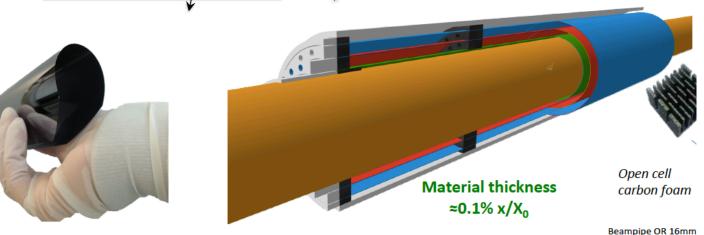

- Improvement of impact parameter resolution by a factor 3 in particular for very low p<sub>T</sub> through reduction of :

- Distance to IP (39mm -> 23mm)

- Material budget( $1.14\% \rightarrow 0.3\% X_0$ )

- Pixel size

- Improvement of standalone tracking efficiency and  $\ensuremath{p_{\text{T}}}$  resolution

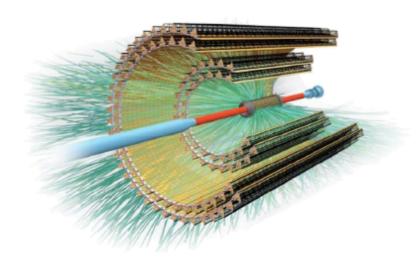

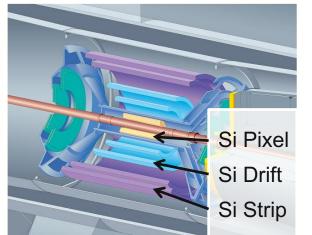

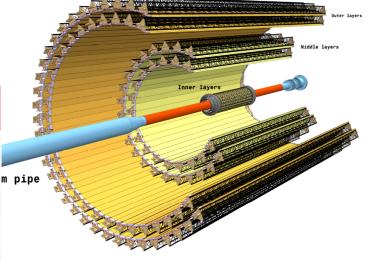

#### New ITS Layout

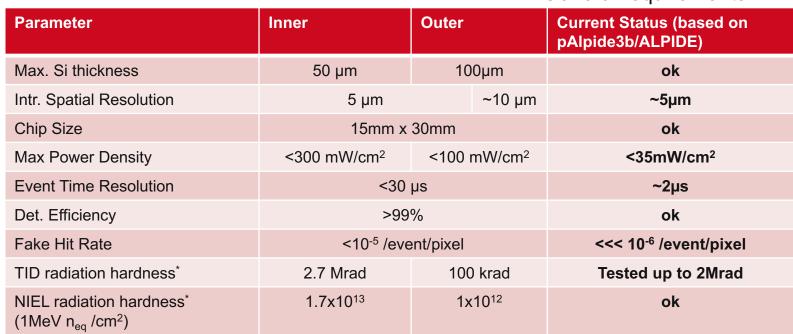

- 7 layers (3 inner, 4 outer layers)

- Radial coverage 23 406 mm

- 24120 Chips, 12.5 Giga Pixels

- 10.3m<sup>2</sup> Active Surface

\* Incl. a safety factor of 10

#### General requirements:

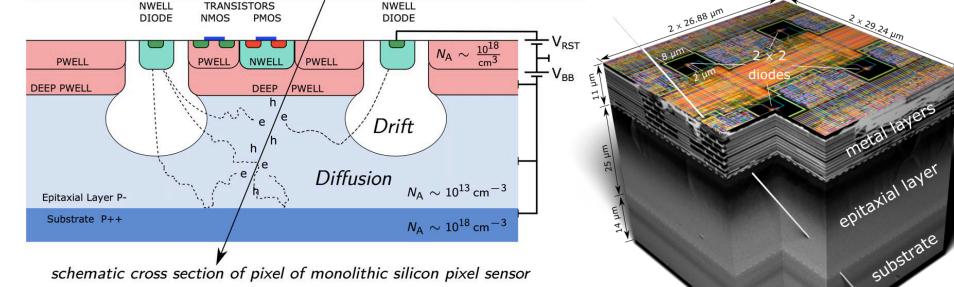

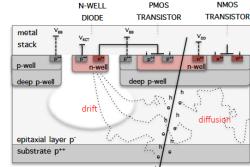

# **CMOS MONOLITHIC ACTIVE PIXEL SENSORS (MAPS)**

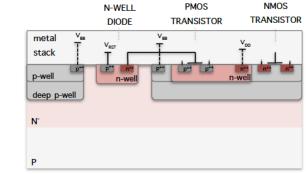

schematic cross section of pixel of monolithic silicon pixel sensor

#### Key features MAPS manufactured in TowerJazz 180nm CMOS Technology:

- Reduced sensitivity to TID due to thin (3nm) gate oxides •

- Quadruple well technology using deep p-well shielding: full CMOS circuits in the active sensor area

- High Resistivity epitaxial layer thickness of 25 µm (not fully depleted):

- Increased depletion volume around the collection diode by applying reverse substrate bias VBB

- Charge collection through drift (white) and diffusion (blue white) within 1ns and 100ns respectively

- Small n-well diode (2µm 3µm, significantly smaller than pixel), thus lower input capacitance resulting in an increased input voltage

Pixel

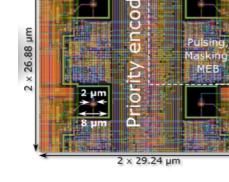

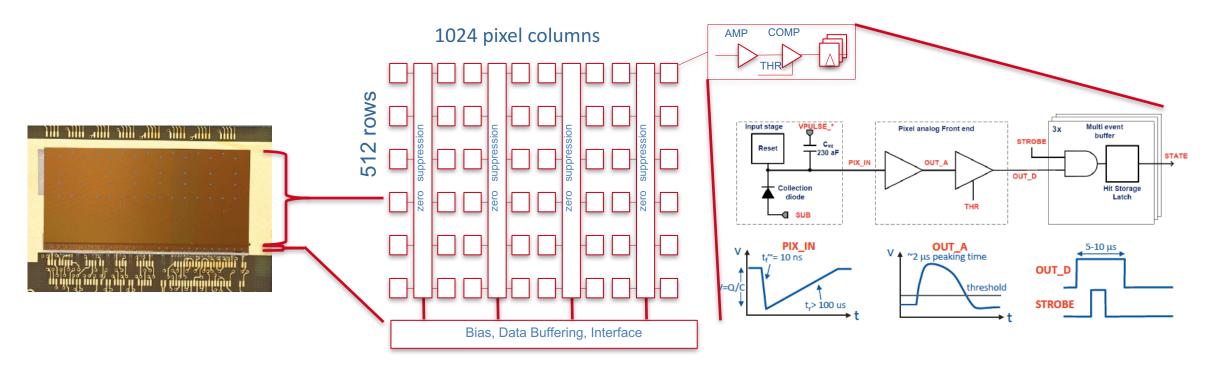

## **ALPIDE ARCHITECTURE**

#### **Key Concepts:**

- In-pixel amplification

- In-pixel discrimination

- In-pixel multi hit buffer

- In-matrix sparsification through priority encoding

#### Key Features:

- Dimensions: 30mm x 15mm

- Pixel pitch: 29µm x 27µm

- Low power consumption: < 35 mW/cm2

- Global shutter: continuous (integration time <10µs) or triggered (200kHz) data acquisition

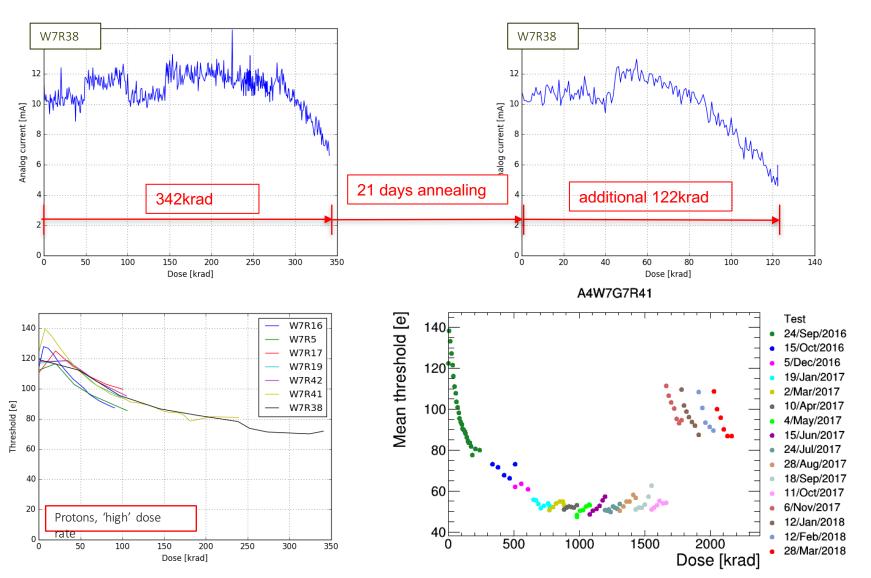

# **TID EFFECTS**

- TID irradiation using a cyclotron (NPI Rež/Prague, 30 MeV/c protons )\* and a Xray machine (CERN ATLAS team)

- Main observations during and after irradiation:

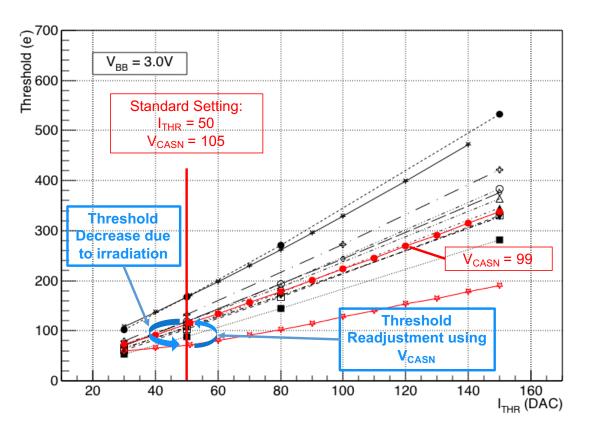

- Some chip characteristics (thresholds, analogue supply currents, current DAC settings) affected as a function of TID, but also of dose rate (>> 0.1 krad/h (@50kHz Pb-Pb expected)

- Changes in analogue supply current and current DAC settings anneal after a few days, effects thus presumably not visible for the maximum expected ALICE dose rate

- Annealing of threshold values slow, but compensation though appropriate DAC settings

\*CANAM infrastructure of the NPI CAS Rez supported through MŠMT project No. LM2011019

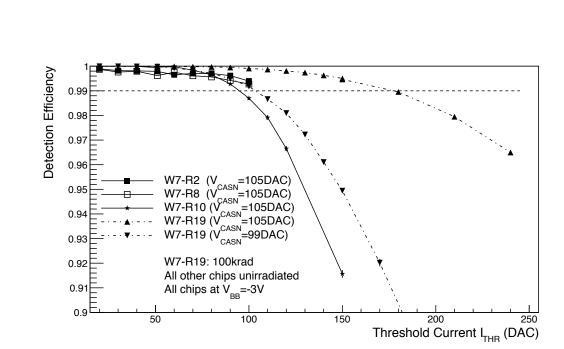

**TID EFFECTS**

Detector performance not affected after TID of 100krad (350krad see next slide)

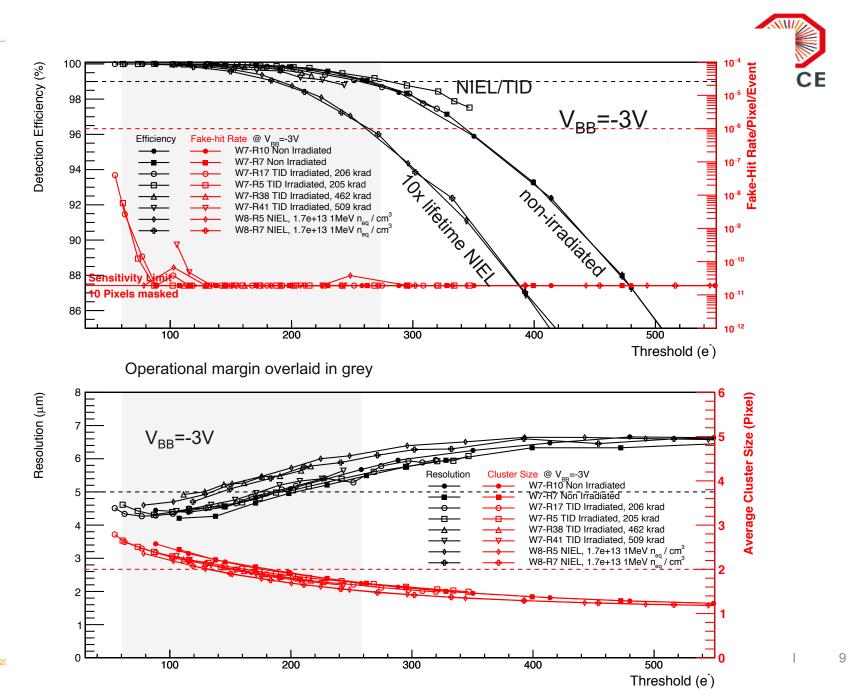

# **NIEL AND TID**

- N-irradiation with a fluency of 1.7\*10<sup>13</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup> at JSI (SL)\*

- Sensor characterisation in various test beams

- Excellent detector performance before and after irradiation over a wide range of operational settings

) AIDA

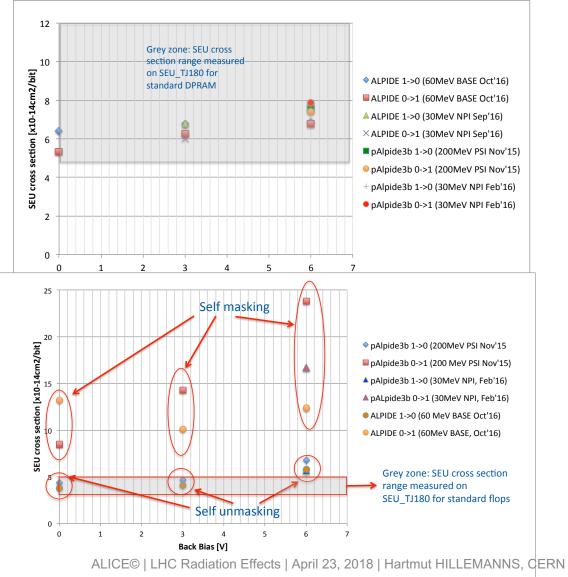

## SINGLE EVENT UPSET

- pAlpide3b/ALPIDE SEU tests using proton beams at NPI, Prague (CZ) (30MeV/c) and at PSI (20 – 200 MeV/c)

- SEU cross section measurement of non SEU protected structures:

- Region memories (FIFO)

- Pixel mask bits

- Typical SEU cross section values:

- Region Memory: 7e-14 cm<sup>2</sup>

- Pixel mask bit: 10e-14 cm<sup>2</sup>

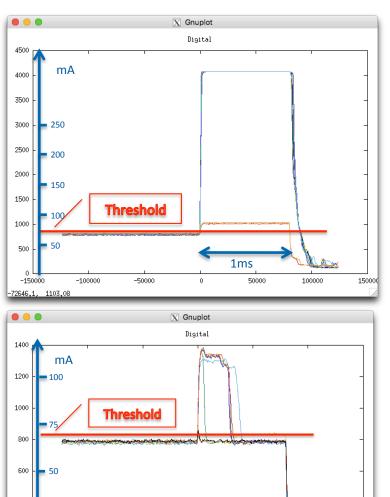

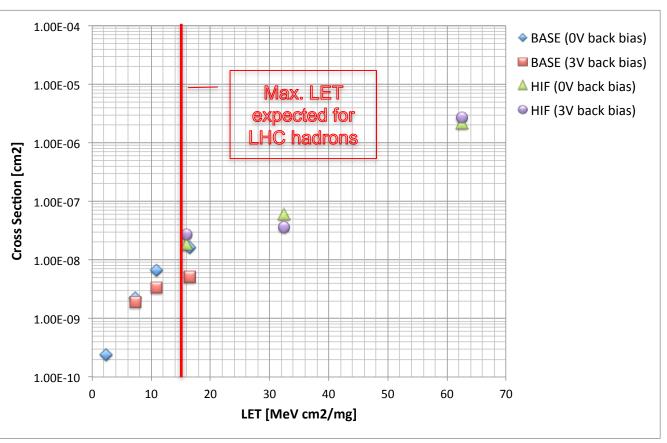

#### SINGLE EVENT LATCHUP TESTS (1/2)

#### SEL Tests at HIF (UC Louvain-la-Neuve) and BASE (LBL):

- Various ion cocktails covering a wide range of LET values (2.4 – 62.5 MeVcm<sup>2</sup>/mg)

- Test setup with dedicated SW for overcurrent detection

- Thresholds (4mA) for analog and digital supply currents

- Chip power cycling after 1ms after overcurrent detection

Û

1ms

50000

100000

150000

400

200

-150000

-26379.9, 1539.20

-100000

-50000

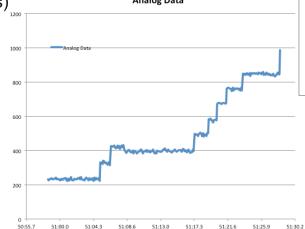

# SINGLE EVENT LATCHUP TESTS (2/2)

Main Observations:

- Measurements at HIF and BASE in reasonable agreement

- No analog overcurrents observed

- Measured cross sections convoluted with expected ALICE particle spectrum results in about 1 LU per day for L0 (23mm, 108 sensors) at a maximum hit density of 1MHz (courtesy R.Garcia, CERN EN)

- All sensors survived latchup tests (even after cumulative latchups)

Analog Data

BASE results courtesy of L. Greiner, J.Szornel A.Collu, G.Contin (LBL Berkeley)

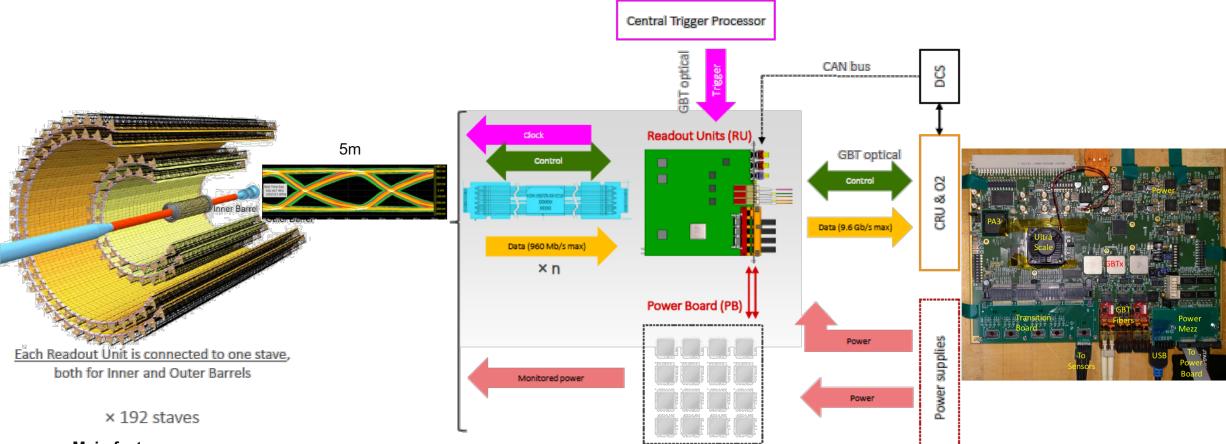

#### **READOUT ELECTRONICS RADIATION TOLERANCE VALIDATION (1/3)**

#### Main features:

- One readout unit per stave (5m, 1.2/0.4 Gb/s data, 80Mb/s control, clock and power control), optically connected to common readout unit (CRU) and central trigger processor (CTP)

- CTP feeds trigger and checks CRU status

- CRU reads data and broadcasts control commands

- Data acquisition, packaging and detector control by O<sup>2</sup> system

- DCS access through O2 or CANBus

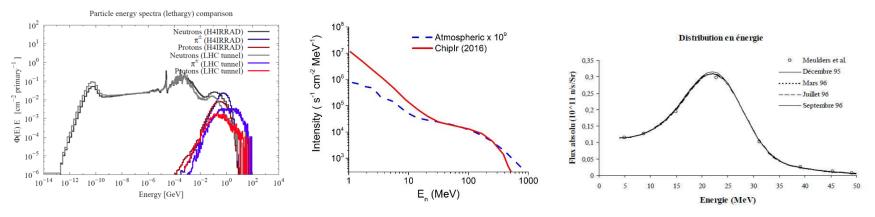

## **READOUT ELECTRONICS RADIATION TOLERANCE VALIDATION (2/3)**

#### **Radiation Environment**

- Readout Electronics located in "Mini Frames" at about 1m from the beam axis and 3m from the IP

- Radiation levels (incl. safety factor 10):

- TID: 10 krad

- NIEL: 1.6 10<sup>11</sup> 1MeV n/cm2

- HEH Flux: 1 kHz/cm<sup>2</sup>

- Requires SEE tolerant hardware and firmware

# Extensive radiation test program both at component and system level:

- Firmware scrubbing verification using 30 MeV protons

- Full system test in the CHARM mixed radiation field

- DCDC (LMZ31710) verification using 23 MeV neutrons (UCL LIF)

- Full system tests using the ChipIr neutron facility (RAL)

- Power Board TID testing using the GIF++

## **READOUT ELECTRONICS RADIATION TOLERANCE VALIDATION (3/3)**

#### Main Results:

- Everything works as expected

- Readout System fully TID tolerant

- SEL not an issue

- Scrubbing from auxiliary FPGA working and effective

- Data interruption in case of firmware upset has been measured and lasts on average one second for a the specific lane, few seconds if a reset of the FPGA is necessary

- Errors on clock resources or other key subsystem are negligible (too rare to gather any significant statistics).

- Commercial DCDC proved compliant with the task, one power glitch every 72 hours foreseen within the whole ITS.

| Failure mode                   | Affected section                   | Estimated occurrence in ITS operations (average MTBF) |            |            | Corrective action                                   | Downtime per<br>occurrence |

|--------------------------------|------------------------------------|-------------------------------------------------------|------------|------------|-----------------------------------------------------|----------------------------|

|                                |                                    | IB                                                    | OB         | Whole ITS  |                                                     |                            |

| Sensor data lane               | 1 sensor for IB<br>½ module for OB | 22 - 40 h                                             | 4 - 6 h    | 3 - 5 h    | Self-repairing                                      | < 1 s >                    |

| GBT data*                      | 1 full stave                       | 29 h                                                  | 10 h       | 7 h        | 30% self repairing, 70% reset<br>by slow control    | < 5 s >                    |

| Clock resources                | 1 full stave                       | Negligible                                            | Negligible | Negligible | Reset by slow control                               | < 5 s >                    |

| Transceiver settings           | 1 sensor, IB only                  | > 932 h                                               | -          | _          | Reset by slow control                               | < 5 s>                     |

| Flash memory                   | 1 full stave                       | Negligible                                            | Negligible | Negligible | FLASH reprogramming (30 s<br>beam off, 30m beam on) | 30 s – 30 m                |

| <b>1</b> PA3                   | 1 full stave                       | 172 h                                                 | 58 h       | 43 h       | Reset by slow control                               | < 0 s>                     |

| <sup>2</sup> DCDC power glitch | 1 full stave                       | 294 h                                                 | 98 h       | 71 h       | Power cycle                                         | < 10 s >                   |

<u>Data for the non-TMR block</u>, final version will use TMR protected block. This failure mode also include sensor control and clock failures.

<sup>1</sup>When PA3 get stuck the main FPGA is not compromised, and therefore no downtime occurs. TMR of key block in PA3 firmware will further improve that.

<sup>2</sup>Considering 200 RU with 8 DCDC each (20% overestimation)

# **DEVELOPMENTS FOR THE FUTURE**

#### What's next?

- The use of MAPS in various detector concepts for future experiments requires the improvement of radiation tolerance and reduction of material budget

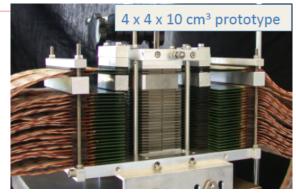

- High granular digital calorimetry:

- Multilayer Si-W pixel and pad readout

- Extremely compact, small Molière radius

- Very good linearity and energy resolution

- Modified CMOS process:

- No circuit design change necessary

- Full depletion through planar n<sup>-</sup> -p junction

- Use of ELT nmos transistors

- Ultrathin sensors:

- Large sensors using stitching technology

- Chip thickness <50µm

- Cooling through air flow

#### SUMMARY AND OUTLOOK

- The upgrade of the ALICE ITS requires a new, fast, low material budget and radiation hard Si tracker

- Based on its features, the TowerJazz 180nm CMOS technology has been chosen as baseline technology for ITS

- Excellent detector performance in terms detection efficiency and fake hit rate after a TID of 350krad and a NIEL irradiation of 1.7x10<sup>13</sup> 1 MeV n<sub>ed</sub>/cm<sup>2</sup> s

- Measured cross sections for SEU and SEL are not considered to be a risk for the operational stability of the ITS

- TID effects will be monitored on a longer time scale for various irradiation scenarios

- Radiation tests on full modules with readout units working stable as expected

- Ongoing future development to address radiation hardness and ultrathin sensors as well as the use of MAPS in calorimeters