### **Characterization of the MPA prototype**, a 65 nm pixel readout ASIC with on-chip quick transverse momentum discrimination capabilities.

Alessandro Caratelli **Davide Ceresa** Jan Kaplon Kostas Kloukinas Jan Murdzek Simone Scarfi Jarne Theo De Clercq Mykyta Haranko Dena Giovinazzo

TWEPP 2018 Topical Workshop on Electronics for Particle Physics 18<sup>th</sup> September 2018

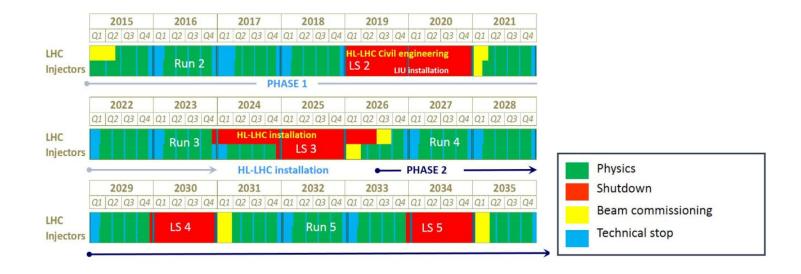

# High Luminosity LHC

#### 10x the nominal luminosity

up to 200 collision every 25 ns.

# Major upgrades to the LHC experiments are necessary

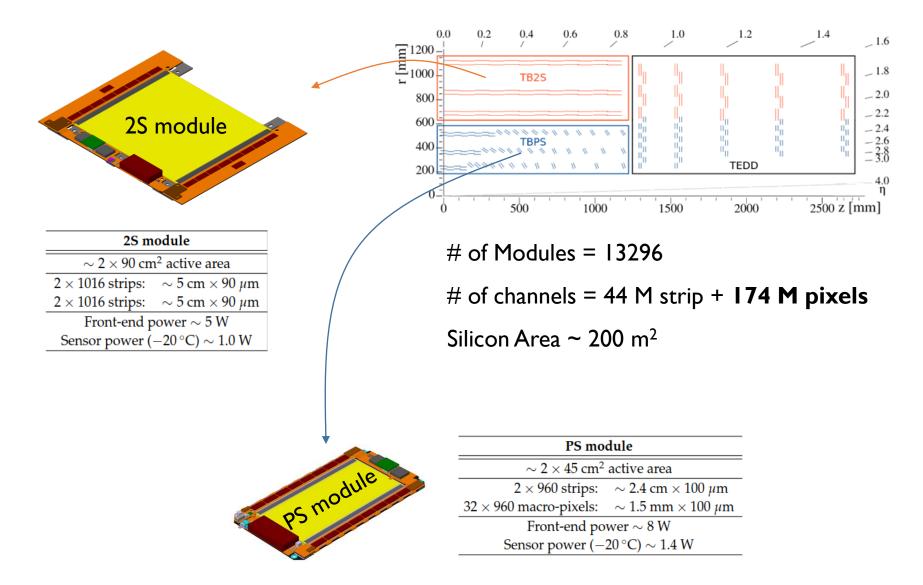

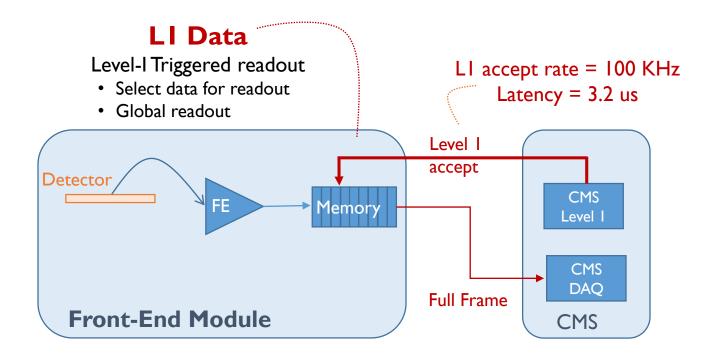

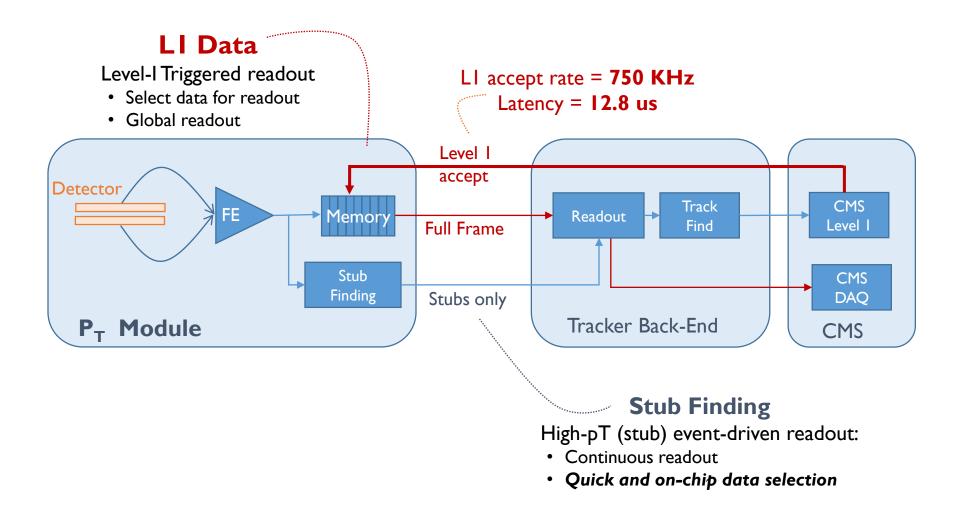

# CMS Outer Tracker upgrade

#### 200 pile-up event

40 MHz Bunch Crossing rate

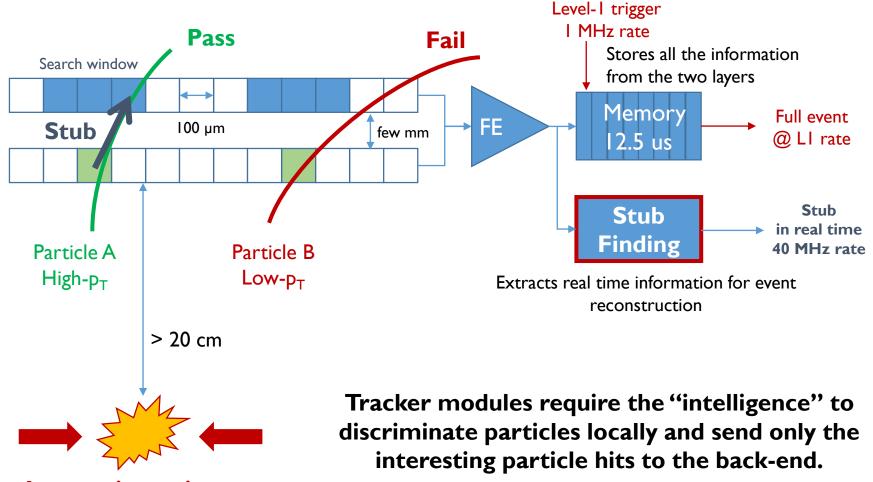

#### Phase-II upgrade of CMS Outer Tracker requirements:

- Increase granularity

- Increase radiation tolerance

3

- Participate in the L1 trigger

- Improve trigger performance

- Reduction of material budget

#### Tracker module requirements:

- Introduction of a pixelated sensor

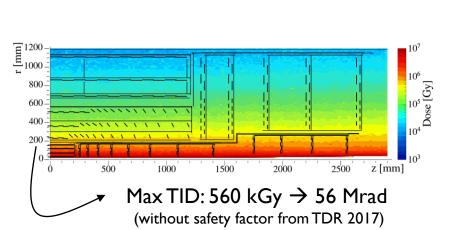

- Radiation tolerance up to 100 Mrad

- Quick and on-chip particle discrimination

- Higher trigger rate and longer latency

- Power density < 100 mW/cm<sup>2</sup>

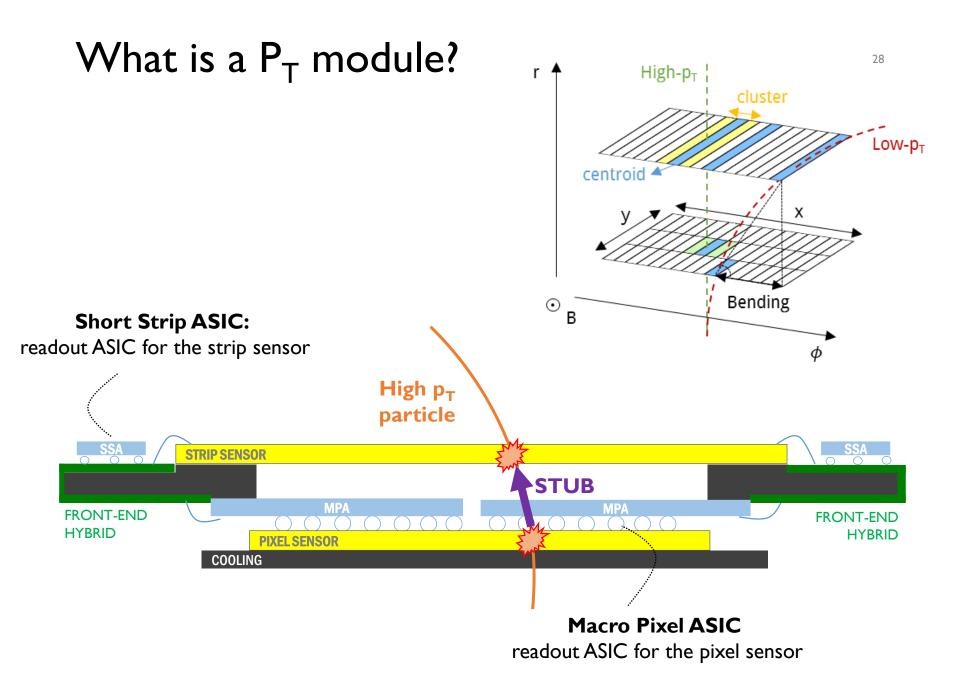

## CMS Outer Tracker p<sub>T</sub> module concept

4

Interaction point

### CMS Outer Tracker layout

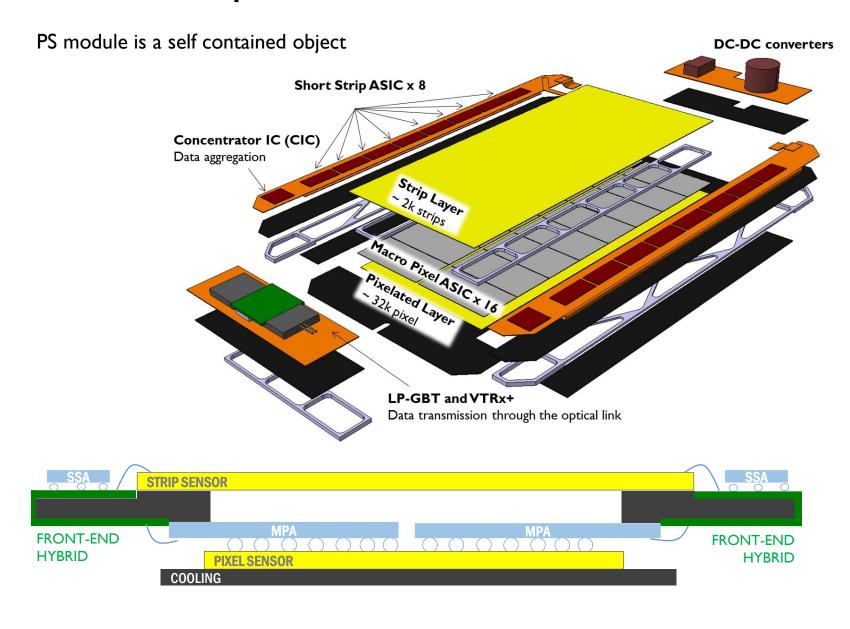

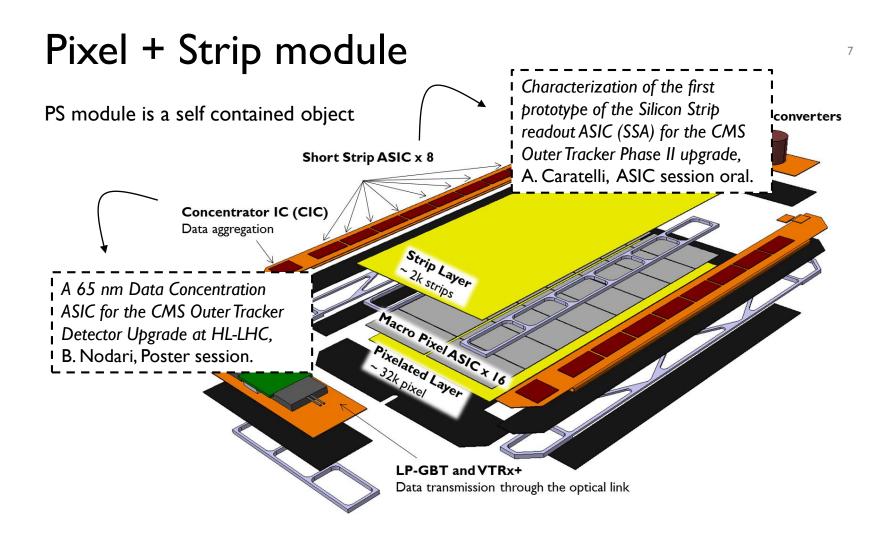

### Pixel + Strip module

#### Module level verification SSA – MPA - CIC:

A System-Verilog Verification Environment for the CIC Data Concentrator ASIC of the CMS Outer Tracker Phase II Upgrades, S. Scarfi, Poster session.

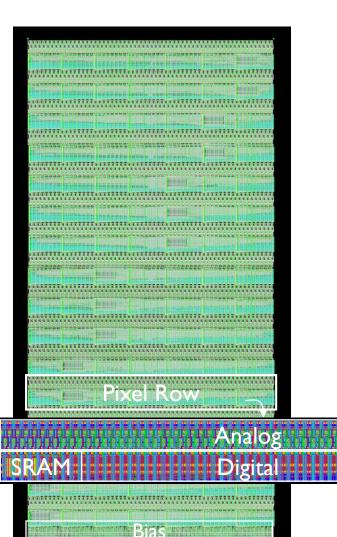

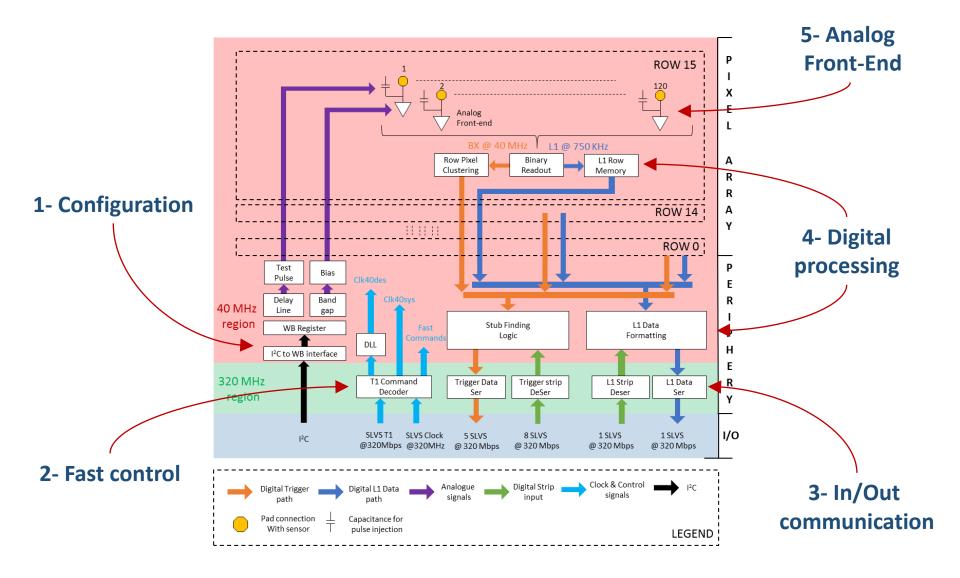

## Macro Pixel ASIC implementation

Pac

IC Technology: 65 nm CMOS technology

#### Implementation technique:

Digital-on-Top architecture Triplicated Control logic (TMR) Clock-Gated configuration Multi voltage supply design Multi-VT design Trunk-based clock distribution Hierarchical design

- Тор

- Analog Bias Block

- Row (x16)

- Digital Pixel Electronics

- Analog Front-End

- SRAM

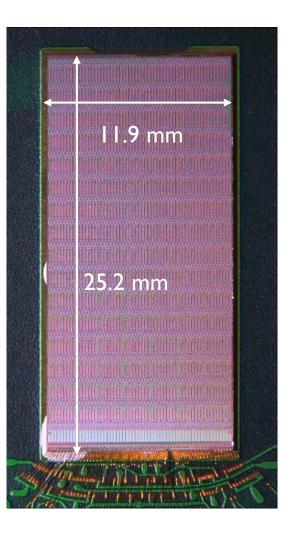

### Macro Pixel ASIC

| Pixel Arrangement              | 118 x 16 = 1888 pixels                                                                                |

|--------------------------------|-------------------------------------------------------------------------------------------------------|

| Macro Pixel Size               | 100 um x 1446 um                                                                                      |

| Sensor Area                    | 5 cm x 10 cm (16 x MPA)                                                                               |

| Acquisition Type               | Continuous @ BX rate (40 MHz)                                                                         |

| Hit Rate (Pixel hit Occupancy) | 53 MHz / cm^2                                                                                         |

| Readout types                  | <ol> <li>Triggered for full frame (L1-Trigger)</li> <li>Continuous for high-pT information</li> </ol> |

| Acquisition Mode               | Binary readout                                                                                        |

| L1-Trigger latency             | < 12.8 us                                                                                             |

| LI-Trigger rate                | <750 kHz                                                                                              |

| Input data types               | <ol> <li>Raw strip data</li> <li>Strip clusters</li> </ol>                                            |

| Output data types              | <ol> <li>Pixel and strip clusters</li> <li>Stubs</li> </ol>                                           |

| Trigger data storage           | Pixel frame for L1 Latency (~2048b x 512w)                                                            |

| Input data port                | 9 x Custom-sLVS @ 320 Mbps = 2.88 Gbps                                                                |

| Output data port               | 6 x Custom-sLVS @ 320 Mbps = 1.92 Gbps                                                                |

| Power budget                   | < 90 mW/cm <sup>2</sup>                                                                               |

| Radiation Tolerance            | 56 Mrad (No safety factor)                                                                            |

| Technology                     | 65 nm with 1p7m (4x1z1u + RDL)                                                                        |

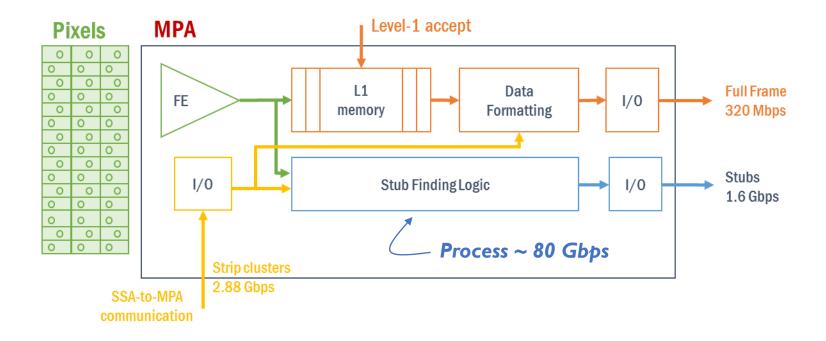

### MPA functionalities in a nutshell

Simulated MPA power consumption : < 200 mW  $< 100 \text{ mW/cm}^{2}$

High- $p_{\tau}$  particles @ BX rate Full frame @ L1 trigger **40 MHz with very low latency:** ~ 500 ns

I MHz rate

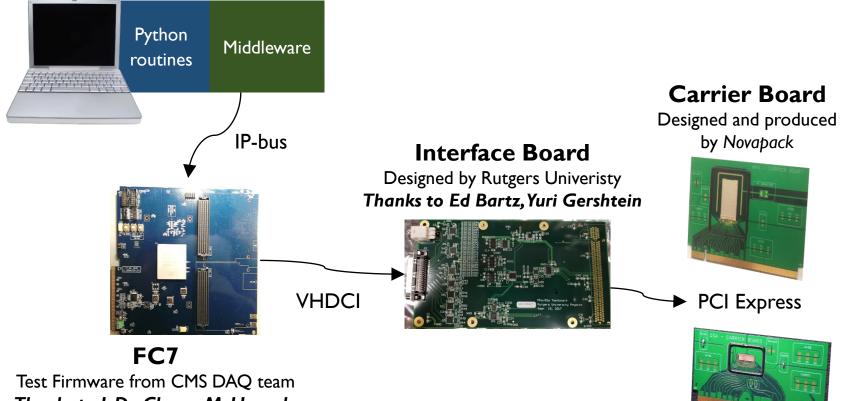

# MPA/SSA test system @ CERN

First full-size prototypes incorporating all functionalities required for system operation were submitted in Sept. 2017

Prototype tests started in February 2018 at CERN using bare dies.

Thanks to J. De Clercq, M. Haranko

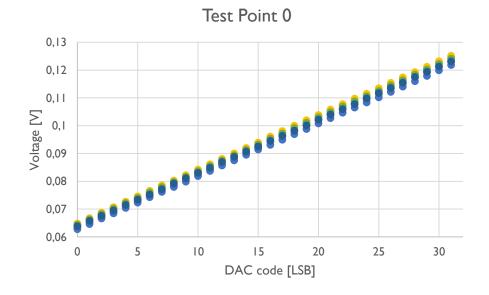

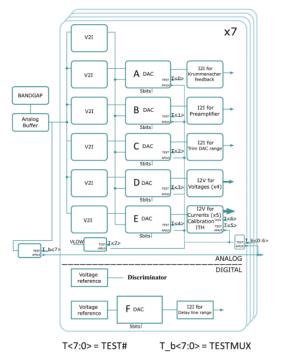

# **Bias Circuitry**

Reminder:

- 7x bias block

- 5x DAC (with test point) for calibration

Automatic procedure:

- Measure test point

- Modify DAC to match nominal values

- Measure and validate calibration

MPA User Manual V 0.1

**X**

Figure 6 Bias Structure

| TEST#<br>BIT | DAC<br>PVT adj. | Description                               | Expected Value   |  |  |  |  |  |

|--------------|-----------------|-------------------------------------------|------------------|--|--|--|--|--|

| 0            | Α               | Krummenacher feedback bias (80nA) : 0F    | 82mV             |  |  |  |  |  |

| 1            | В               | Preamplifier bias (15uA) : 0F             | 82mV             |  |  |  |  |  |

| 2            | С               | TRIM DAC range 65mV/153mV/250mV: 00/0F/1F | 48mV/108mV/172mV |  |  |  |  |  |

| 3            | D               | DAC for voltage biases: 0F                | 82mV             |  |  |  |  |  |

| 4            | E               | DAC for current biases: 0F                | 82mV             |  |  |  |  |  |

| 5            | E               | ITH (threshold) -10mV to +370mV: 00-FF    | 0 to 380mV       |  |  |  |  |  |

| 6            | E               | CALIBRATION level (0 to FF)               | 0 to 450mV       |  |  |  |  |  |

| 7            | /               | Local reference (GND)                     | 0 +/-5mV         |  |  |  |  |  |

Table 2 Summary of bias DACs and test points (measured through Test Analog)

15 | P a g e

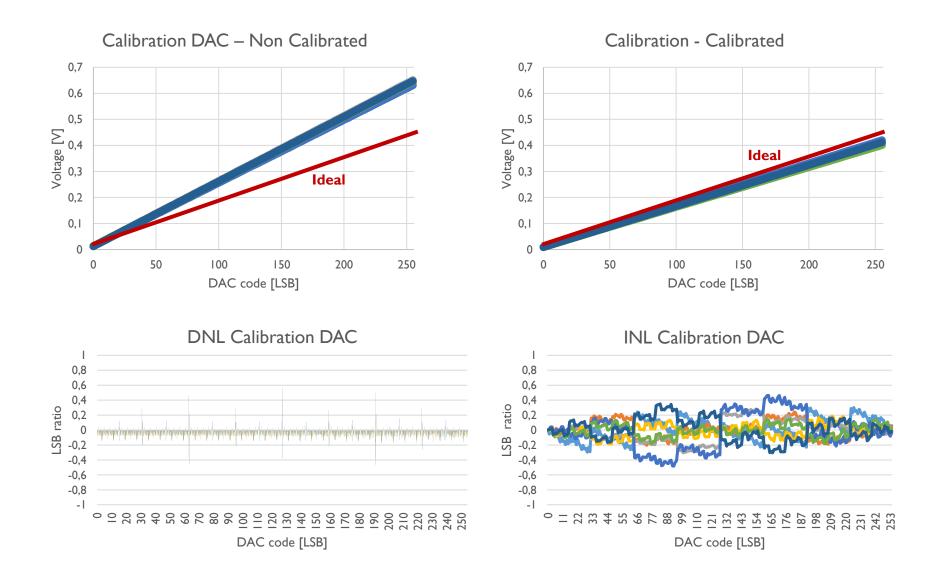

### Calibration & Threshold DAC

13

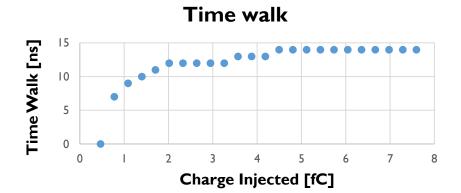

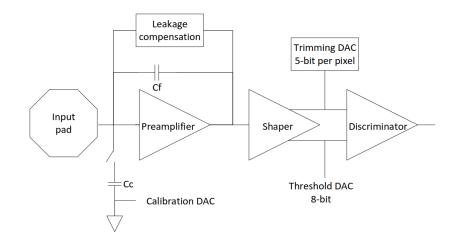

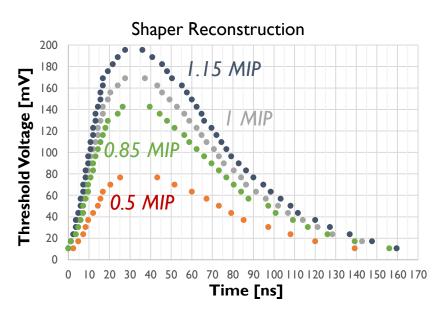

# Analog Front-End results MPA

Front-End designed by J. Kaplon. Simulation results:

- ENC < 200 e-

- Peaking time ~ 25 ns

- SNR >> 20

- Time walk < 15 ns

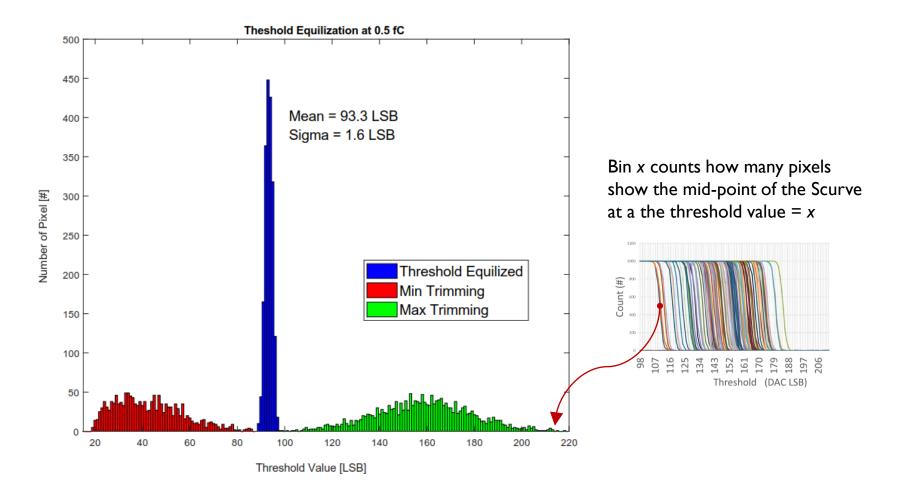

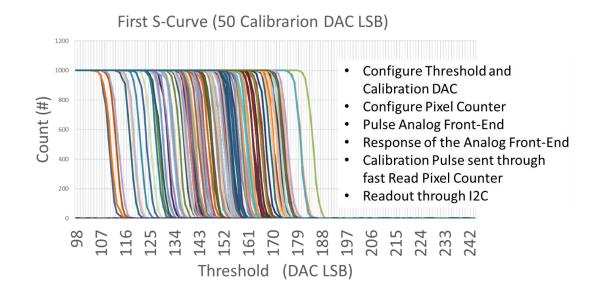

### MPA Threshold Equalization test

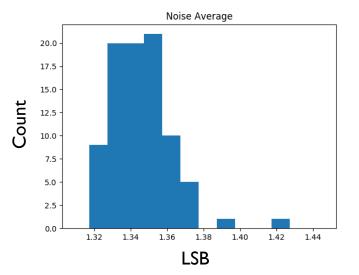

#### **S-Curve Trimming Spread @ 0.5 fC:** ±1.6 Threshold DAC LSB ± 0.55 Trimming DAC LSB ~ 150 electrons

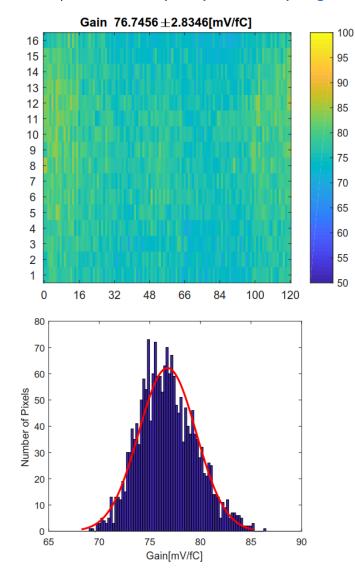

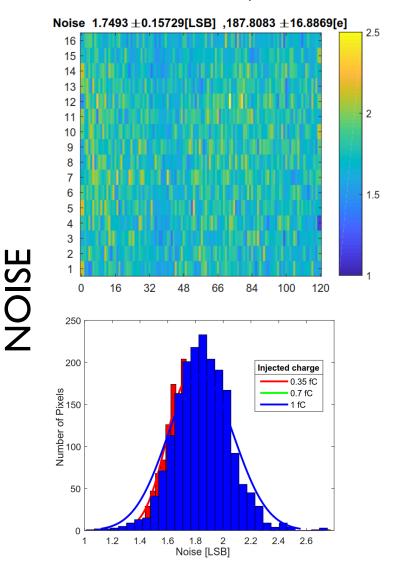

### MPA Gain and Noise results

Measurements provide a good agreement with simulation and reduced-size prototype called MPA-Light (reference: <u>http://iopscience.iop.org/article/10.1088/1748-0221/11/01/C01054</u>)

GAIN

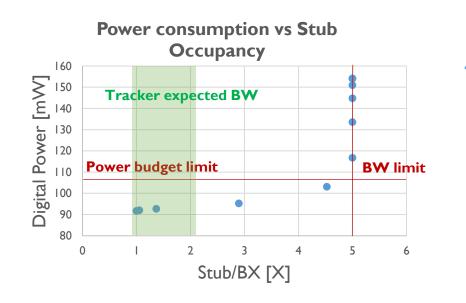

### Power consumption measurement

#### **Operative conditions:**

Nominal Voltage

No input data

Analog FE calibrated

SLVS max. current

Analog power @ 1.25V = 67 mW

Digital power @ 1.0V = 91 mW

Measured power consumption

IO power @ 1.25 V = 26 mW

Total power consumption: 184 mW Power budget < 200 mW What happens with occupancy?

### Simulation analysis power

Analog power @ 1.25 V = 70 mW

Digital power @ 1.0V = 88 mW

IO power @ 1.25 V = 27 mW

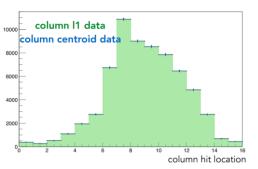

### First test beam by D. Schell and J. Clercq

- 2 test beams: ٠ CERN (first time running chip, fw, sw testing, first physics results) DESY (testing different sensor layouts)

- Chip was operated in all three read-out modes: asynchronous, synchronous (edge sensitive) and synchronous (level sensitive)

- Single sensor —> no stub data yet. Chip operated in pixel-pixel mode —> get centroid data on the stub lines

8000

7000 6000

1000

# row I1 data row centroid data row hit location

Beam Profile 30°:

18

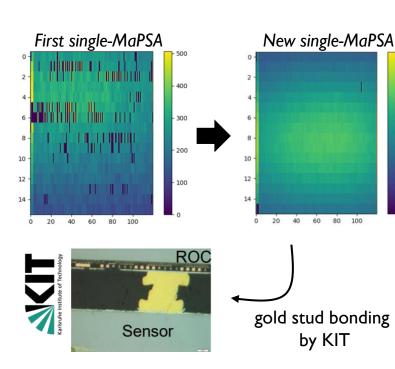

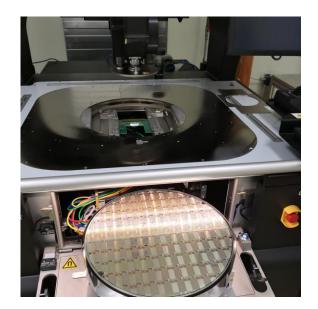

# Wafer probing results

4 Wafer tested (with and without bumps)

- Fully automatized procedure (python)

- 3.5 mins/chip for complete characterization

#### Run example:

88 chips tested (one chip does not power up).

Performance of the 87 remaining chips analysed:

- Control: all chips passed basic checks (I2C, output alignment, bias calibration).

- Analog: all chips show working fast readout;

- Three chips show bad pixels (yield ~ 95%).

- Digital: Trigger and L1 path tested (SRAM at 1.2V):

- 71 good chips (yield ~ 81%);

- Loss related with memory issue.

#### Final Yield **69 good chips** (yield ~ 78%) Expected yield from foundry model ~ 65%

Thanks to J. Alozy, M. Osherson, A. Apresyan and D. Giovinazzo.

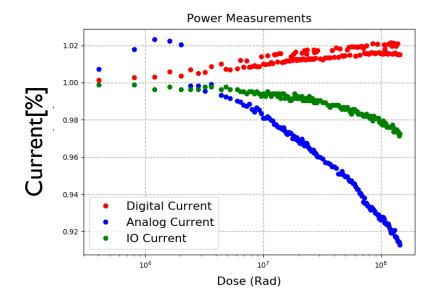

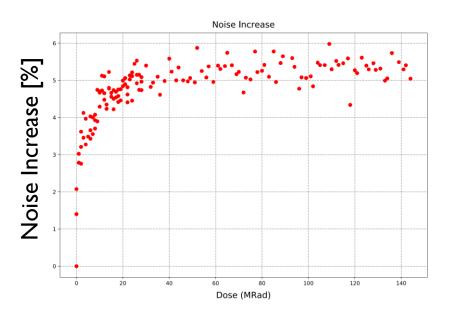

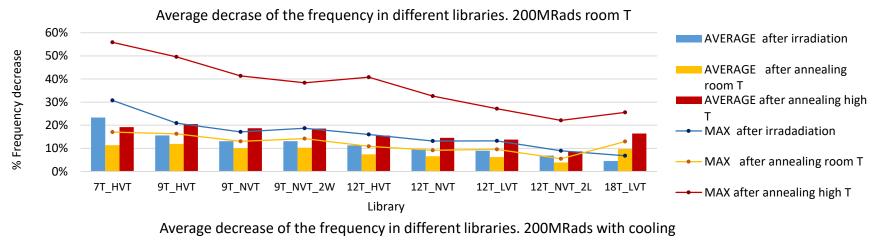

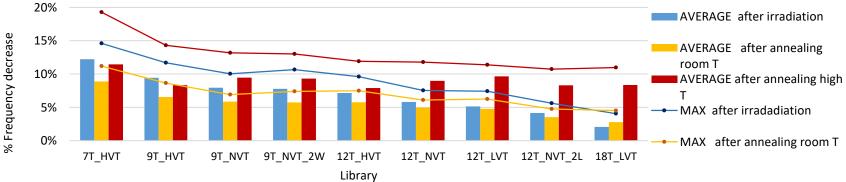

# MPA results with TID

Irradiation performed using the new CERN X-Ray facility (~1.5 Mrad/h on ~3  $cm^2$ ).

Room temperature

3 runs 100, 150, 200 Mrad

Digital functionalities were not degraded

Analog degradation was within expectation <10 %

Thanks to G. Borghello and

H. Koch

20

# Conclusions

- First full-size and full-functionality MPA prototype was fabricated in 65 nm CMOS technology

- Functional verification and performance characterization test results are very promising

- High quality Test beam results produced using MPA-sensor assemblies

- First TID test on the MPA confirms radiation harness up to 200 Mrad

- These prototypes enable the development of the first PS module assemblies

## Thanks to...

#### MPA-SSA design team at CERN:

Alessandro Caratelli, Davide Ceresa, Jan Kaplon, Kostas Kloukinas, Jan Murdzek and Simone Scarfi'

#### to our collaborators for design:

CERN: Stefano Michelis for the bandgap design

University of Bergamo and INFN Pavia: Francesco De Canio and Gianluca Traversi for the sLVS TX and RX design

SMU: Gong Datao, Yang Dongxu and Jian Wang for the DLL design

RAL: Stephen Thomas for the Analog buffer design

#### to our collaborators for testing :

M. Osherson(Fermilab), B. Harrop (Princeton), E. Bartz (Rutgers), A. Apresyan (Fermilab), S. Los (Fermilab), Y. Gershtein (Rutgers), J. Alozy (CERN).

# Reference

- D Abbaneo and A Marchioro, A hybrid module architecture for a prompt momentum discriminating tracker at HL-LHC, Journal of Instrumentation, Volume 7, September 2012

- D. Ceresa et Al., Macro Pixel ASIC (MPA): the readout ASIC for the pixel-strip (PS) module of the CMS outer tracker at HL-LHC, Journal of Instrumentation, Volume 9, November 2014

- D. Ceresa et Al., Readout architecture for the Pixel-Strip (PS) module of the CMS Outer Tracker Phase-2 upgrade, PoS(Vertex 2016)066.

- L. M. Casas et al., Characterization of radiation effects in 65 nm digital circuits with the DRAD Digital radiation test chip, 2017 JINST 12 C02039

- A. Caratelli et Al., Short-Strip ASIC (SSA): A 65nm Silicon-Strip Readout ASIC for the Pixel-Strip (PS) Module of the CMS Outer Tracker Detector Upgrade at HL-LHC, PoS(TWEPP-17)031.

- D. Ceresa et Al., Design and simulation of a 65 nm Macro-Pixel Readout ASIC (MPA) for the Pixel-Strip (PS) Module of the CMS Outer Tracker Detector at the HL-LHC, PoS(TVVEPP-17)032.

- S.Viret, Data transmission efficiency of the phase II tracker front-end system for the tilted geometry, CMS internal note.

## Reference

- G. Blanchot et al., Hybrid circuit prototypes for the CMS Tracker upgrade front-end electronics, 2013, JINST 8 C12033

- P. Fischer, G. Comes and H. Kruger, *MEPHISTO: A 128-channel front end chip with real time data sparsification and multi-hit capability*, 1999 Nucl. Instrum. Meth. A 431 134.

- L. Gaioni et al., Low-power clock distribution circuits for the MPA, 2015 JINST 10 C01051

- F. Faccio et Al., Radiation-induced short channel (RISCE) and narrow channel (RINCE) effects in 65 and 130 nm MOSFETs, IEEE Trans. Nucl. Sci., vol. 62, no. 6, pp. 2933-2940, Dec. 2015.

- R. Brouns et Al, Development of a radiation tolerant low power SRAM compiler, AMICSA 2014

- D. Ceresa et Al., A 65 nm pixel readout ASIC with quick transverse momentum discrimination capabilities for the CMS Tracker at HL-LHC (MPA-Light), Journal of Instrumentation, Volume 11, January 2016

- V. Re et al., Review of radiation effects leading to noise performance degradation in 100 nm scale microelectronic technologies, Proc. IEEE Nuclear Science Symp. Conf. Rec., 2008.

- The Phase-2 Upgrade of the CMS Tracker, 2017 [cds.cern.ch/record/2272264]

Davide.Ceresa@cern.ch

# Spare slides

### Current Silicon Strip Tracker

### Outer Tracker principle of operation

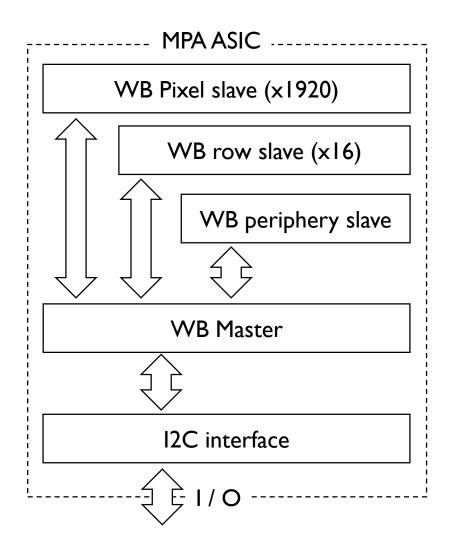

# Slow Control

MPA and SSA uses an I2C protocol for external interfacing and an Wish Bone protocol for internal configuration

MPA 10 bit x 1920 pixels + periphery = 13 mW (15% of digital power budget)

The I2C interface is activated only when a I2C command is received and **only the addressed WB slave is activated**.

# Configuration power consumption < 1 mW

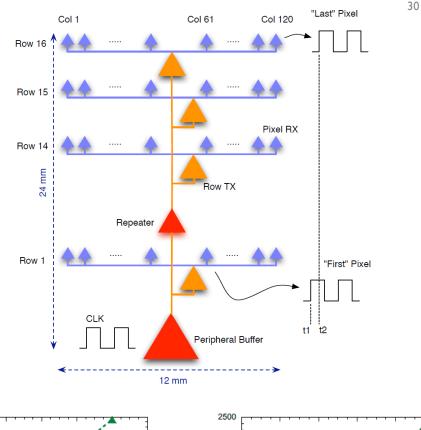

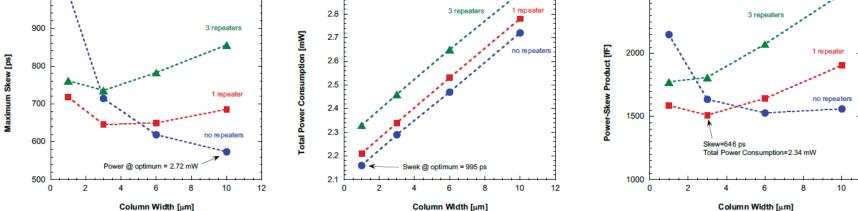

# **Clock distribution**

#### **Clock distribution design:**

A clock distribution with one column saves a factor  $\sim 10$  in power consumption. Simulation shows that the skew can be kept below 1 ns which is enough for the application.

#### **Open Issue:**

1000

How to implement in digital-on-top design? The clock tree in the pixel array should follow the dimension and the structure defined by the study.

2.9

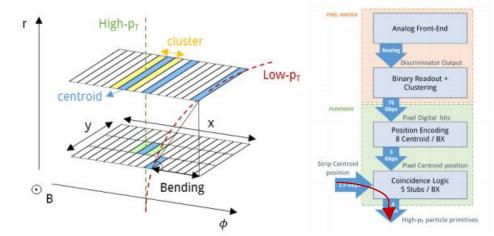

## Strip Centroid identification logic

#### Firmware

<u>SSA emulator on FC7</u> allows to send single/multi programmable strip centroid

Study single/multi cycle line alignment and processing

#### ASIC

Strip-Strip mode: the MPA sends in output the strip centroids.

Check SSA data and I/O data bus (8 x 320 MHz input, 5 x 320 MHz output)

Figure 8 Stub Finding in PS-module scheme (left) and block diagram (right)

Define Strip Centroid and line in firmware: 64

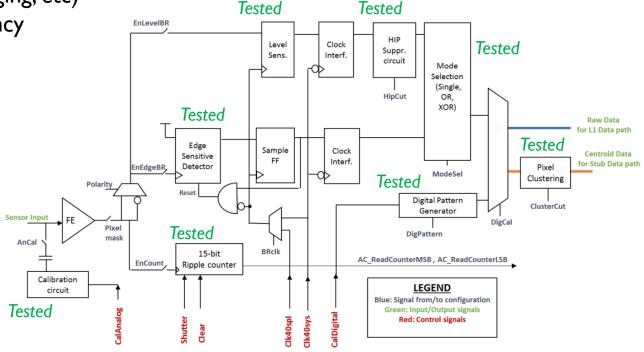

# Pixel Centroid identification Logic

## **Tested**

#### ASIC

Pixel-Pixel Mode: the MPA sends out Pixel Centroid

- Configure **Digital Calibration** Input

- Send Pulse

- Observe Output Stub (Clustering, Encoding, BX Averaging, etc)

- Observe Data Latency

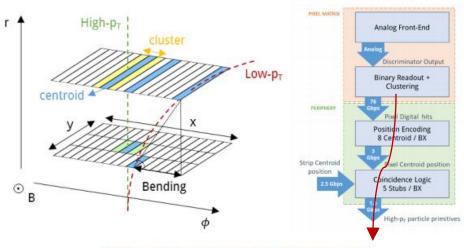

Figure 8 Stub Finding in PS-module scheme (left) and block diagram (right)

Pulse injection in: 17, 18, 19, 20, 25, 26 Stub Position BX 1: 0, 0, 0, 0, 0 BX 2: 0, 0, 0, 0, 0 ... BX 21: 34, 38, 51, 0, 0

# Stub Processing Logic

#### Firmware

<u>SSA emulator on FC7</u> allows to send single/multi programmable strip centroid

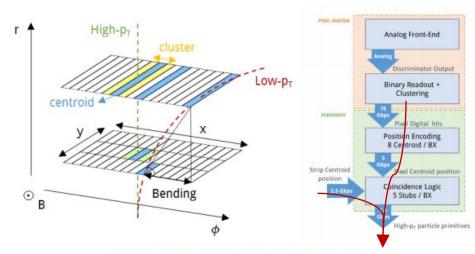

# Test of coincidence logic and stub < generation

#### ASIC

Tracker (Normal) Mode: the MPA sends out stubs

- Configure Digital Calibration Input

- Send Pulse

Figure 8 Stub Finding in PS-module scheme (left) and block diagram (right)

Pulse injection in: 17, 18, 19, 20, 25, 26

Stub Position BX 1: 0,0,0,0,0 BX 2: 0,0,0,0,0

BX 21: 34, 38, 51,0,0

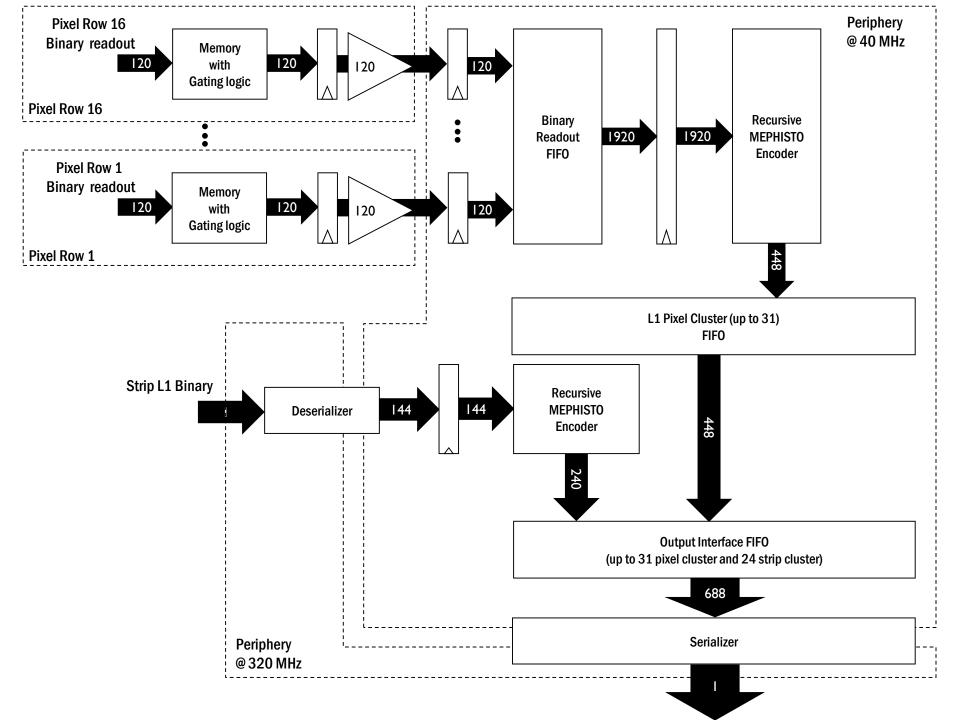

## **Binary Readout Logic**

- Configure Pixel-Pixel Mode

- Configure Analog Calibration Input

- Send Pulse

- Observe Output Stub (Sampling, HIP suppression, Clustering, Encoding, BX Averaging, etc)

Tested Tested

- Observe Data Latency

34

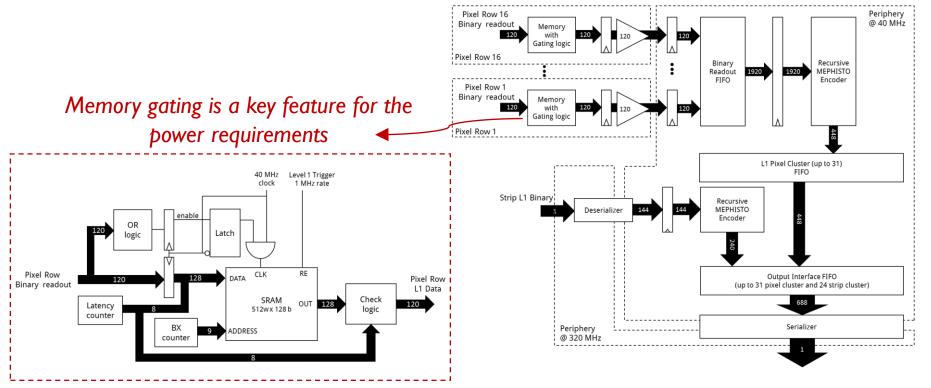

# LI Data with memory gating

#### Output Frame to data concentrator for LI data:

- Triggered transmission

- Unique start sequence (19 bits)

- Variable packet size depending on event size (max. 32 Pixel/Strip clusters)

- Initial training with fixed or pseudo-random sequence capabilities (phase Aligner on receiver side)

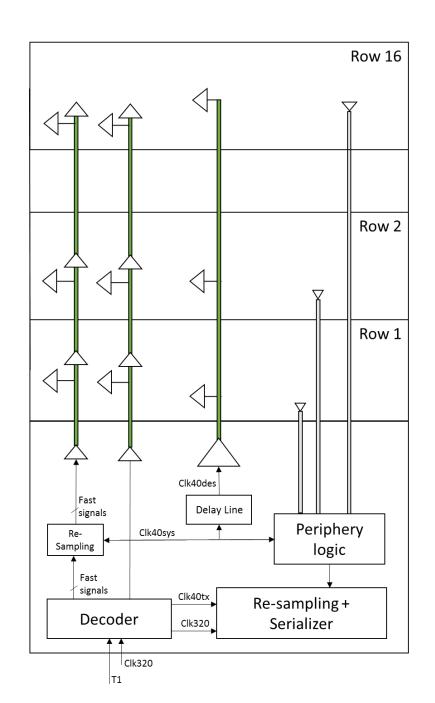

# **Clock distribution**

#### Clk40Des:

- 40 MHz clock for FE sampling

- Distributed with Clock Trunk approach

- Clock domain crossing to clk40sys in pixel core

- $\Delta t$  respect clk40sys = 0-3.125 ns

#### Clk40sys

- 40 MHz system clock

- Distributed with re-buffering at each row

- Skewed to limit Voltage drop

- Triplicated

- Clock domain crossing to clk40tx before serializer

- $\Delta t$  respect clk40sys = 0-21.875 ns

#### Clk40tx

- 40 MHz transmission clock

- Used to synchronise Serializer and Deserializer

### MPA Block Diagram

### Fast Counter Readout

Readouts the full matrix counters (15 bits x 1920 pixels) in 400 us

- I counter / 8 BX

- Compatible with standard readout

Allow to produce quickly S-Curve and start performance study and trimming

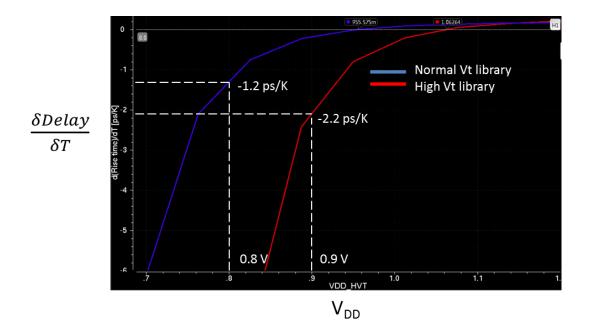

### Radiation Hardness requirement

- Outer Tracker Max.TID: 100 MRad (with no safety margin)

- 200 MRad Radiation model available thanks to M. Menouni (CPPM, RD53)

- Digital library results from DRAD chip, plot courtesy of L. M. Jara Casas (CERN, RD53)

### Corner requirements

- Best: I.I V, 0 C FF

- Typical: I V, 25 C, TT

- Worst: 0.9 V, 125 C, SS

- Worst Low Temperature: 0.9 V, -40 C ,

"Under **low-voltage supplies**, the cell performance (delay, transition time, setup/hold time) at **-40 C is worse** than at 125." [from Tech.manual]

### **Slowest corner**

Drain Current:

$$I_{\rm D} = \mu_{\rm n} C_{\rm ox} \frac{W}{L} (V_{\rm GS} - V_{\rm t})^2$$

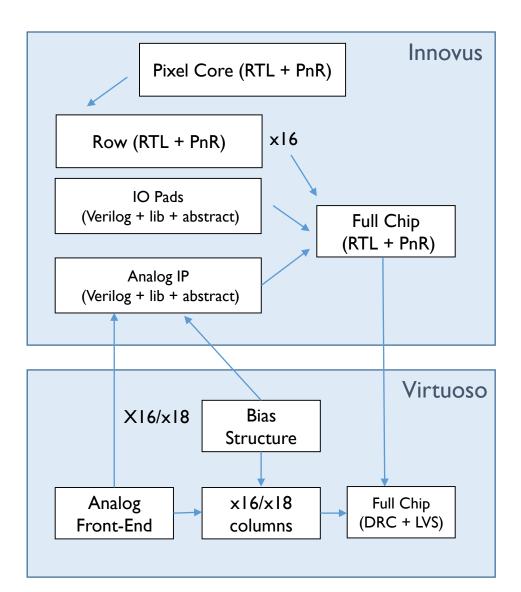

### P&R Hierarchy

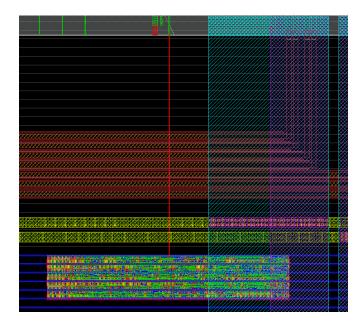

## **Pixel Core**

- Synthesized and PnR separately

- Integrated as Macro Block

- Placed and connected to FE manually

- Contains only FE electronics (no configuration)

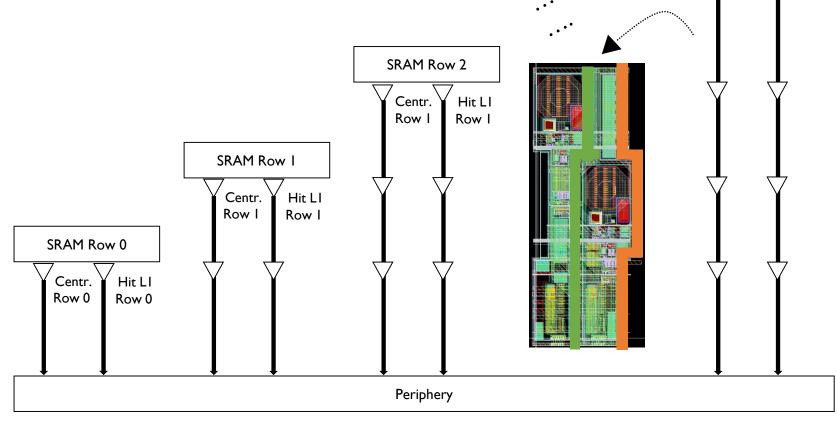

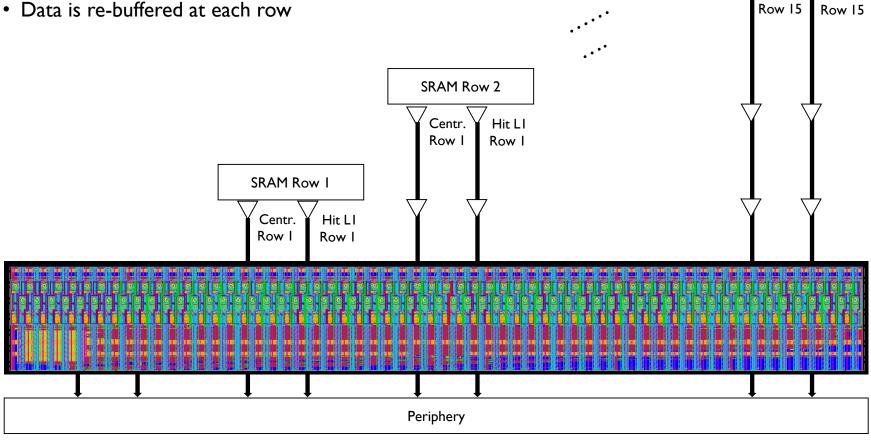

### **Pixel Row**

- Every row has dedicated lanes for data transmission to the periphery.

- SRAM are placed in correspondence of these lanes

- Data is re-buffered at each row

Hit LI

Row 15

SRAM Row 15

Centr.

Row 15

### **Pixel Row**

- Every row has dedicated lanes for data transmission to the periphery.

- SRAM are placed in correspondence of these lanes

- Data is re-buffered at each row

Hit LI

SRAM Row 15

Centr.

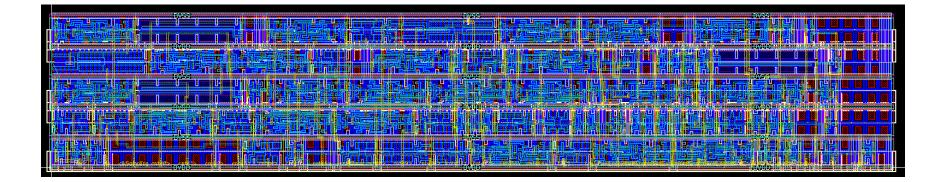

# Periphery

Integrates:

- Bias Block

- Clock Buffer and data re-buffering

- DLL

- eFuse

- IO Pad Area

- Digital logic (flat approach)

| 12  | 15 3 3 | 1   | 12       |        | J.R. | 44   | i sin     |    | 3   |         | R.    | 0    | į. | 2,2        | 2.5 | 15   | Ç, | 5.1 | 1 |     | 3        | R.   | Į,   | 1            | 2,2 | 2,2 | i. | 3     |

|-----|--------|-----|----------|--------|------|------|-----------|----|-----|---------|-------|------|----|------------|-----|------|----|-----|---|-----|----------|------|------|--------------|-----|-----|----|-------|

|     | 100    |     | H        | titit  |      |      | i î î î   |    |     | i i i i | litti |      | H  | aa         |     | E H  | 10 |     | I | tat |          |      | titi |              | I   | 80  |    | litit |

| 翻   |        | Ϋ́, |          |        | 儲    |      | di.       | ĥ  | Ĩ   | R       |       | i.   | ĥ  | a          | Ĩ   |      | ñ  |     | i |     | iii      |      | à    |              |     |     | i. | ä     |

|     |        |     | ĥ        | Úúr    |      |      | di.       | R  | ł.  | M       | iii   | iii  | ł  | i          | ł   |      | ũ  |     | l |     | ň        | h    | đđ   |              | h   |     |    | à     |

|     |        |     |          |        | AUS. |      |           |    |     |         |       |      | 10 |            |     |      |    |     | ļ |     |          |      |      |              |     |     |    |       |

|     |        |     | H        | đ      |      |      | 1743)     |    |     |         | RA    |      | H  | aa         |     | ITH  |    |     | Ì | tat |          | 1    | tili |              | ľ   |     |    | 88    |

| 翻   |        | Ϋ́  | h        | iii:   | 艄    |      | di.       |    | ñ   | Ŕ       | iii   | a.   | h  | h          | ł   | Ì    | h  |     | Ĥ |     | i        |      | đđ   |              | h   |     |    | iii   |

| άł. |        |     | ĥ        | đđ     |      |      | d.        | ĥ  | ł.  | M       | iii.  | h    | ł  |            | ł   |      | à  |     | U |     | ň        |      | à    |              | h   | R   |    | iii   |

|     | II.    |     |          |        |      |      |           |    | 3.5 |         |       |      |    |            |     | 11   | ļ  |     | ļ |     |          | II.  |      |              |     |     |    |       |

|     |        |     | H        | titi i |      |      | 1743)     |    |     | i i i   | tat   |      | H  | aa         |     | E TH |    |     | Ì | tat |          |      | titi |              | I   |     |    | iii   |

| 翻   |        | N.  |          | iù,    | 艄    | iii  |           | Ri | ñ   | T.      | ñ     | in i | ł  | à          | ł   |      | ù  |     | Î |     | iii      |      | à    |              |     |     | i. | à     |

| 龖   | iii    |     | i.       | ùù.    |      |      |           | À  | i.  | i.      | ini   | in   | h  | i.         | ł   |      | ù  |     | l | à   | M        |      | à    |              |     |     |    | à     |

| 334 |        |     |          |        | ALS. |      | s pils    |    |     |         |       |      |    |            |     | 15   |    |     | ļ |     |          | I.S. |      | 5 51<br>5 10 | ļ   |     |    |       |

| 102 | 100    |     | Ю        | 100    |      | aa:  | a î ĉi la |    | 101 | I       | 101   |      | H  | aa         |     | ET H | 10 |     | Ì | ιαι |          |      | u    |              | М   |     |    | idi   |

| 翻   |        | Ϋ́  | R        | iù,    | 儲    | iii  |           | ĥ  | ñ   | T.      | ñ     | in i | h  | àð         | ł   |      | ù  |     | Î | lai | à        |      | à    |              | h   | ł   | i. | a     |

| 闣   | Ri     |     | ĥ        | àù     |      | aa   |           | ĥ  | à   | ł.      | ini   | i.   | ł  | i.         | ł   |      | ù  |     | l | ā   | idi      |      | à    |              | h   |     |    | à     |

|     |        |     |          |        | ALS. |      | s als     |    |     |         |       |      |    |            |     | 15   |    |     | ļ |     |          | I.   |      | 5            | ļ   |     |    |       |

| 107 |        |     |          | 100    |      | aa:  | 121       |    |     | Int     | lai   |      | h  | aa         |     | E TH | 10 |     | ľ | ιαι |          |      | 101  |              | М   |     |    | aa    |

| 翻   | Ri     |     | Rit<br>I | άŭ     |      | aa   |           | Ř  | ù.  |         | iii   | in i | h  | àà         |     |      | iù |     | i | lài | idi<br>I |      | à    |              |     |     |    | iii   |

| 龖   | in.    |     | ĥ        | àù     |      | aa   |           | Ř  | à   | M       | iii   | in   | ł  | àà         | T.  |      | ù  |     | l | ñ   | ñ        |      | à    |              | h   | W   | N. | ŵ     |

|     |        |     |          |        |      |      |           |    |     |         |       |      |    |            |     |      |    |     |   |     |          |      |      |              |     |     |    |       |

|     |        |     |          | 100    |      |      |           |    |     |         | lac   |      |    | <b>a</b> a |     |      | 10 |     |   | lac |          |      |      |              |     |     |    | iđi   |

| m   | ITT    | T   | 11       | TH)    | ľ    | n II | T         | 1  | I   | 1       | 11    |      |    |            | 1   |      |    | 14  |   | 11  | T        | 1    | TI   |              | T   | ł   |    |       |

|     |        |     |          | , iii  |      |      |           |    |     | Iji l   |       |      |    |            | 1   |      |    |     |   |     | iţ,      |      | -ii  |              |     | III |    | ш,    |