The End-of-Substructure (EoS) card for the Strip Tracker Upgrade of the ATLAS experiment

Chaowaroj (Max) Wanotayaroj

Chaowaroj (Max) Wanotayaroj on behalf of DESY EoS Team

#### Introduction **ATLAS ITk Upgrade**

- HL-LHC will be a very harsh environment for ATLAS inner tracker (ITk)

- Peak luminosity ~  $7.5 \times 10^{34} cm^{-2}s^{-1}$  (200 collisions per bunch crossing) 593 mm

- Lifetime integrated luminosity ~ 3000 fb-1

- New, upgraded silicon tracker

- New readout electronic needed

- Faster

- Less materials

- Two geometries

- Stave for barrel

- Petal for endcap

- End of Substructure (EoS) card

- Sit on the "ear" of stave and petal

- Act as the interface between on- and off-detector components

- Handle data, command, and power delivery

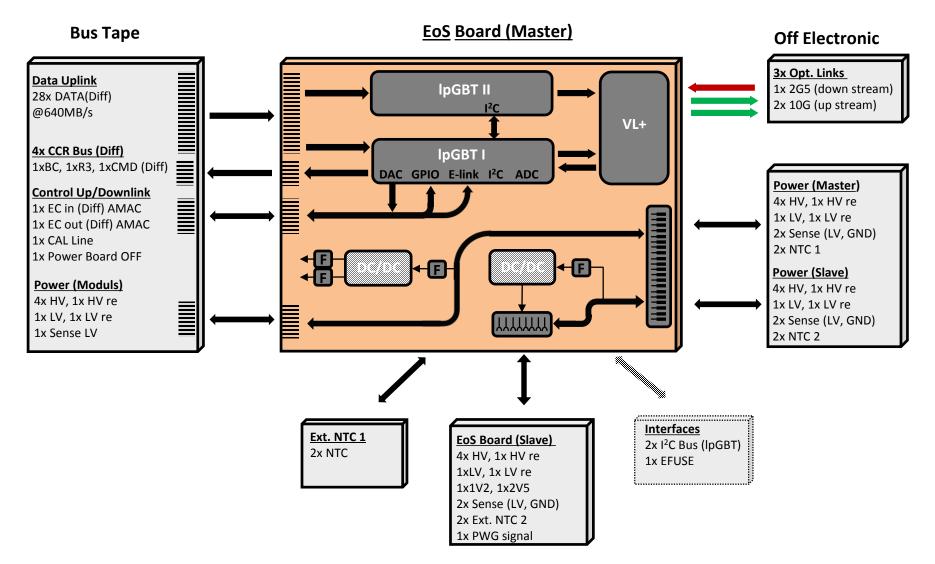

- Upstream: Up to 28 "Elinks" @ 640 Mbit/s

- Downstream: Clock and control data stream for front-end ASIC

- Both Low (LV) and High (HV) Voltage delivery 20/09/2018 TWEPP 201BESY.

Chaowaroj (Max) Wanotayaroj

modules

For

hybrids

1400 mm

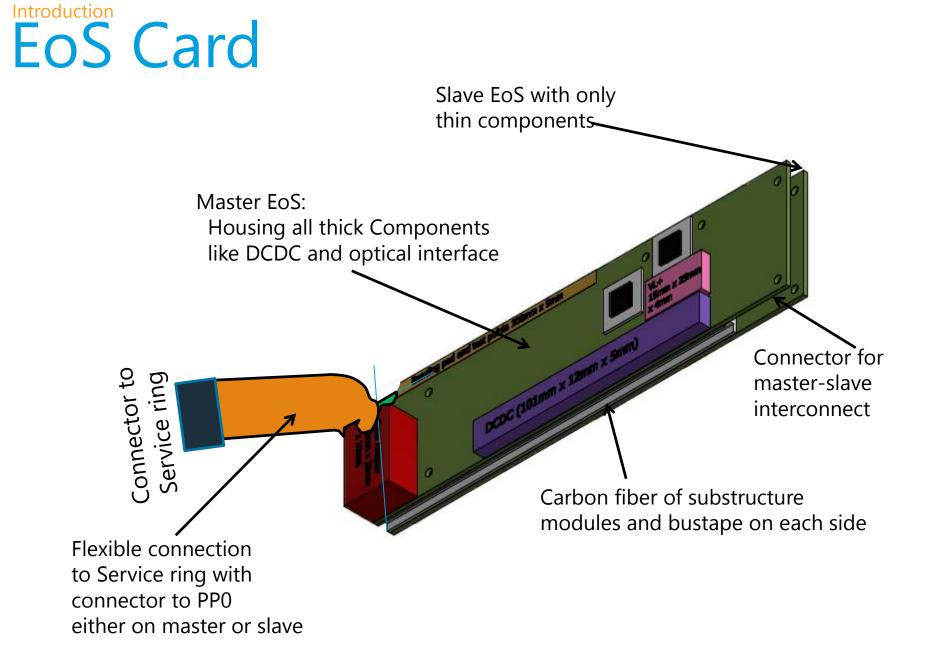

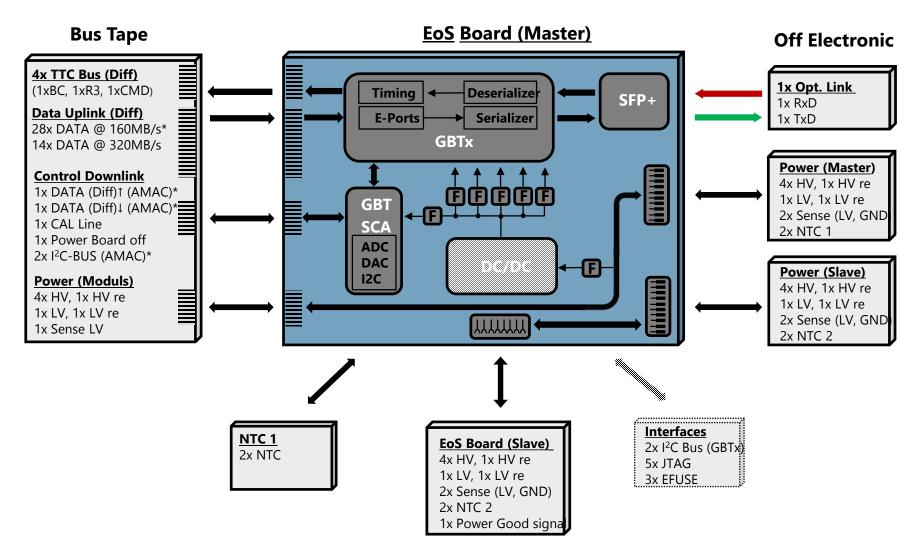

## EoS Card

- Major radiation-hard components from CERN:

- Low-power Gigabit Transceiver (lpGBT) ASIC

- Bi-directional optical link (VL+)

- DCDC convertor (BPOL12 and BPOL2.5)

- Multi-layer board using industry-standard PCB technology.

AMAC Control

E-Link SC

4 x TTC Bus

VL+

.....

laste

2.5 V

Slave

1.2 V

DC DC

- Nominal thickness 1.6 mm, maximum 1.8 mm

- Total height < 5 mm (constrain from detector design/assembly)</li>

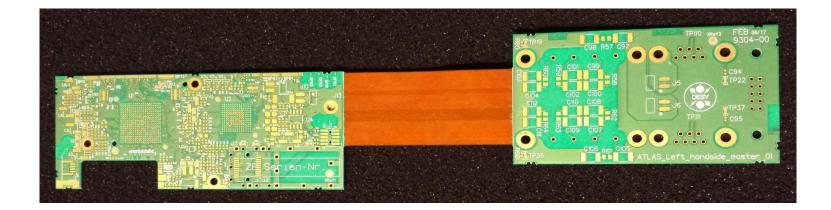

- Two variants called the "Master" and the "Slave"

- Glued to the each side of the mechanical structure (see next slide)

- Connected at one end

- 1 or 2 lpGBT each and a VL+ each

- Master will house the think components

- Fiber interface

- DCDC converters

- Flex cable for common power and external monitor connector

- In the slave for barrel, master for petal

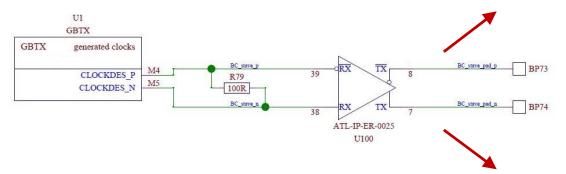

#### Schematic

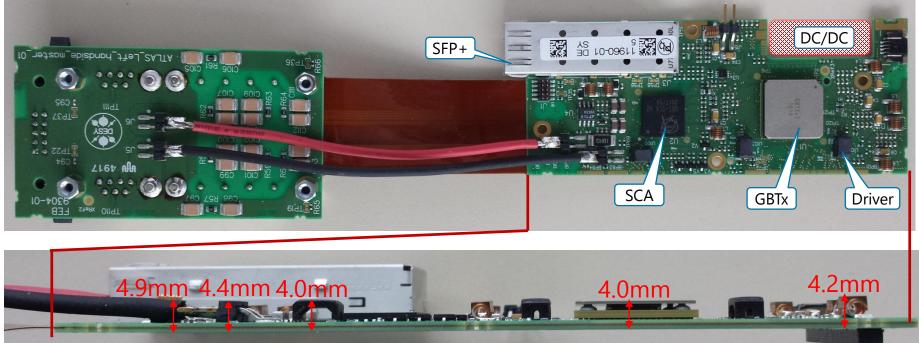

# GBTx-based Prototype

#### **EoS Prototype**

- The EoS will use IpGBT chip, but it is not yet available

- We built GBTx-based prototypes to learn about implementing the hardware and software

- We won't learn everything since lpGBT is different

- Unlike IpGBT, GBTx is accompanied by an ASIC decicated to slow control called GBT-SCA

- Built both master and slave cards

- The laser component, VL+, is also not yet available

- We use industry standard SFP+ for prototyping

- The height of SFP+ is over the limit but can be ignored

### **Evolution of the Prototypes**

#### VLDB

#### Test daughterboard

GBTx GBT-SCA SFP+

- We started from VLDB board, which is CERN reference design

- Also hosted the GBT-SCA for slow control, whose functionalities will be integrated into IpGBT

- VLDB is a fallback reference in case we run into a problem with our prototypes

- Next, we built a simple test daughterboard, hosting GBTx and SFP+

- We no longer use it, but still make them for other teams to get started on the GBTx chip

# Master Board

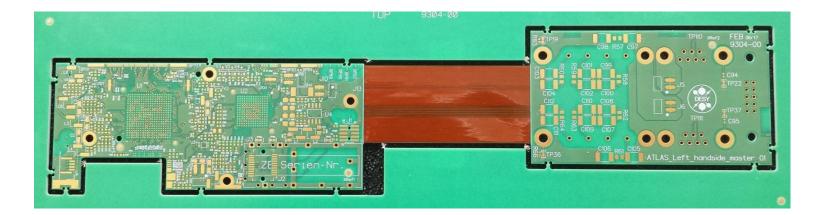

- So far, we built a total of 23 master boards

- 3 of them are version 0

- We have 20 of the latest version 1

- Current tallest component is at 4.9 mm, including the PCB

- All I/O channel can run up to 320 Mbps

# Slave Board

- For slave board, we built a total of 12 boards

- 2 are version 0

- We have 10 of the latest v.1

### Things We Learned

The current (v.1's) prototypes have no outstanding issues, but we've learned quite a lot while building them

- Wrong pull-up for the SFP+

- Passive (copper) cable is a good thing to check if optical one doesn't work

- Mistakes on connections between GBTx and SCA

- Wrong resistors

- Stricker design rule will check and make sure these are correct in the future

- PCB manufacture can made bond pads with too small pad size, serious over-etching (!?)

- We will perform visual inspection to catch this

- Elink channels have to be carefully selected

- Some are not available at high speed mode

#### **Functionality Test**

We developed both firmware (FPGA) and software (PC) for testing the boards

- Isolation resistor HV lines

- Line resistor HV, LV, NTC

- Electrical strength, residual current HV lines @ 1.5kV for 60 sec

- Current on LV and 1V5

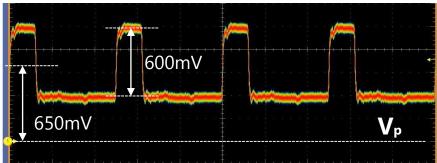

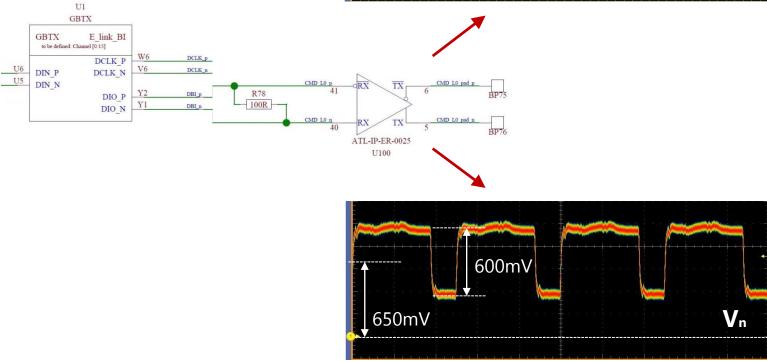

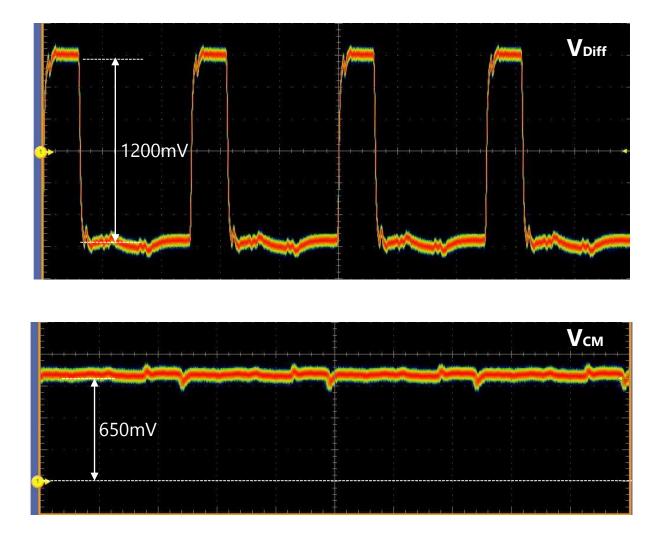

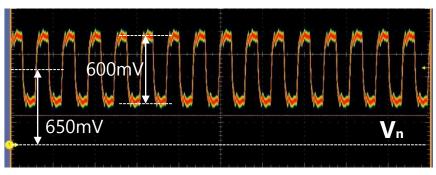

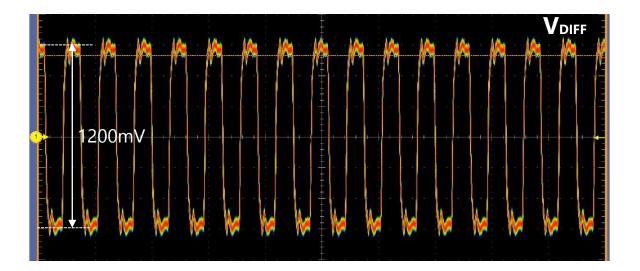

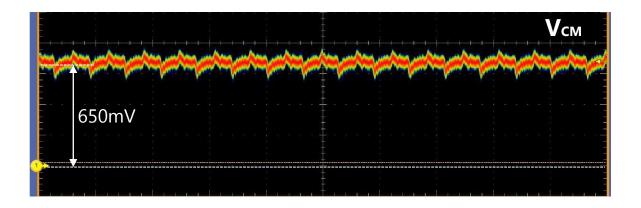

- Common mode voltage at output driver

- Fast control Signals (CCR) and AMAC down ( $V_{CM}$ ,  $V_{DIFF}$ ,  $I^2C$ )

- Test of all data input ports

- GBT-SCA:

- Read SCA's ID

- SCA's built-in I<sup>2</sup>C Bus

- GPIO

- ADC and DAC channel

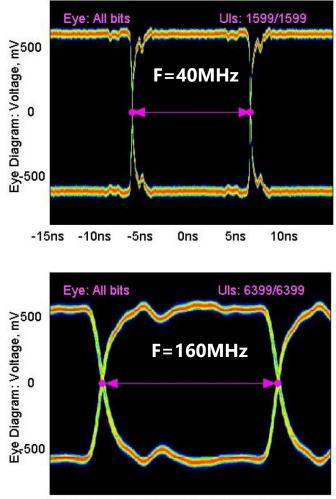

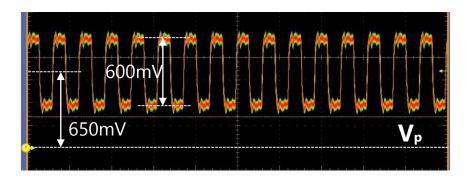

#### CMD Signal (E-Link)

• Sending "0001" @ 40 MHz (160 Mbps)

20/09/2018 TWEPP 201**BESY.**

### CMD Signal (E-Link)

• Sending "0001" @ 40 MHz (160 Mbps)

20/09/2018 TWEPP 201**BESY.**

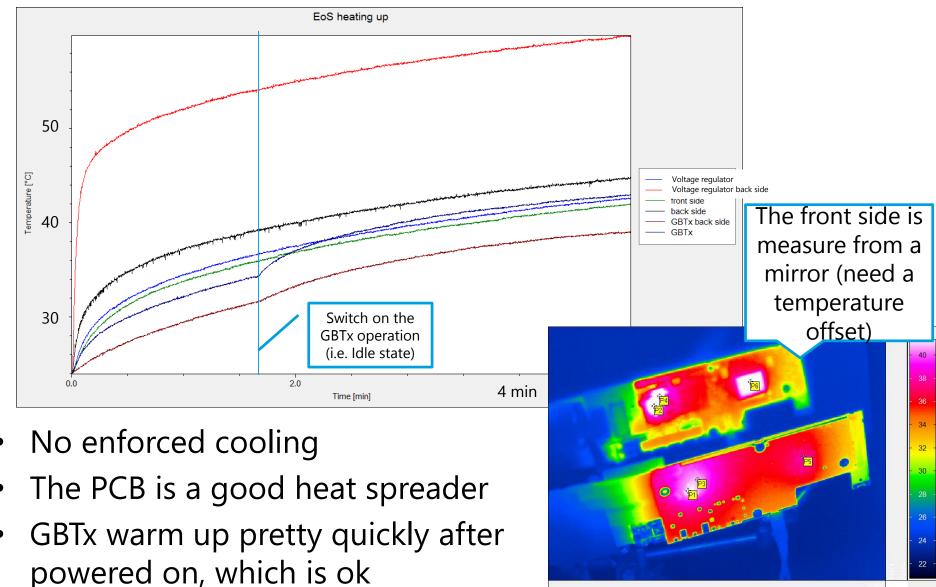

#### **Thermal Test**

20/09/2018 TWEPP 201**BESY.**

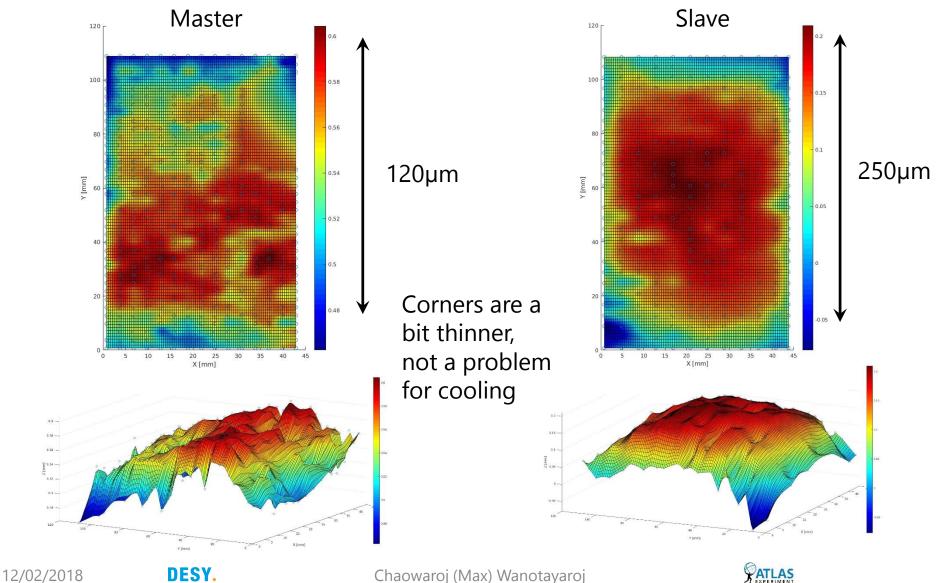

#### Flatness Test

• Measure the flatness of fully populated master and slave board

#### Bit Error Rate Test

- We ran a preliminary bit error rate (BER) test

- The tests have the full data path

- FPGA -> Optical link -> EoS (GBTx) -> Elink -> FPGA

- Ran with various configurations:

- 160 and 320 Mbps

- All Elinks on and only the used group on

- With a metal case around the EoS and without

- With twisted power cables(12v, 1.5v) and without

- With a prototype DCDC converter (supply only 12v)

- All tests are more than 15h (<10<sup>13</sup>) error-free

- Two tests were run for ~70h, both with only one Elink group turned on

- 160 Mbps with metal case and twisted power cables

- 320 Mbps without metal case and without twisted power cables

- Already better than the aimed 10<sup>12</sup>

- Should be able to do even better with a proper setup

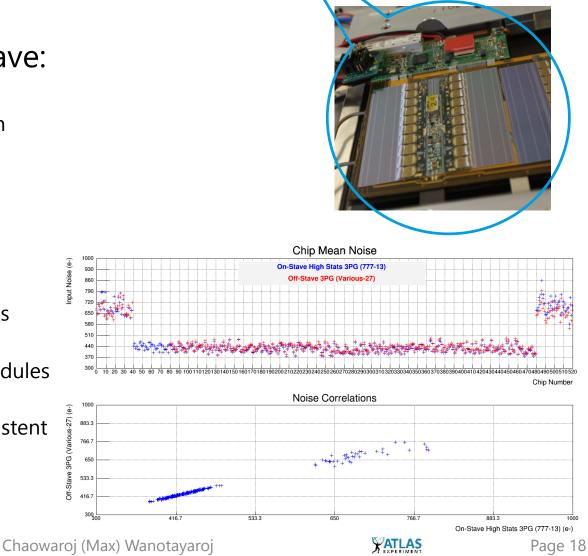

### **EoS with Real Stave**

- Our colleagues at Rutherford has put a master EoS prototype together with a real stave:

- Bus tape

- Full electrical modules at both ends

- 11 modules with mechanical sensors

- **Results:**

- LV, HV supply works

- Connection to pipe NTC works

- For temperature interlock

- Configure and readout all modules correctly

(e--27)

3PG (Various

Off-Stav

- Module results on stave consistent with those off stave

- The prototype works!

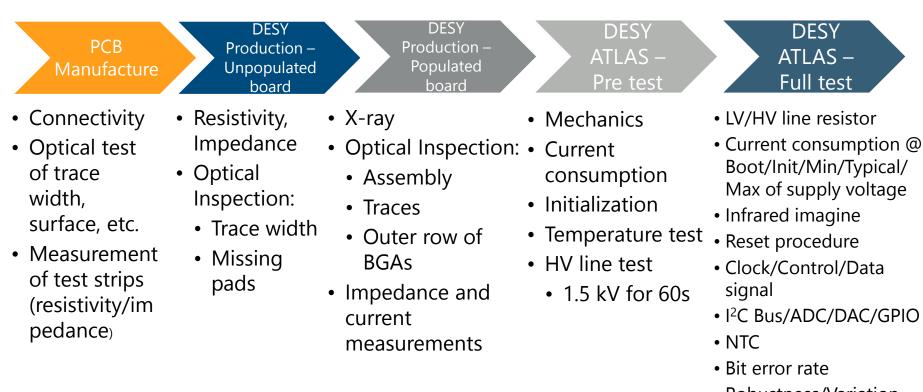

#### Test Plan

EoS sits on a single point of failure for a large part of the detector => need to be well-tested

- Robustness/Variation

- Noise on power line

DESY.

#### Summary

- We built EoS prototypes using available components

GBTx instead of IpGBT and SFP+ for VL+

- Learned how to connect and control the chips

- Perform functionality tests to make sure we build them correctly

- Check the thermal and flatness characteristic of our prototypes

- Master prototype has been used and tested with real stave

- Design concept for IpGBT/VL+ based prototypes are ready

- Vigorous tests are planned

#### Thank you

# Backup

20/09/2018 TWEPP 2018

#### Test Setup

- The basic setup are:

- EoS board (VLDB or the prototype)

- FPGA board (currently Xilinx KC705)

- PC

- We developed the firmware for the FPGA board based on the GBT-FPGA project from CERN

- We wrote a software on PC to control the testing on FPGA board

- Currently connected by UART interface

- Plan to move to faster link as we scale up

- Standalone instead of full ATLAS DAQ system

- Good enough for our needs

- Simpler to develop and debug.

- Can be ready as soon as we have the boards and not rely on other developments

Bonding pads:

EOS

Power

supply

12\/

**ELINK**

Power

AMAC-control

RX

TCC

Master

Clock

3x LHC

**FPGA**

KC 705

Setup schematic

$\mathsf{PC}$

#### Firmware and Software

- We first integrated GBT-SC IP core to the main GBT-FPGA example designed

- Include both external control (EC) to GBT-SCA and internal control (IC) of the GBTx itself

- Test with VLDB, then try it on our prototypes

- Can do both IC and EC communication

- Configure the GBTx via the optical link instead of I2C

- Read the SCA's unique ID and control various functionalities

- Controlling of the FPGA and the SCA chip has been implemented on the PC software

- Enable us to perform functionality test fairly quickly

- In the future, automation will be build into the software so anyone can run the test

- Add bit error rate test

### Schematic Diagram

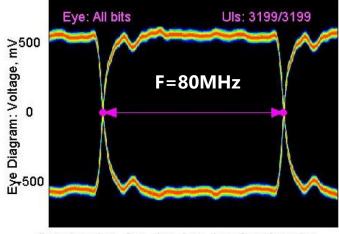

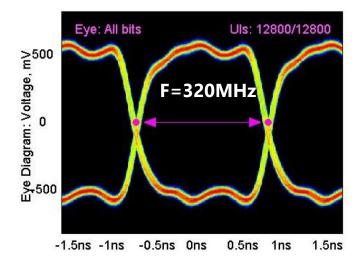

#### Bunch Clock Signals ("TTC")

-2.5ns2ns-1.5ns1ns-0.5ns0ns 0.5ns1ns 1.5ns2ns

-5ns -4ns -3ns -2ns -1ns Ons 1ns 2ns 3ns 4ns

#### Bunch Clock @ 160 Mbps

20/09/2018 TWEPP 201**BESY.**

#### Bunch Clock @ 160 Mbps

20/09/2018 TWEPP 201**BESY.**

#### 1. Manufacturer lests for unpopulated EoS boards

| PCB Manufacturer |                                                         |    |           |

|------------------|---------------------------------------------------------|----|-----------|

|                  | Parameter                                               | TT | Resources |

| 1.1              | Connectivity tests on board<br>(E-Test against Netlist) | -  | -         |

| 1.2              | Optical test of trace width, surface                    | -  | -         |

| 1.3              | Measurement of Test Strips (resistivity/impedance)      | -  | -         |

DESY.

| DESY Production I |                                                                                                                 |                  |                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|

|                   | Parameter                                                                                                       | тт               | Resources                          |

| 2.1               | <ul><li>Measurement of test strips on diff. layers:</li><li>Resistivity</li><li>Impedance</li></ul>             | 0,1 min<br>1 min | Quadrupole Tester<br>Reflectometer |

| 2.2               | <ul><li>AOI of the unpopulated PCB</li><li>trace width, missing pads,</li><li>Surface of bonding pads</li></ul> | 2 min            | AOI System                         |

| DESY Production II |                                                                                                                                                                                                                     |          |              |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|

|                    | Parameter                                                                                                                                                                                                           | тт       | Resources    |

| 3.1                | X-Ray and destructive solder ball tests (1. board)                                                                                                                                                                  | 3600 min |              |

| 3.2                | Readability of the RF-ID Chip                                                                                                                                                                                       | 0,1 min  | RF-ID Reader |

| 3.3                | <ul> <li>Optical check:</li> <li>Correct assembly</li> <li>Check of none tested traces (TP&lt;-&gt;BP)</li> <li>Outer row of BGAs</li> </ul>                                                                        | 5 min    | AOI System   |

| 3.4                | <ul> <li>Impedance and U/I measurements:</li> <li>Signal connections from/to lpGBT</li> <li>Isolation between NTC lines/HV-return/LV-return and GND</li> <li>Line resistor of HV lines (CON&lt;-&gt;BP)?</li> </ul> | 3 min    | Polartester  |

DESY.

| DESY ATLAS I |                                                                                                                                                                                 |                             |                                          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------|

|              | Parameter                                                                                                                                                                       | TT                          | Resources                                |

| 4.1          | <ul> <li>First check of EoS:</li> <li>Mechanical checks (dimensions, position of drill holes, flatness)</li> <li>Current consumption</li> <li>Correct initialisation</li> </ul> | 5 min<br>0,1 min<br>0,1 min | PS, TB, PC                               |

| 4.2          | <ul> <li>Temperature test</li> <li>Long Term Test @ 40°C for 100 h</li> <li>Cycle Test @ +30°C30°C, 2x in 16 h</li> </ul>                                                       | 6000 min<br>960 min         | Environemental<br>chamber ,<br>PS,TB, PC |

| 4.3          | <ul><li>Test of HV lines @ 1,5kV for 60 sec</li><li>Electrical strength</li><li>Residual current</li></ul>                                                                      | 10 min                      | HV-PS                                    |

|     | DESY ATLAS II                                                                                                                                                    |                             |                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|

|     | Parameter                                                                                                                                                        | тт                          | Resources                    |

| 5.1 | <ul><li>Line resistor on HV line between:</li><li>Connector and Bus Tape Bond Pads</li></ul>                                                                     | 1 min                       | LV-PS, TB, PC                |

| 5.2 | <ul><li>Line resistor on LV line between:</li><li>Connector and Bus tape Bond Pads</li><li>Connector and DC/DC-converter Bond Pads</li></ul>                     | 1 min                       | LV-PS, TB, PC                |

| 5.3 | <ul> <li>Current consumption for 1V8/2V5</li> <li>After boot process</li> <li>After initialisation</li> <li>At min/typ/max. values of supply voltages</li> </ul> | 0,1 min<br>0,1 min<br>5 min | LV-PS, TB, PC                |

| 5.4 | Check of PCB/ASIC temperature<br>(infrared imaging)                                                                                                              | 4 min                       | LV-PS, PC, Box,<br>IR Camera |

| 5.5 | <ul><li>Reset signal:</li><li>Function test</li><li>Delay time of the reset signal (Ub/PWG)</li></ul>                                                            | 0,1 min<br>0,1 min          | LV-PS, TB, PC                |

| 5.6 | <ul><li>CCR- and AMAC down Signals:</li><li>Function Test</li><li>VCM, VDIFF, Timing</li></ul>                                                                   | 1 min<br>5 min              | LV-PS, TB, PC                |

|      | DESY ATLAS II                                                                                         |                 |               |

|------|-------------------------------------------------------------------------------------------------------|-----------------|---------------|

|      | Parameter                                                                                             | тт              | Resources     |

| 5.7  | Data Input Ports (E-Links) and AMAC up:<br>• Function Test                                            | 1 min           | LV-PS, TB, PC |

| 5.8  | <ul> <li>I<sup>2</sup>C Bus signals:</li> <li>Function Test</li> <li>Vhigh, Vlow, Timing</li> </ul>   | 0,1min<br>1 min | LV-PS, TB, PC |

| 5.9  | GPIOs:<br>• Function Test                                                                             | 0,1min          | LV-PS, TB, PC |

| 5.10 | Test of ADC/DAC                                                                                       | 0,1min          | LV-PS, TB, PC |

| 5.11 | Test of NTC temperature measurement                                                                   | 0,1min          | LV-PS, TB, PC |

| 5.12 | BER Test for 10 <sup>-13</sup> @ 640Mbit/s and 14 E-Links                                             | 20 min          | LV-PS, TB, PC |

| 5.13 | <ul><li>Robustness and variation test with:</li><li>DC/DC converter</li><li>broken filter C</li></ul> | 5 min           | LV-PS, TB, PC |

| 5.14 | Noise on power lines from board                                                                       | 5 min           | LV-PS, TB, PC |

#### **DESY Stock**

<u>Agenda</u>

HV-PS : High voltage power supply Adapter)

LV-PS : Low voltage power supply **DESY**.

TB : Test bench (FPGA board and EoS Test

PC : Personal Computer Chaowaroj (Max) Wanotayaroj