Imperial College London

Science & Technology

Facilities Council

Karlsruher Institut für Technolo

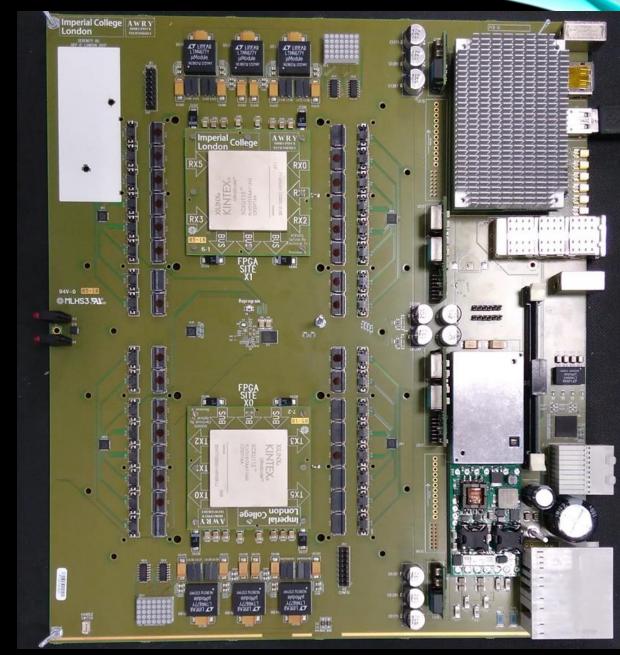

# WHAT IS SERENITY?

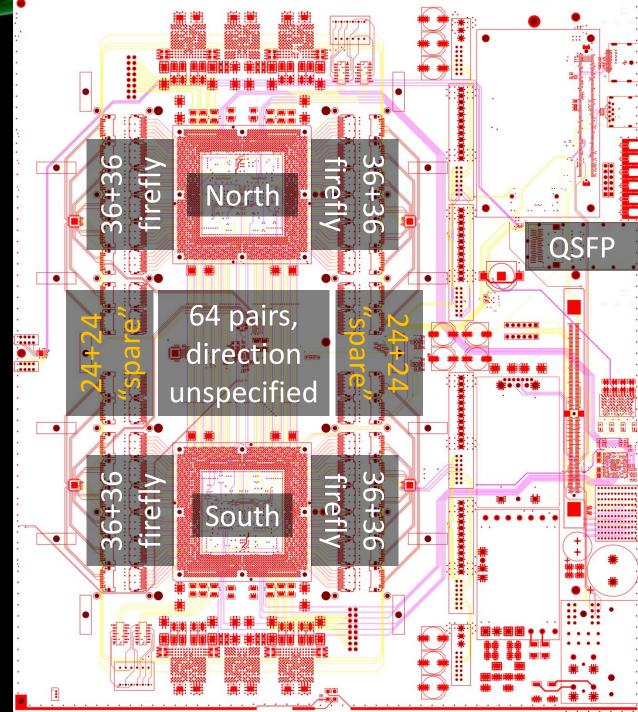

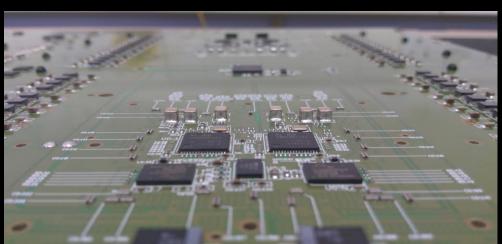

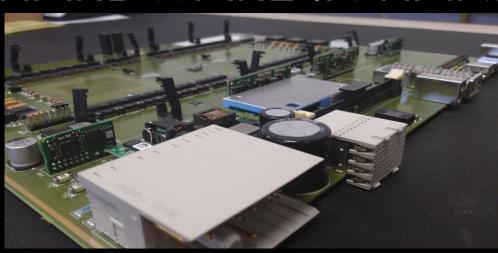

- ATCA Development Platform

- Carrier Card

- Services Power, Clocks, Optics, Interconnects, IPMC & CPU

- Daughter Cards

- Data Processing FPGAs

- Firmware & Software

- Generic, Flexible Infrastructure

# AN ASIDE: COTS COMPONENTS

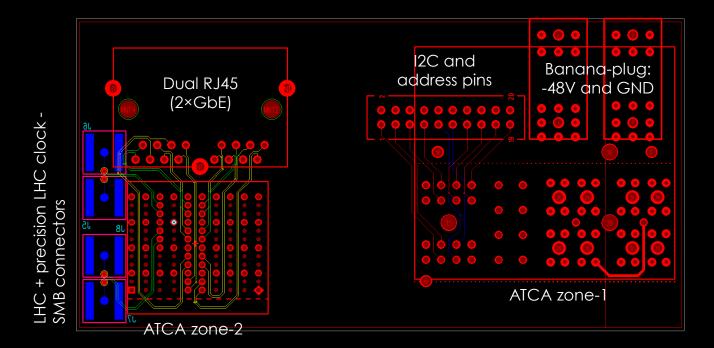

#### ATCA low level control – IPMC

- Available from CERN

- Runs the commercial standard software

#### Ethernet

- Switch with integrated Gigabit Ethernet Phys

- AC coupled via capacitors

- Small form factor 1cm<sup>2</sup>

- VLAN capable

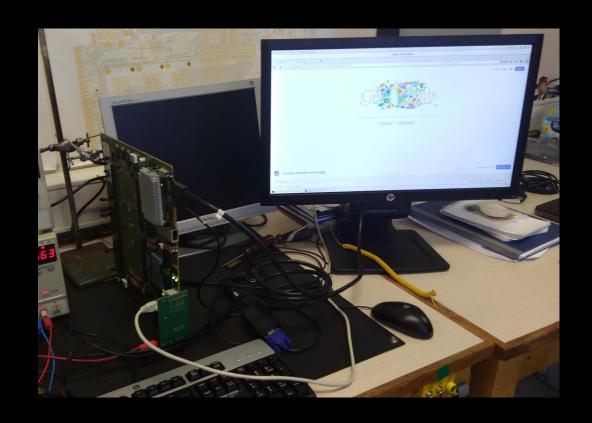

#### Standard Intel x86 COM-Express Type 10 CPU

- Running standard Centos Linux

- What sys-admins want, not necessarily what hardware engineers want!

- PCIe interface to FPGAs

- Clean separation of hardware, firmware and software

# WHICH PROBLEMS IS SERENITY MEANT TO SOLVE?

- Different projects want different FPGAs, different optical and electrical connectivity

- Can one board make everyone happy?

- If not, can we at least provide a rapid-prototyping platform for ATCA?

- Bulk of cost concentrated in FPGAs, bulk of potential failure modes in carrier

- Can we decouple financial risk from production risk?

# **HOM**s

- FPGAs on Daughter-cards:

- Freedom to choose your preferred family, package, generation, (vendor?)

- Freedom to choose your balance of optical and electrical connectivity

- Carrier testing done with FPGAs safely in their static-bags

### WHAT WERE THE CONCERNS?

- We started the project with serious concerns over choice of ATCA, particularly:

- Thermal management

- Optics must be kept below 50C or longevity drops at shocking rate

- Acoustic noise

- Others expressed concern over

- Interposer signal integrity

- Supplying power to FPGAs

- Cooling FPGAs on daughter-cards

- Limited prior experience with 16 or 25G links

- Whether different institutes could really produce their own daughter-cards?

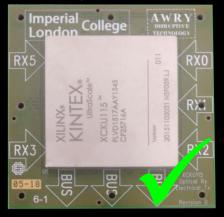

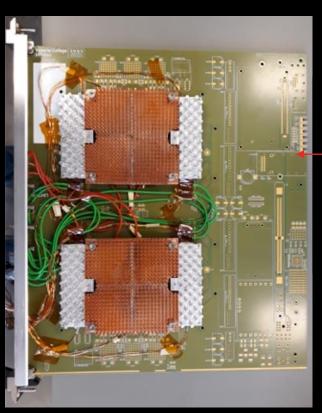

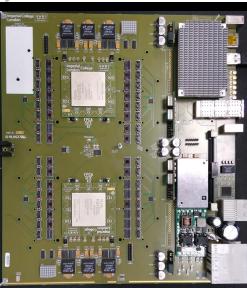

# CAN DIFFERENT GROUPS PRODUCE DAUGHTER-CARDS?

- IC Xilinx KU115: Symmetric & Daisy Chained

- KIT Xilinx KU15P

- TIFR Xilinx VU9P

Saclay – a clock-network analysis daughter card

All optical KU115, Imperial

Mixed optical/electrical KU15P, KIT

Clock-performance analyzer CEA Saclay

In progress, All optical VU9P, TIFR

Daisy-chain, optical in KU115, Imperial

Daisy-chain, optical out 19/0%/2013, Imperial

#### 0.00 dB (00000) √ 0.00 dB (00000) 0.00 dB (00000) PRBS 7-bit PRBS 7-bit PRBS 7-bit ∨ 0.00 dR (00000) ∨ 0.00 dB (00000) 0.00 dB (00000) ∨ 0.00 dB (00000) ~ 0.00 dB (00000) PRBS 7-bit ✓ 0.00 dB (00000) 0.00 dB (00000) ∨ 0.00 dB (00000) ∨ 0.00 dB (00000) < 0.00 dB (00000) PRBS 7-bit PRBS 7-bit PRBS 7-bit √ 0.00 dB (00000) 0.00 dB (00000) ✓ 0.00 dB (00000) 0.00 dB (00000) ✓ 0.00 dB (00000) ∨ 0.00 dB (00000) 0.00 dB (00000) 0.00 dB (00000) √ 0.00 dB (00000) PRBS 7-bit PRBS 7-bit PRBS 7-bit √ 0.00 dB (00000) 0.00 dB (00000) ✓ 0.00 dB (00000) ~ 0.00 dB (00000) ✓ 0.00 dB (00000) ✓ 0.00 dB (00000) ∨ 0.00 dB (00000) ∨ 0.00 dB (00000) 0.00 dB (00000) ~ 0.00 dB (00000) ~ 0.00 dB (00000) ✓ 0.00 dB (00000) ✓ 0.00 dB (00000) v 0.00 (III (00000)

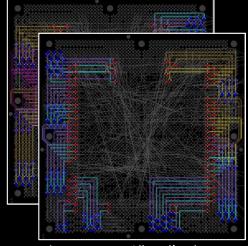

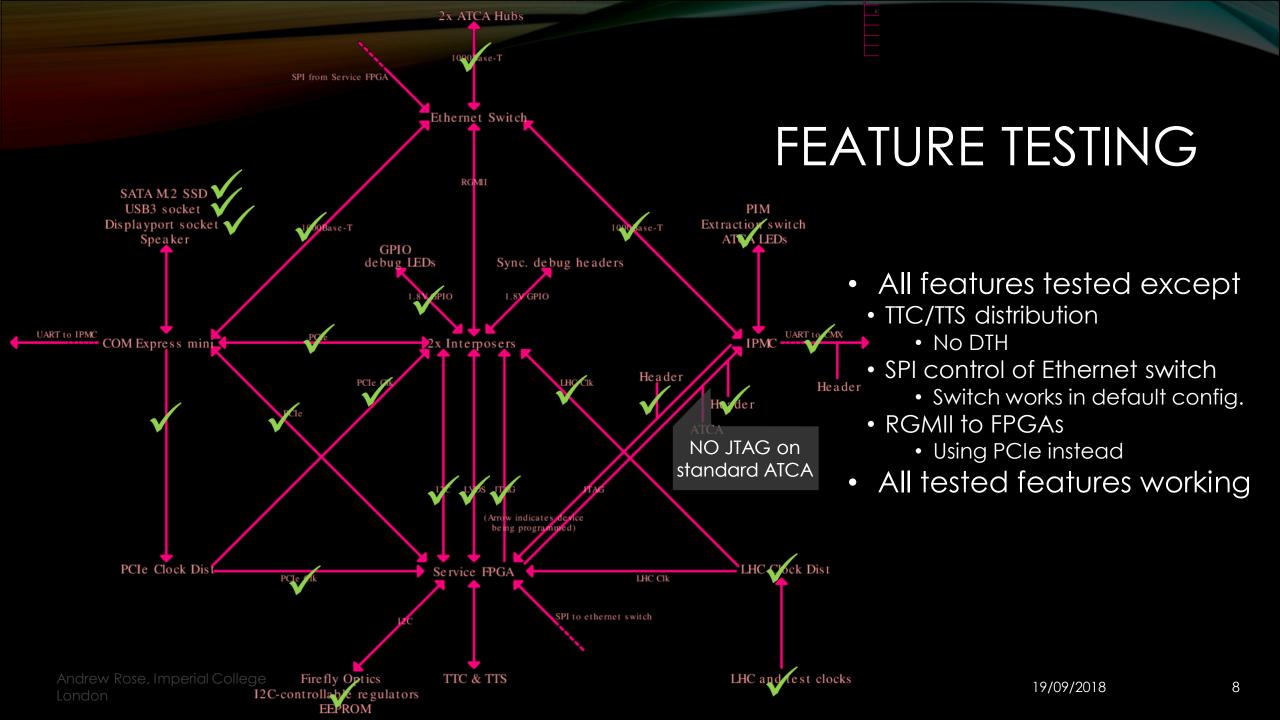

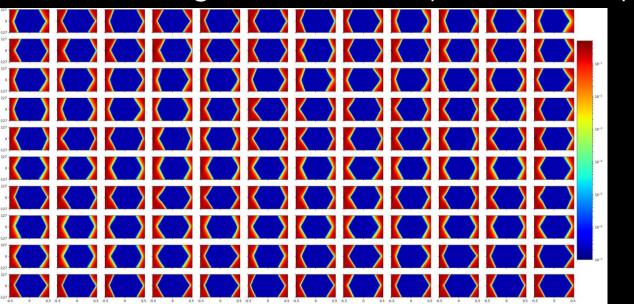

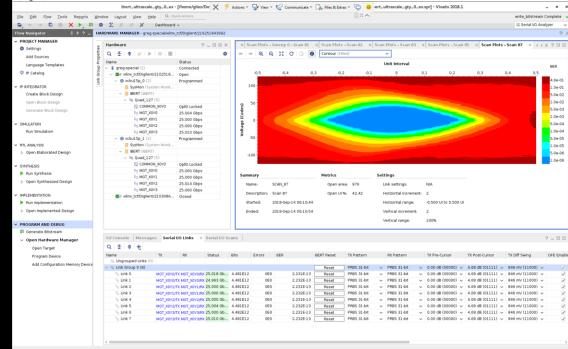

### LINKS - INTERNAL LOOP

- 120 simultaneous IBERTs

- 16Gbps, Near-end PMA loopback. Default settings

- Each link passed 1e15 bits No errors

- 120Pb of data through silicon

- Indicated good clock and power stability

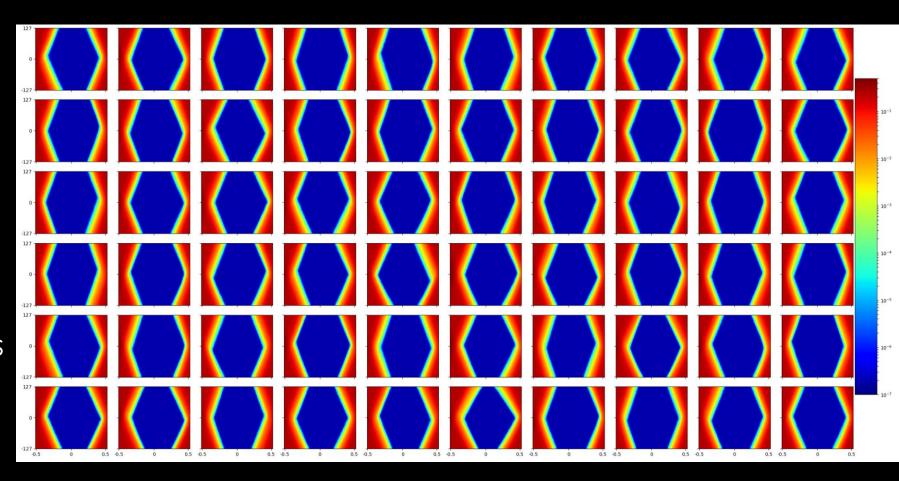

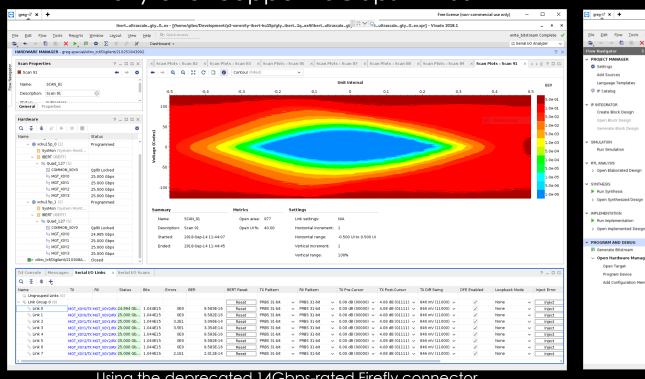

# COPPER LINKS – EYE DIAGRAMS

- Inter-interposer bus

- Two independent FPGAs

- 16Gbps, DFE disabled, No Preor Post-Cursor

- Each link passed

8e14 bits No errors

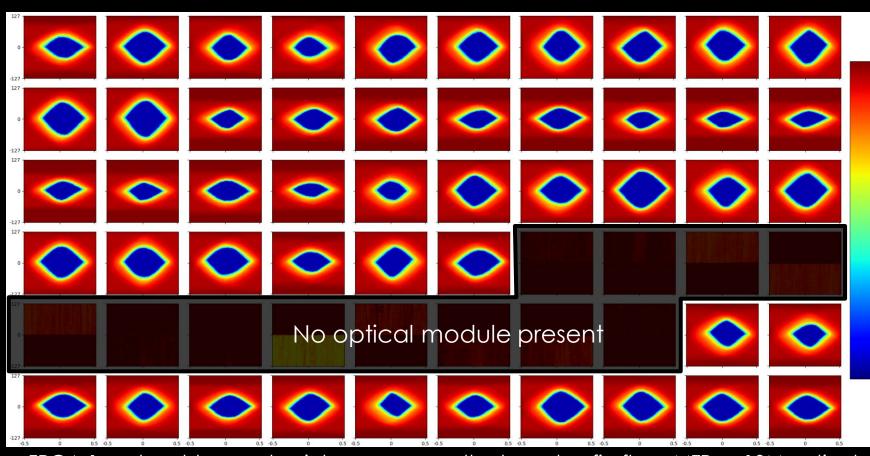

# OPTICAL LINKS – EYE DIAGRAMS

- Firefly optics

- Two independent FPGAs

- 16Gbps, DFE disabled, No Preor Post-Cursor

- Default optical module settings

- 10m optical fibre

- Each link passed

8e14 bits No errors

FPGA 1  $\rightarrow$  daughter-card  $\rightarrow$  interposer  $\rightarrow$  motherboard  $\rightarrow$  firefly  $\rightarrow$  MTP  $\rightarrow$  10M optical cable  $\rightarrow$  MTP  $\rightarrow$  firefly  $\rightarrow$  motherboard  $\rightarrow$  interposer  $\rightarrow$  daughter-card  $\rightarrow$  FPGA 2

# 25GBPS INITIAL RESULTS

#### Firefly over copper 25Gbps PRBS31

#### Inter-interposer bus 25Gbps PRBS31

Using the deprecated 14Gbps-rated Firefly connector

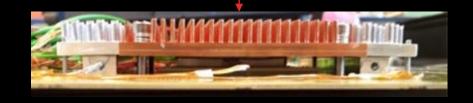

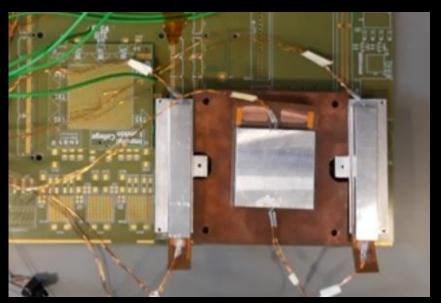

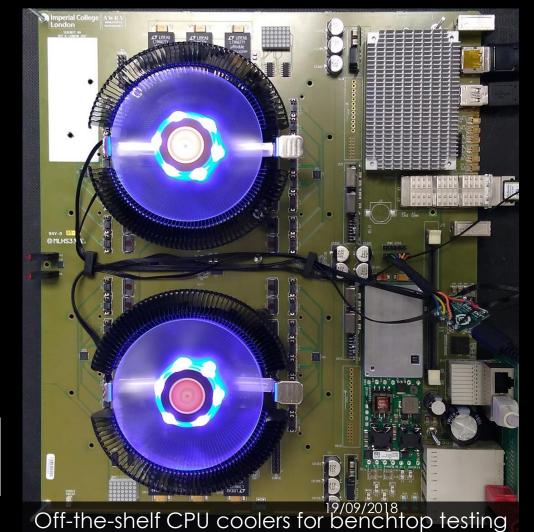

# THERMAL & MECHANICAL TESTS

- Thermal simulations

- Physical thermal studies at CERN

- Mechanical component design, studies into stress on FPGA solder balls and stress on PCBs under way at IC

# TEST STAND AT CERN

- Kapton heaters

- Comtel Crate

- Front-Back Airflow

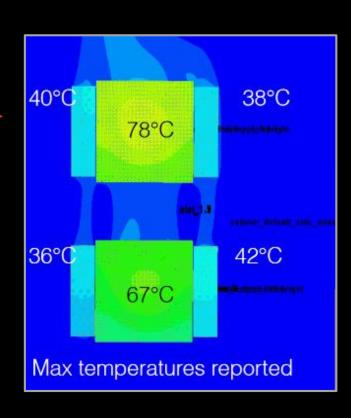

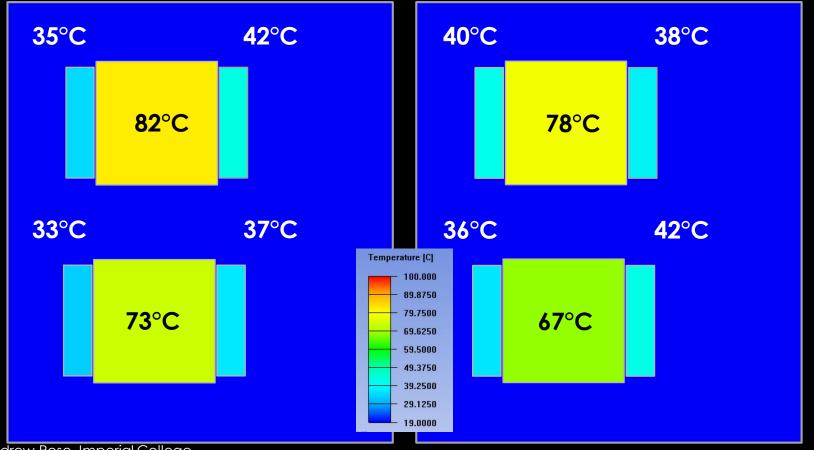

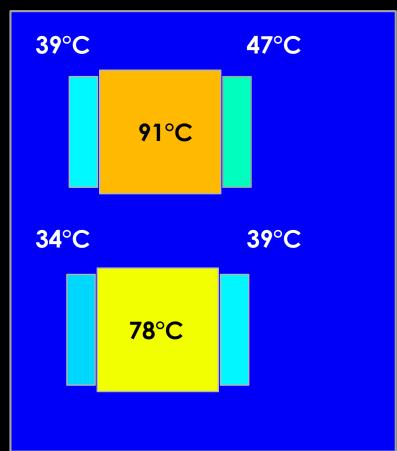

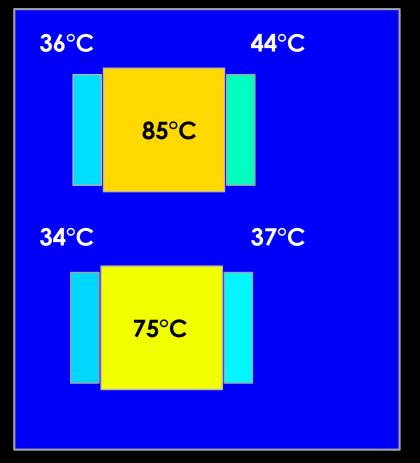

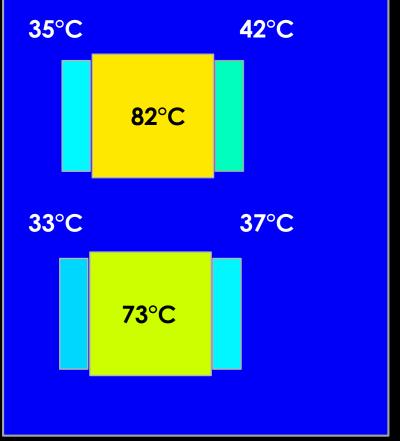

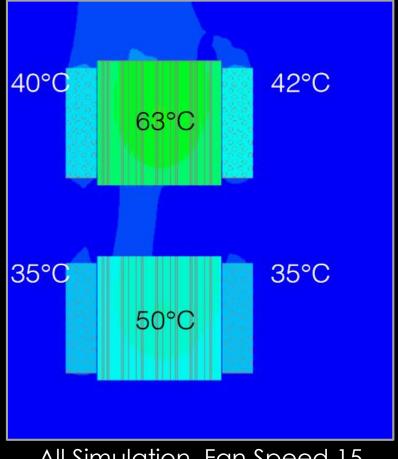

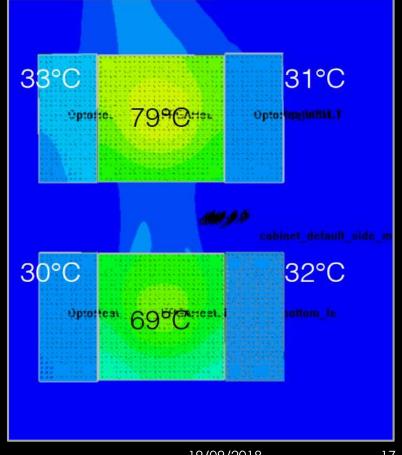

## THERMAL TEST RESULTS

Measurement, Fan Speed 15

**Simulation**, Fan Speed 15

- Standard CERN crate made by Schroff, Vertical Airflow

- FPGAs @ 90W each

- Max temperature 100 °C

- Optics @ 10W each

- Max temperature 50 °C

- May increase to 20W so need margin

- Simulation by Ansys

- KIT also running simulations with Mentor FloTHERM for comparison

Andrew Rose, Imperial College London

19/09/2018

# FAN SPEED

Measurement, Fan **Speed 10**

Measurement, Fan **Speed 13**

Measurement, Fan **Speed 15**

Andrew Rose, Imperial College London

19/09/2018

London

#### Simulations suggest significant improvement with custom heatsink.

Validation of simulation with measurement under way

# 38°C 40°C 78°C 42°C 36°0 67°C Max temperatures reported Andrew Rose, Imperial College

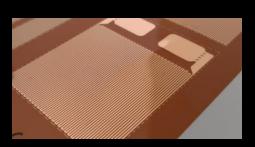

# HEATSINK TYPE

London

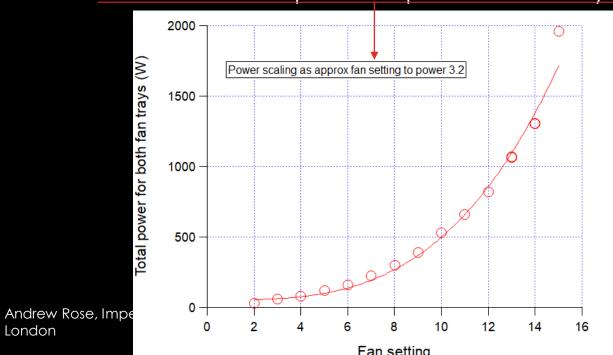

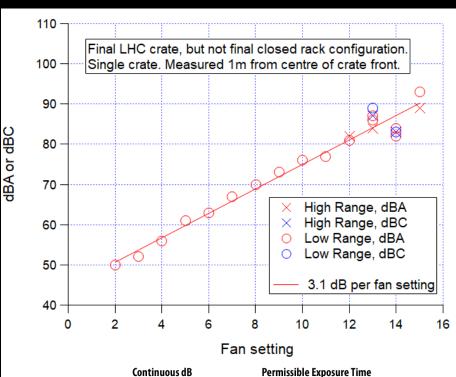

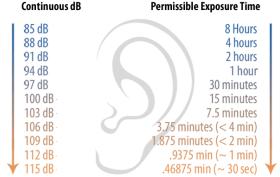

# CRATE NOISE & POWER

- Measurements of the running ATCA system still a cause for concern regarding

- Aural (acoustic) health and safety

- Power-consumption required to cool system

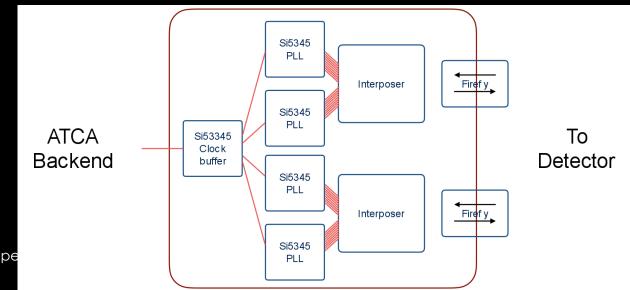

# **CLOCK-DISTRIBUTION TESTS**

- Serenity is TDR proposal for CMS HGC DAQ, trigger, clocking and control board.

- HGC requires precision timing distribution

- CEA Saclay have been testing whether Serenity's clocking performance meets HGC requirements

### CLOCK-DISTRIBUTION TESTS

- 320.624MHz test clock (HGC precision-timing frequency)

- External clock-source, RMS = 1.3ps

- Serenity tested at 20GS/s (Eval board at 40GS/s)

| Measurements by<br>CEA Saclay | SI5444 Eval board<br>for comparison<br>(4 outputs) | Serenity North<br>LHC clock<br>(9 outputs) | Serenity South<br>LHC clock<br>(9 outputs) | Serenity Overall |

|-------------------------------|----------------------------------------------------|--------------------------------------------|--------------------------------------------|------------------|

| Random Jitter                 | 0.9ps                                              | 1.6ps                                      | 1.4ps                                      | 1.8ps            |

| Deterministic Jitter          | 1.9ps                                              | 3.2ps                                      | 3.1ps                                      | 4.2ps            |

| RMS                           | 1.3ps                                              | 2.3ps                                      | 2.1ps                                      | 2.8ps            |

Based on these results, Serenity's contribution to system jitter is minimal and it can be considered a "pure clock distribution" node DXXIKP

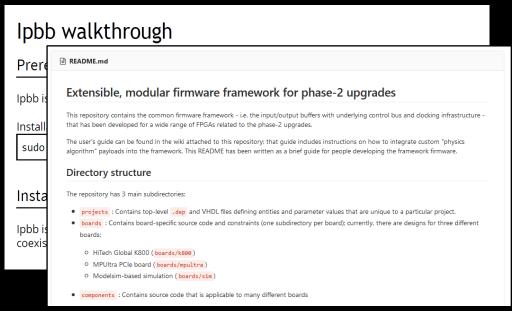

### Ipbus-over-PCle worked out-of-the-box

- Have built upon the success we had with MP7 model in Phase-1 upgrades

- Infrastructure firmware EMP

- Build Tool IPBB

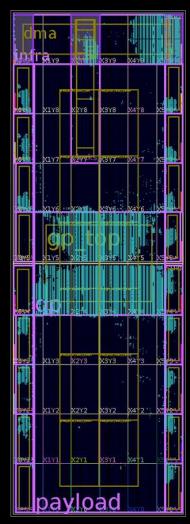

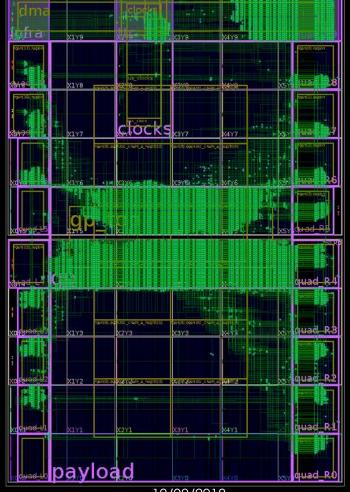

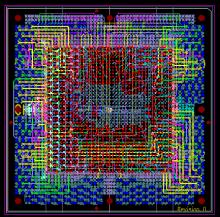

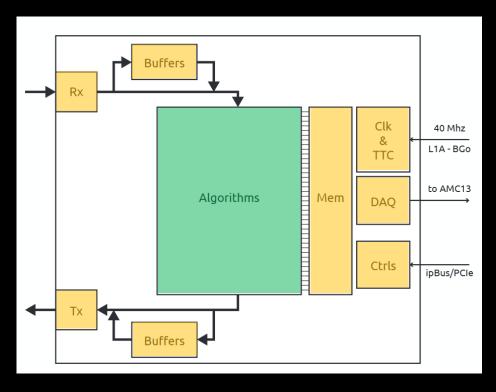

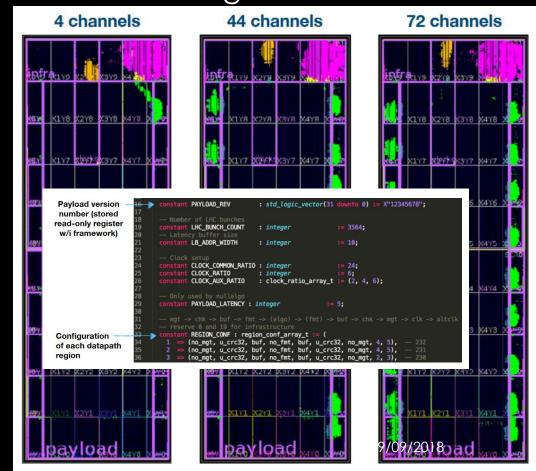

### FIRMWARE

Infrastructure separated from payload for algorithms

# EMP FIRMWARE

Different boards

Different configurations

### CONCLUSIONS

- Serenity has succeeded in its initial aims of allowing multiple types of FPGA and user-specified connectivity, and also in mitigating risk

- Different institutes have successfully produced their own daughter-cards, each with different generations & models of FPGAs

- Concerns over interposer signal integrity and supplying power to FPGAs seem unfounded

- Performance at both 16G and 25G looks good

- Cooling of both optics and FPGAs on daughter-cards looks manageable

- General concerns over power and noise of LHC-scale systems built using ATCA remain

### MHAT NEXTS

- 20 Revision 1.1 cards in assembly now

- A number of cards destined for "time-share test-stands" at CERN

- Allow systems to test "full-stack" algorithms from source to sink

- Also, horizontal integration with CERN DTH & online software when they become available

- Remaining cards destined for collaborating institutes

# THANKS FOR LISTENING! ANY QUESTIONS?

CEA Saclay: Ozgur Sahin, Pierre-Anne Bausson

IC: Andrew Rose, Duncan Parker, Greg Iles

INFN Pisa: Giacomo Fedi, Piero Giorgio Verdini, Andromachi Tsirou

KIT: Luis Ardila, Matthias Balzer, Thomas Schuh

RAL: Tom Williams, Alessandro Thea, Kristian Harder

TIFR: Shashi Dugad, Raghu Shukla, Irfan Mirza

University of Ioannina: Stavros Mallios

Imperial College London

Science & Technology Facilities Council

institute undamental earch Karlsruher Institut

I do not own, nor do I assert any right of ownership over, the Serenity logo.

It is just a cool logo from a cool TV series (Firefly)

and subsequent film (Serenity).

I urge you to go and buy them both: They're a lot of fun.

# SPARES & BACKUP

# HARDWARE IN HAND

# MICRO-BACKPLANE

# X1 to X0 Polarity over configuration copper error X0 to X1 over fibre No optical modules plugged

## OFF-CHIP LINK IBERTS

- 120 simultaneous IBERTs

- 16Gbps

- 60 through fireflys, 60 over copper

- Default settings

- With highlighted caveats, each link passed 8e14 bits

- No errors

- 1board, 85Pb between FPGAs

19/09/2018

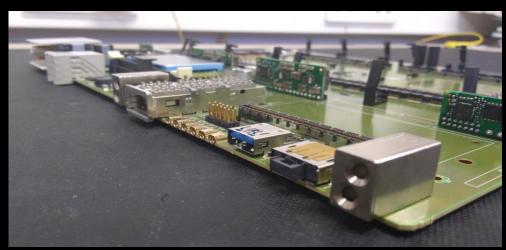

## CARRIER TESTING

- Com-express & GBE

- HD display-port, USB, SSD, Centos-7, GBE<sup>†</sup> all working

- Artix-7 Service FPGA

- JTAG, Flash, Heartbeat LED, Clocks, PCle to Com-express all working

- IPbus-over-PCle

- The existing MP7 I2C-over-lpbus and JSM JTAG-over-IPbus infrastructure also work unchanged

# COMMUNICATION VIA PCIE

- JTAG to both KU115s via the Artix

- Digilent USB-debugger via Artix GPIO

- XVC-over-lpbus-over-PCle

- Directly over Ipbus

- Heartbeat LEDs

- Debug LED arrays

- Programming Flash

- PCIe & system clock

```

00:1f.3 SMBus: Intel Corporation Atom Processor E3800 Series SMBus Controller (rev 11) 01:00.0 Serial controller: Xilinx Corporation Device 7021 02:00.0 Serial controller: Xilinx Corporation Device 8031 03:00.0 Serial controller: Xilinx Corporation Device 8031 04:00.0 Ethernet controller: Intel Corporation I210 Gigabit Network Connection (rev 03) Andrew Rose, Imperial College London

```

### EMP FIRMWARE: EXAMPLE

- Many large Xilinx parts are now multi-die

- Super Logic Region

- How do algorithms developed in MP7 port to UltraScale?

- HT Track Trigger

- Geometric Processor Component

- Concern over inter SLR routes

- Quickly port to KU115

- VU9P or KU15P also available.

- Only 20% of inter-die routes used.