# VMM and the SRS - update

Michael Lupberger (CERN)

### What happened since December 2017

#### New student from Central China Normal University for 6 months

→ Yan, will work on DDR3 memory on the FECv\_6 (FPGA coding)

#### BrightnESS test beam in December

→ → first neutron test beam with VMM3 hybrids (four) and better software (see presentation on last miniweek, data analysis still ongoing)

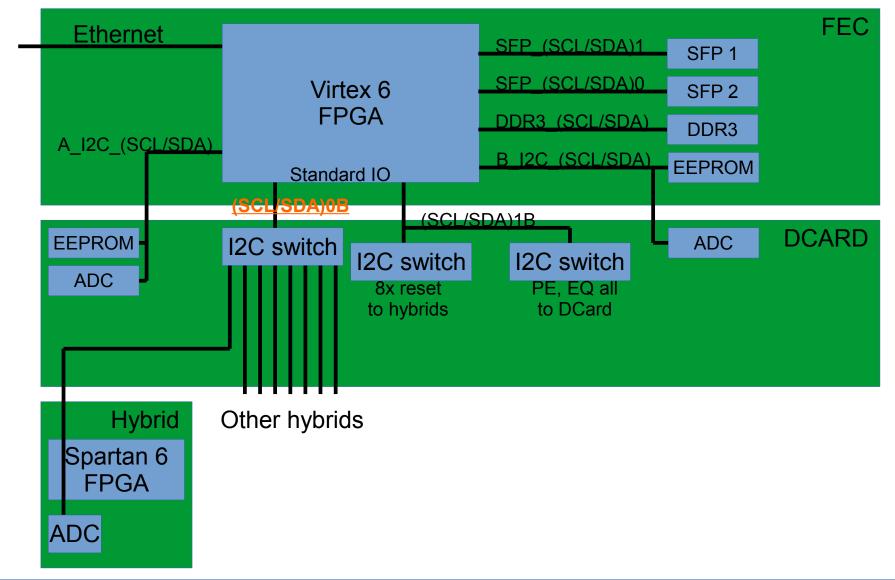

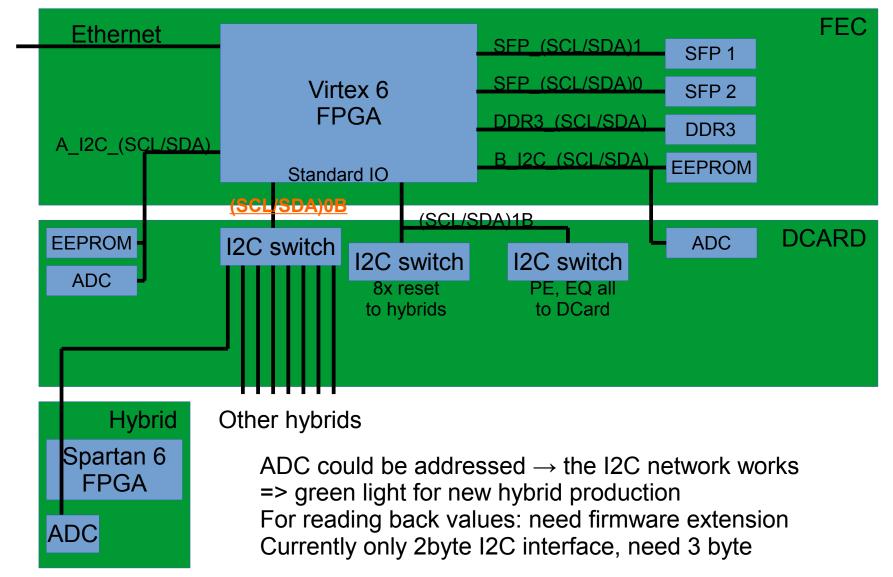

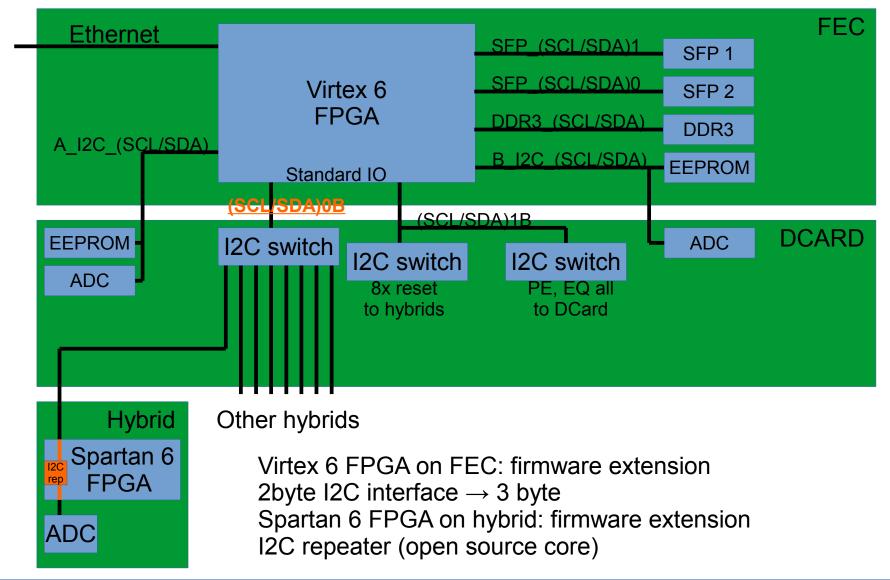

#### I2C test of new ADC for hybrid

→ Firmware implementation of new ADC for full functionality

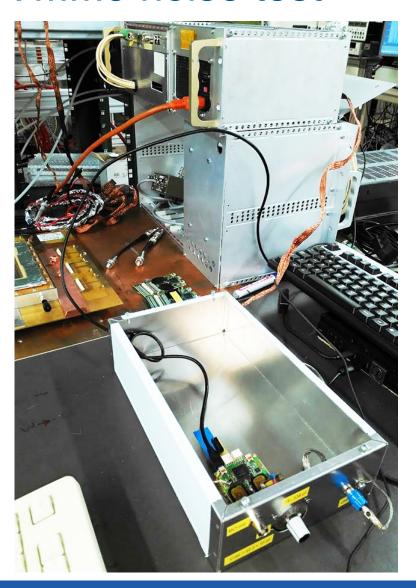

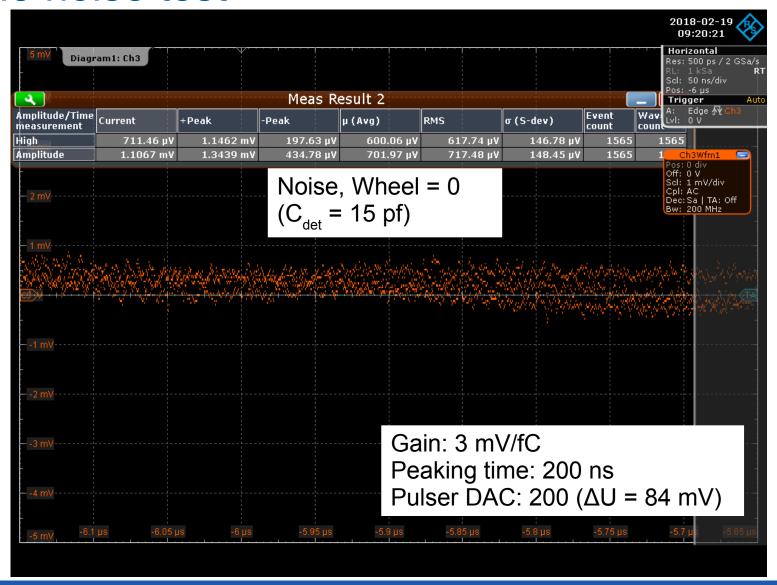

#### VMM3 hybrid noise test

→ currently ongoing

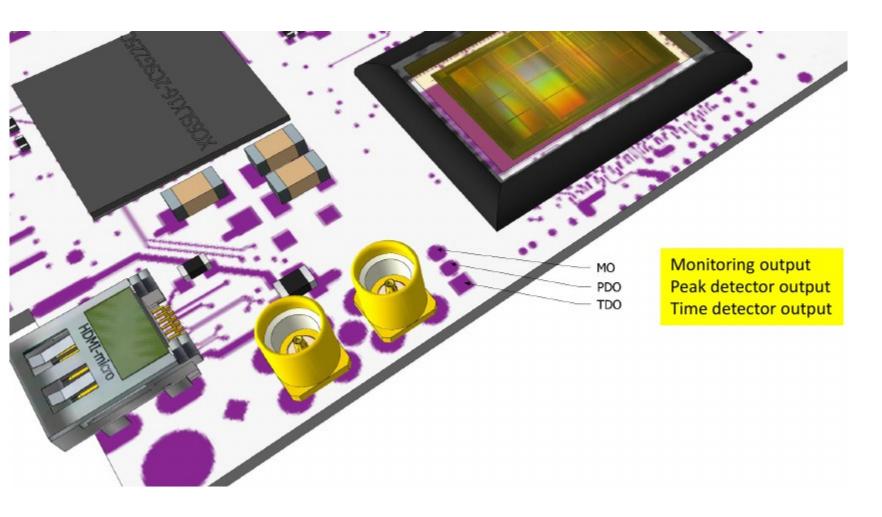

#### New ADC

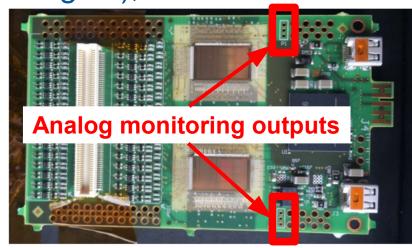

#### Necessary to read monitoring outputs

- M0: Can be set to output global threshold DAC, pulser DAC, temperature sensor level, band-gap reference and for every channel: baseline (and signal), threshold level

- tdo: baseline and ramp

- pdo: baseline and pulse amplitude

For fast signals (ramp, pulse), ADC is to slow

We need it for calibration of baselines and thresholds

#### I2C network

#### I2C network

#### **I2C** network

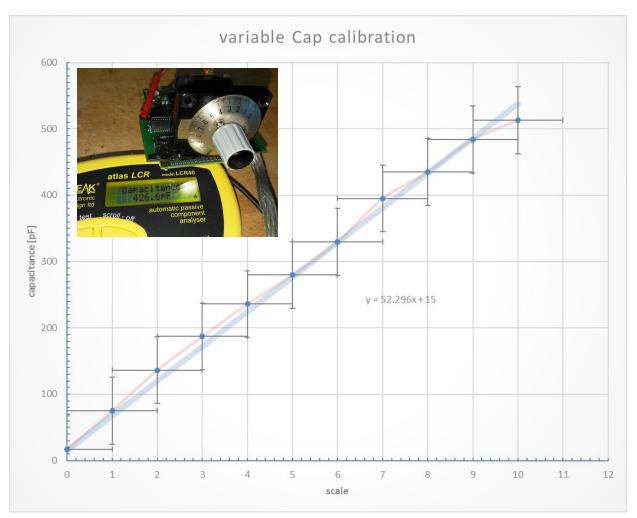

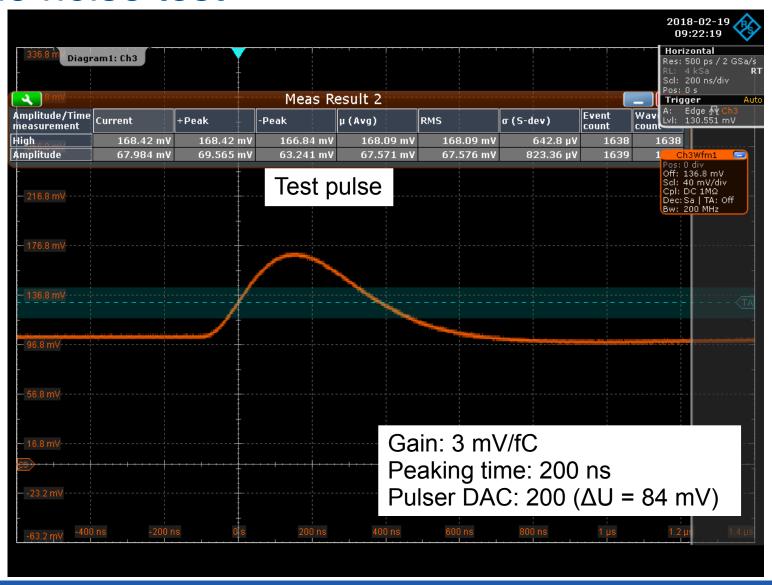

Principle of measurement

Compare baseline rms (mV) with test pulse U\_test (mV)

VMM internal test pulse has know charge (ΔU on C)

$\Delta U$ : measure TestPulse DAC at M0 output for x=0, and x=200

U\_test: measure amplitude of test pulse at M0

Baseline rms: measure without test pulse at M0

$$\begin{aligned} &\mathsf{ENC} = \frac{\mathsf{U}_{\mathrm{rms}}}{e-} \ / \frac{\mathsf{U}_{\mathrm{peak}}}{\Delta Q_s} \ = \ \frac{U_{test} \ Cs}{e-} \ * \ \frac{U_{rms}}{U_{peak}} \end{aligned} \qquad \begin{aligned} &\mathsf{Cs} = 300 \ \mathsf{fF} \\ &\mathsf{ENC}[\mathsf{e-}] = 1864.5 \, \frac{\mathsf{U}_{\mathsf{rms}}[\mathsf{mV}] \, \mathsf{U}_{\mathsf{test}}[\mathsf{mV}]}{\mathsf{U}_{\mathsf{peak}}[\mathsf{mV}]} \end{aligned}$$

Systematic effects:

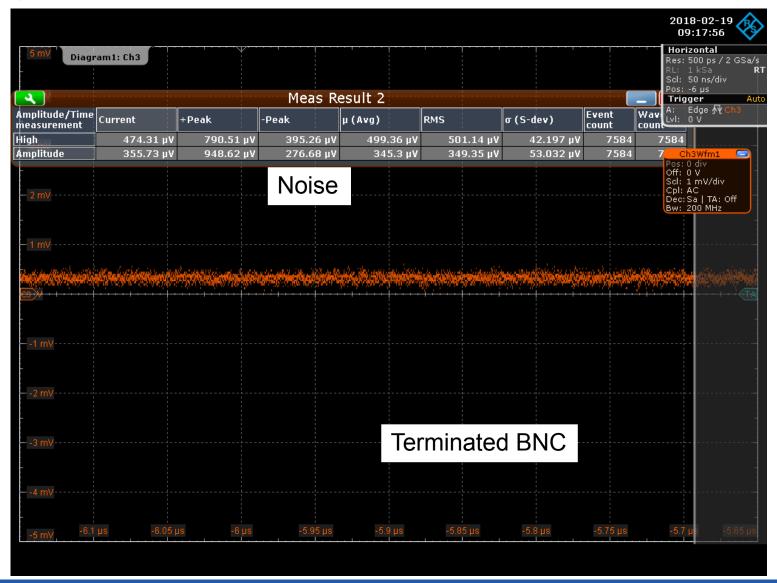

Oscilloscope noise → quadratic subtraction

External noise → shielding box, grounding, go out of lab

Still: External noise can not be excluded completely

⇒ VMM noise could be smaller then measured

Internal noise → disable test pulser, readout while measuring

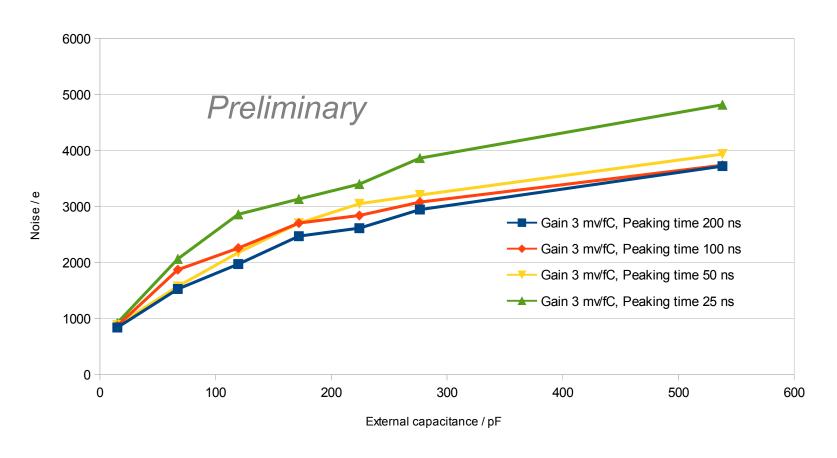

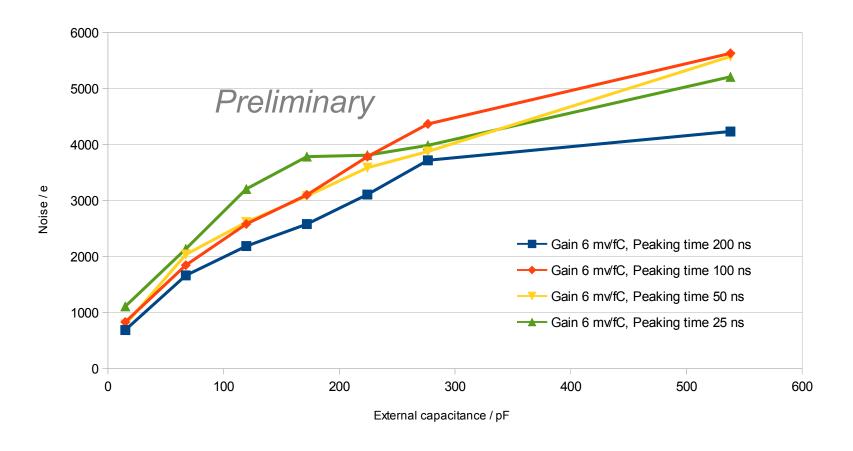

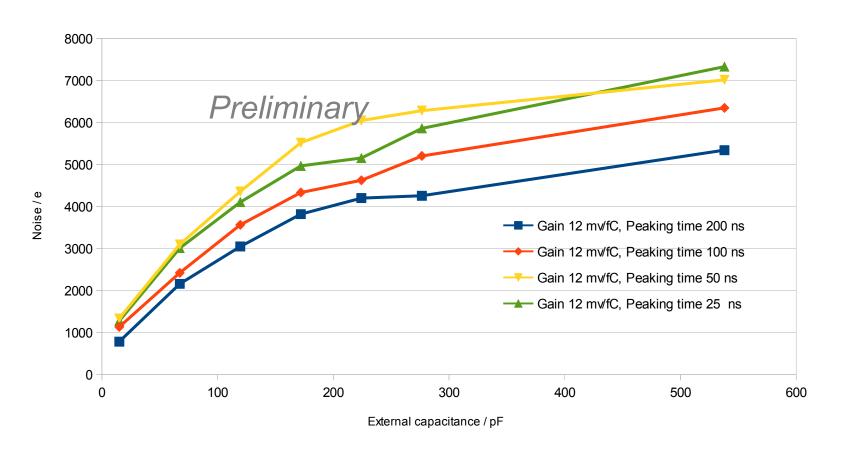

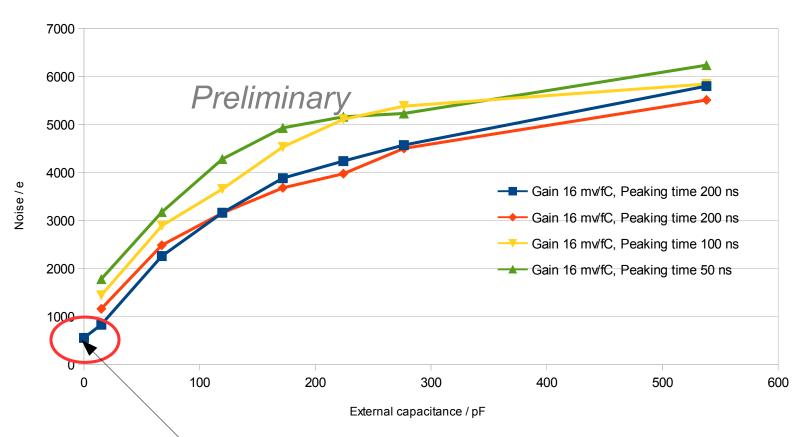

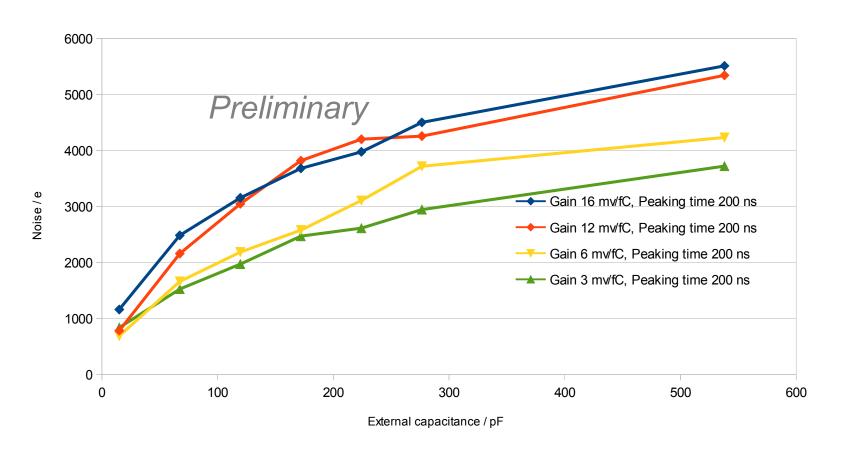

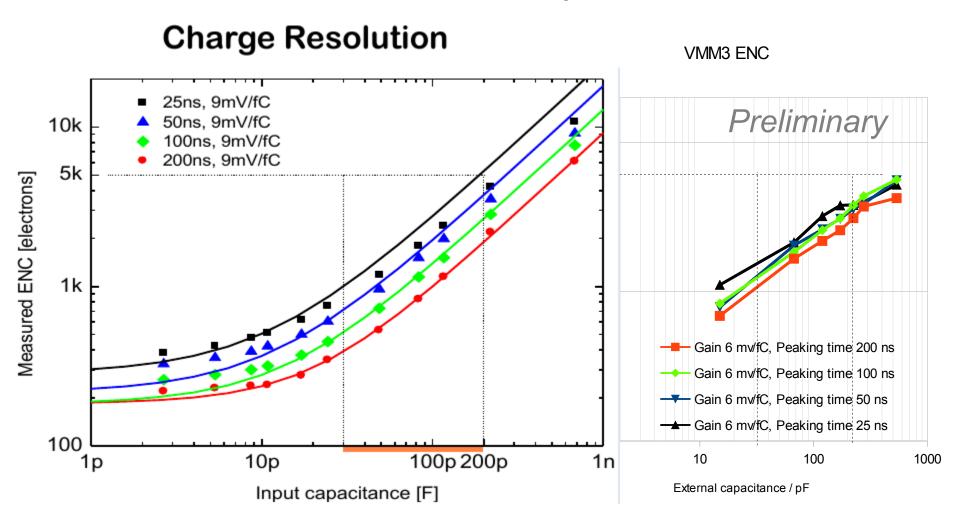

#### VMM3 ENC

VMM3 ENC

External capacitance decoupled → minimum noise: 560 e

From George lakovidis, poster at MPGD2017

### How you can support the SRS+VMM development

Send a student! (master/PhD, should stay at least for two months)

#### Good experience so far:

- Freddy Fuentes (Universidad Antonio Nariño, Bogotá) → will come again for 1.5 months ==

- Lara Bartels (University of Göttingen, CERN summer student)

- Manuel Guth (University of Freiburg, CERN summer student)

- Lucian Scharenberg (University of Bonn)

- Yan Huang (Central China Normal University)

#### Win-win-win situation:

You: Student brings back experience with operating the SRS + VMM setup

We+You: Student advances the project

Student: Stay at CERN

### How you can support the SRS+VMM development

Send a student! (master/PhD, should stay at least for two months)

#### Proposed projects:

- 1. Advance slow control: implement automated calibration → **CERN summer student?**

- → preferably stay of 6 months, should know C++, Qt, also work in the lab for testing

- 2. Implement useful triggered readout in firmware → currently ongoing by myself

- → at least 2 months with knowledge of FPGA programming ( > 3 month only basic knowledge)

- 3. Improve readout speed from VMM to Spartan-6 FPGA → will be done by Freddy

- → at least 2 months with knowledge of FPGA programming ( > 3 month only basic knowledge)

- 4. Understanding the VMM readout and documentation for users

- → no prior knowledge required

- 5. VMM hybrid characterisation for user references

- → some experience with working in the lab, using instruments

#### Outlook for the next months

## SRS + VMM project is advancing very well

- but still so much to do

- VMM3a test samples will arrive end of this month

- Hybrid PCBs are currently produces

- DVM Card final review ongoing

- VMM3a wafer production will start soon (3-5 wafers for us)

- SRS + VMM test system for first groups to be delivered

- Three SRS test beams

- Two neutron test beams for completing BrightnESS