#### Stave Emulator and Regulator Test

L. Gonella, D. Arutinov, M. Barbero, A. Eyring, F. Hügging, M. Karagounis, H. Krüger, N. Wermes Physikalisches Institut, Uni Bonn

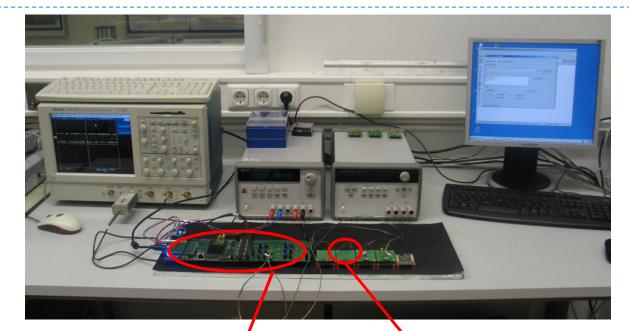

## Stave Emulator Test Bench

- The stave emulator is a test system which allows to evaluate system aspects and custom developed hardware for the ATLAS Pixel Detector for sLHC, such as

- physical layer data transmission: LVDS drivers/receivers, cables, connectors, ...

- data coding schemes: raw, 8B/10B, 64B/66B, …

- powering concepts: serial, dc-dc, switched cap, ...

- DCS concepts: voltage monitoring, control of bypass switch, reset, ...

- data management of the End-Of-Stave controller, ...

- ...

- It uses

- FPGAs to emulate the modules and the end-of-stave controller

- interconnection boards to provide support for different cable and connector options, LVDS transceiver chips, power supply options (parallel, DC/DC or SP), AC-coupling

- a DCS test board (COBOLT) developed in Wuppertal providing multi-channel ADC and GPIO to test DCS functionalities

$\rightarrow$  flexible and realistic test bench

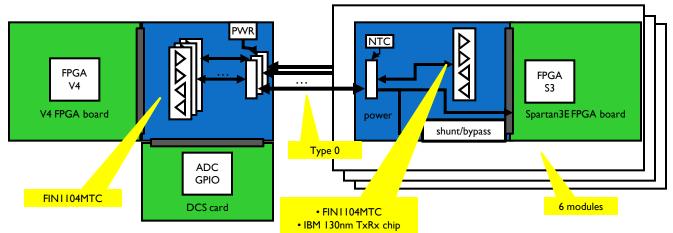

#### Stave Emulator

End-Of-Stave emulator unit

Module emulator unit

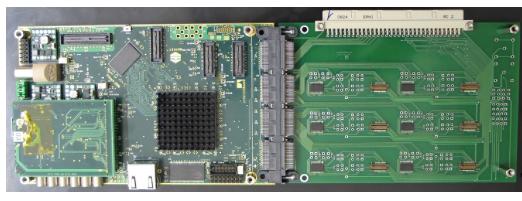

## Hardware

#### **FPGA** Boards

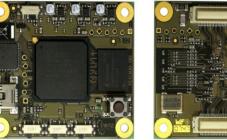

- Module  $\rightarrow$  Spartan 3E FPGA

- Commercial FPGA board (Trenz TEO300B)

- Spartan XC3S1600E, 64 Mbyte DDR RAM, 32 Mbit Flash, **USB** interface

- Approx. size of a 2x2 FE-I4 module

- End-Of-Stave Controller  $\rightarrow$  Virtex4 FPGA

- FPGA board developed in Bonn for read-out of DEPFET modules

- XILINX Virtex 4 LX40-1148, 288Mbit RLDRAM Should be able to handle >14.4Gbit/s, µC-based system monitor (ADM1062), USB 2.0 connector, 16Mbit async. SRAM, EUDET TLU connection, Multiple high speed connectors

- Interconnection boards

- Custom developed

- Tailor different test wishes (data transmission, powering option, ...)

- Define successive stave emulator versions

- Iterate the design of interconnection boards to add more functionalities and custom developed hardware when available

#### Spartan 3E board

VIRTEX4 board

# Firmware and Software

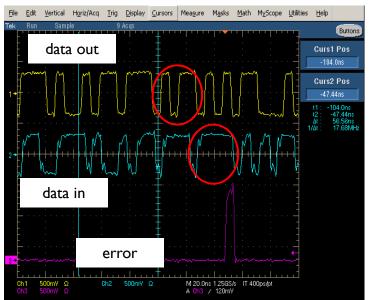

- Firmware for data transmission tests

- PRBS of different length, 8b10b encoded data

- FE-I4 code for Spartan3E

- Bit Error Rate firmware for Virtex4

- uses PRBS;

- clock frequency synthesized with Digital Clock Manager;

- compares data out with data in;

- delay adjustment between data out and data in done in 2 steps: coarse delay = 1 clk period, fine delay = 75ps

#### Software

Application developed with C++ and Qt (GUI) allows to download firmware on the FPGA, read/write data from/to FPGA

# Baseline Design

- "6 modules-stave"

- Connection EoS module using Type 0 cable

- Powering

- parallel

- serial using commercial shunt regulator

- commercial bypass transistor on modules to test protection option

- DC-coupled data transmission with different LVDS transceiver chips

- on End-Of-Stave side: commercial FIN1104MTC transceiver chip

- on module side: commercial FIN1104MTC or IBM 130nm transceiver chip (i.e. FE-I4 LVDS TX and RX)

- NTC to measure module temperature

# Tests with Baseline Design

- Bit Error Rate Tests

- study the performance of the LVDS TX and RX for FE-I4

- Comparison with commercial transceiver chip

- ▶ V<sub>dd</sub> = 1.2-1.5V

- ▶ I<sub>bias</sub> higher than nominal

- parallel powering, DC coupled data transmission, PRBS8-16-24, 160Mbps

- → IBM 130nm transceiver chip runs error free with PRBS24 at 160Mbps with  $V_{dd} = 1.2V(38e^{12} bits$  transmitted)

#### Tests with COBOLT

- Serial powering chain

- Some DCS functionalities have been successfully tested

- module temperature measuring with NTC

- control of bypass transistor

- monitoring of module voltage through bypass control line

|    |                   | Nominal                      | 1.2∨   | I.5V   |

|----|-------------------|------------------------------|--------|--------|

| RX | l <sub>bn</sub>   | -35uA                        | -100uA | -150uA |

|    | I <sub>bp</sub>   | 35uA                         | 60uA   | 90uA   |

| ТХ | I <sub>bp</sub>   | 60uA                         | 60uA   | 90uA   |

|    | U <sub>bias</sub> | 600mV (1.2V)<br>750mV (1.5V) | 600mV  | 750mV  |

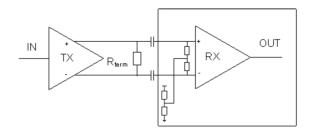

# Next Stave Emulator Version

- Second version of interconnection board for module emulator unit available

- more custom-developed hardware

- IBM 130nm LVDS transceiver chip

- External biasing circuitry for RX inputs ( $\rightarrow$  AC-coupled data transmission)

- IBM 130nm LVDS tri-state driver

- ShuntLDO regulator

- Test plan

- AC-coupling at TX/RX level with FEI4 LVDS transceiver chip

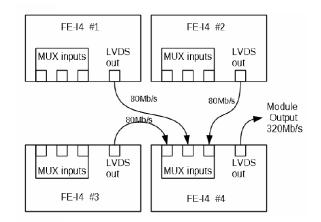

- Multiplexing of data out of different FEs

- w/ tri-state driver

- FEs in master-slave configuration

- Test of ShuntLDO regulator in a real serially powered system

- Test of ShuntLDO pure LDO regulator operation with shunt capability switched-off

possible RX inputs self-biasing integrated circuit for FE-I4

Goal: Set up a serially powered stave with AC-coupled data transmission and FE data output multiplexing, using real FE-I4 components

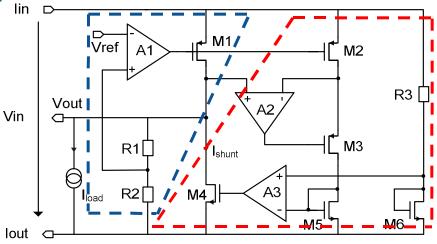

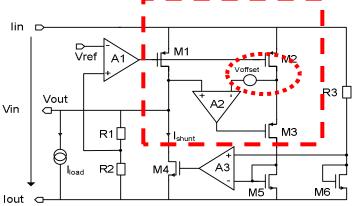

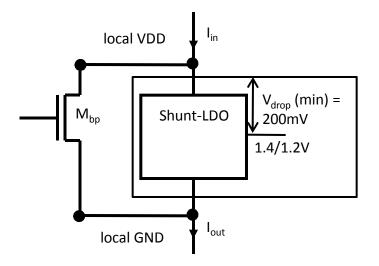

# ShuntLDO: Working Principle

combination of a LDO and a shunt transistor

- R<sub>slope</sub> of the shunt is replaced by the LDO power transistor

- shunt transistor is part of the LDO load

- shunt regulation circuitry ensures constant

I<sub>load</sub>

- $I_{ref}$  set by R3, depends on  $V_{in}$  ( $\rightarrow$   $I_{in}$ )

- I<sub>MI</sub> mirrored and drained in M5

- I<sub>MI</sub> and I<sub>ref</sub> compared in A3

- M4 shunts the current not drawn by the load

- LDO regulation loop sets constant output voltageV<sub>out</sub>

- LDO compensates output potential difference

simplified schematics

# ShuntLDO : Features

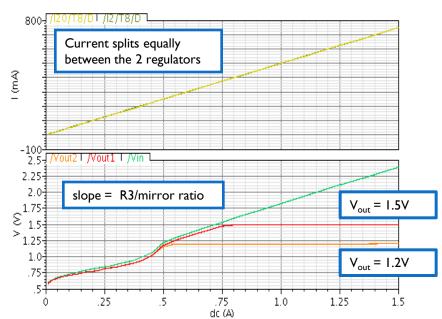

- ShuntLDO regulators having different output voltages can be placed in parallel without any problem regarding mismatch & shunt current distribution

- resistor R3 mismatch will lead to some variation of shunt current (10-20%) but will not destroy the regulator

- ShuntLDO can cope with an increased supply current if one FE-I4 does not contribute to the regulation e.g. disconnected wire bond

- ► I<sub>shunt</sub> will increase

- can be used as an ordinary LDO when shunt is disabled

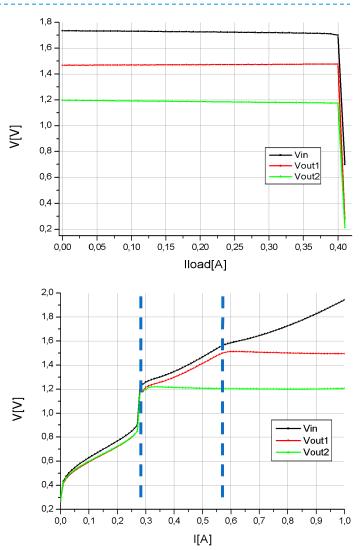

Parallel placed regulators with different output voltages - simulation results -

DC Response

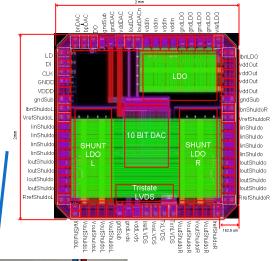

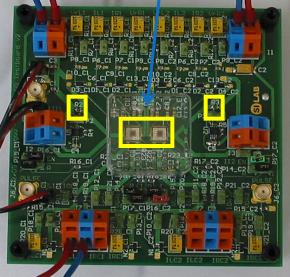

# ShuntLDO : Prototypes and Test System

- 2 prototypes submitted and tested

- September 2008, March 2009

- $V_{out} = 1.2-1.5V$ ,  $V_{dropout}MIN = 200mV$ ,  $I_{shunt}MAX = 0.5A$ ,  $R_{in} = 4\Omega$ ,  $R_{out} = 30m\Omega$

- test setup

- two ShuntLDO regulators connected in parallel on the PCB

- biasing & reference voltage is provided externally

- input & load current is provided by programmable Keithley sourcemeter

- input & output voltages are measured automatically using a Labview based system

- shunt current is measured by 10mΩ series resistors and instrumentation opamp

# 2 ShuntLDO in Parallel

- Load Regulation Measurement

- I.5(I.2)V output sees fix I<sub>load</sub> = 0.4A

- I.2(I.5)V output has variable I<sub>load</sub>

- V<sub>in</sub> and V<sub>out</sub> collapse when the overall I<sub>load</sub> reaches I<sub>supply</sub> (= 0.8A)

- effective output impedance R = 60mΩ (incl. wire bonds and PCB traces)

- Generation of different V<sub>out</sub>

- V<sub>out</sub> settles at different potentials

- V<sub>out1</sub> and V<sub>out2</sub> slightly decrease with rising input current (V drop on ground rails leads to smaller effective reference voltages)

- non constant slope of V<sub>in</sub>

- $R_{in} \approx 2\Omega$  (after saturation)

L. Gonella - SLHC-PP Annual Meeting - Feb. 2010

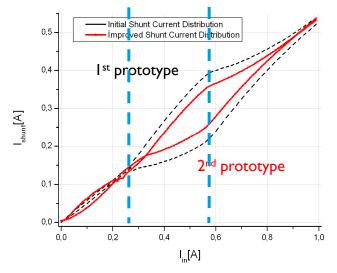

# Shunt Current Distribution at Start-Up

- unbalanced I<sub>shunt</sub> distribution at start-up

- more I<sub>shunt</sub> flows to the regulator which saturates first (i.e. to the regulator with lower V<sub>out</sub>)

- however I<sub>shunt</sub>MAX is not exceed

- improvement of shunt distribution as soon as both transistors are saturated

- non constant slope of V<sub>in</sub> closely related to

I<sub>shunt</sub> distribution

- bad mirroring accuracy for non saturated transistors due to offset at the input of A2

- wrong current is compared to the reference

- hypothesis confirmed by simulations and second vin prototype

- scaling of input transistor of A2 by factor 4 halves the unbalance

#### 2 SHULDOs in parallel with different $V_{out}$

## Shunt Current Distribution

- no problem at start-up if the 2 ShuntLDOs generate the same V<sub>out</sub>

- they saturate at the same time

2 ShuntLDOs in parallel with same V<sub>out</sub> at start-up

- if V<sub>out</sub> is changed with both regulators being saturated the shunt current changes of about 1.4%

- → Unbalanced I<sub>shunt</sub> at start-up can be avoided completely by choosing the same  $V_{out}$  at start-up and setting different  $V_{out}$  afterwards

0,65 -0,60 0,550 0.55 0.548 0,50 -0,546 0,45 -0,544 0,40 0,542 Vout I fixed at 1.2V [shunt[A] 0.35 0,540 2 Vout2 varies (1.2V - 1.5V)0,30 Ishunt1 0,538 0,25 Ishunt2 0,536 0,20 0,534 0,15 0,10 -0,532 0.05 0,530 0,00 1.20 1,25 1,30 1,35 1,40 1,45 1,50 1.55 0,0 0,1 0,2 0,3 0,4 0,5 0,6 0,7 0,8 0,9 1,0 Vout2 [V] Ishunt[A]

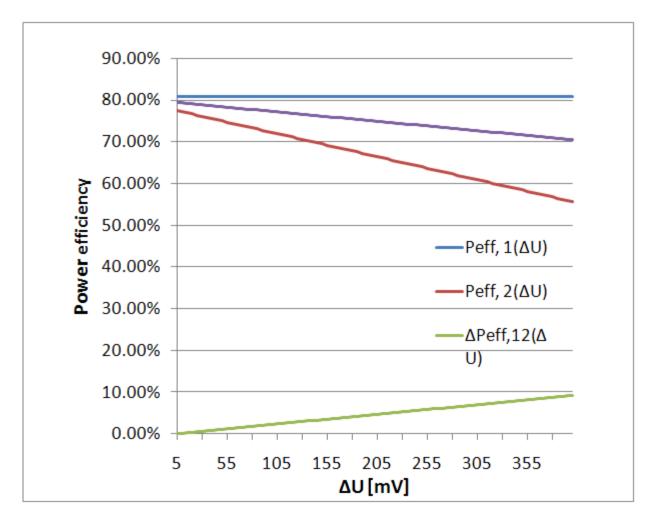

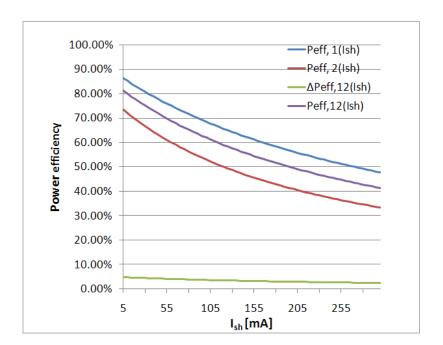

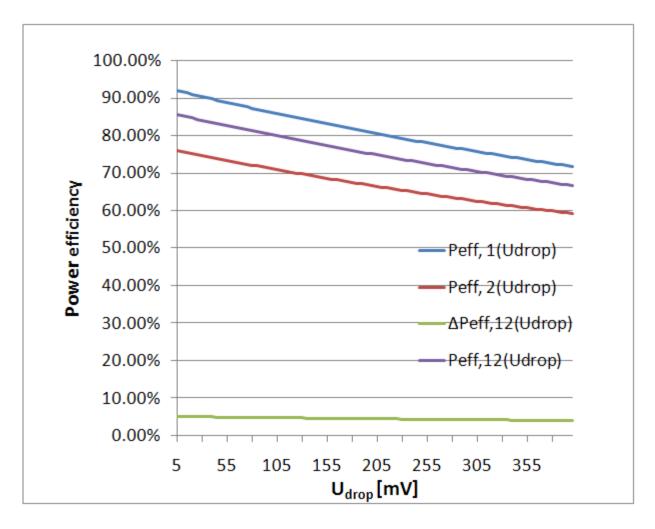

# ShuntLDO Efficiency

- Crucial point for SP is the power efficiency of the power converter

- 3 possible sources of inefficiency for the ShuntLDO

- Dropout voltage V<sub>drop</sub>

- Shunt current I<sub>shunt</sub>

- $\Delta V$  between the 2 V<sub>out</sub> needed by the FE

#### Calculation for ATLAS Pixels

|                        | nominal v     | worst case    | best          |

|------------------------|---------------|---------------|---------------|

| V <sub>out1</sub> [V]  | 1.4           | 1.4           | 1.4           |

| V <sub>out2</sub> [V]  | 1.2           | 1.2           | 1.2           |

| I <sub>out1</sub> [A]  | 0.36          | 0.4           | 0.36          |

| I <sub>out2</sub> [A]  | 0.24          | 0.27          | 0.24          |

| V <sub>drop</sub> [V]  | 0.2           | 0.2           | 0.1           |

| I <sub>shunt</sub> [A] | 0.03          | 0.05          | 0.01          |

| ∆U [V]                 | 0.2           | 0.3           | 0.2           |

| I <sub>тот</sub> [А]   | 0.6           | 0.67          | 0.6           |

| P_eff, 1               | 80.77%        | 77.78%        | <b>90.81%</b> |

| P_eff, 2               | <b>66.67%</b> | <b>59.56%</b> | <b>76.80%</b> |

| P_eff, 1-2             | 79.55%        | 76.14%        | 90.32%        |

| ΔP_eff,1-2             | 4.55%         | 6.57%         | 5.16%         |

| P_eff,1-2g             | 75.00%        | 69.56%        | 85.16%        |

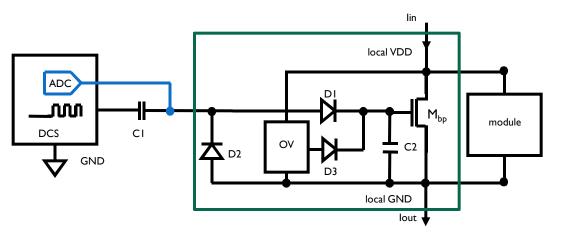

# **Module Protection Chip**

- I 30nm CMOS technology

- Bypass transistor

- AC-coupled slow control line

- $\blacktriangleright$  can be used to monitor  $V_{mod}$  when idle

- Independent over voltage protection circuitry

- Specs for 4-chip FE-I4 module<sup>(\*)</sup>

- I<sub>nom</sub> = 2.4A, I<sub>MAX</sub> = 3.5A

- AC-signal frequency = 100k 1MHz

- AC-signal amplitude = V<sub>gs</sub> bypass

- OV protection threshold:  $V_{\text{thMIN}} = 2V V_{\text{thMAX}} = 2.5V$

- OV protection time response = 100ns

(\*) preliminary

#### **Bypass Transistor**

- $I = 3.5A, V \ge 1.6V \pmod{2.5V}$

- $\rightarrow$  DG NMOS

- Radiation hardness

- ELT to cut leakage current path

- Positive  $V_{th}$  shift at TID  $\geq$  1 Mrad

- Account for  $\Delta V_{th} = 200 \text{mV}$  in simulations

- Operational temperature

- Not yet defined, will depend on the sensor

- Simulations with T =  $(-27 \div +27)^{\circ}C$

- Low power consumption when on

- Process Corners

$\rightarrow$  W = 48mm, L = 0.24 $\mu$ m

- Power consumption (worst case)

- Bypass on → 335.1mW

- Bypass off  $\rightarrow 25\mu W$

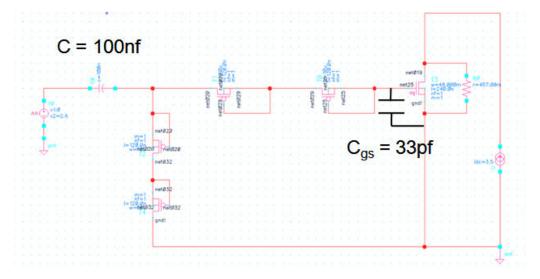

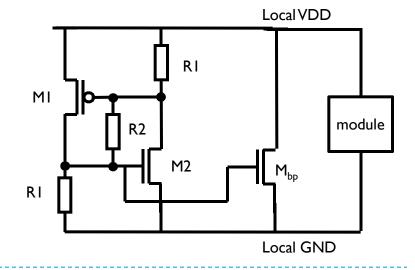

# **Control Line**

#### Rectifier

- In a diode connected MOSFET  $V_{ds} = V_{gs} \approx V_{th}$

- To increase the power conversion efficiency

- ▶  $V_{sb} < 0$  when diode is forward biased  $\rightarrow V_{th}$  smaller  $\rightarrow V_{ds}$  smaller

- ▶  $V_{sb} > 0$  when diode is reversed biased  $\rightarrow V_{th}$  higher  $\rightarrow$  smaller leakage current

$\rightarrow$  use PMOS or triple well NMOS (allow to connect bulk in the "forward direction")

#### Thin oxide transistor

- W = 10µm for radiation hardness

- > 2 PMOS in series to avoid gate oxide breakdown (AC-signal amplitude > 2.5V)

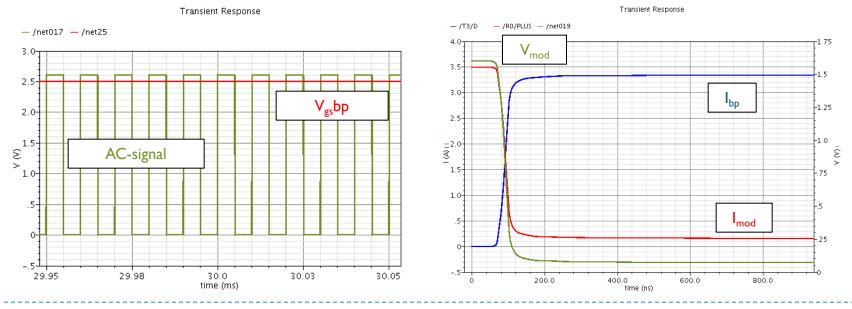

### **Control Line: Simulation Results**

- AC-signal: 2.6V, f = 100k 1MHz

- V<sub>gs</sub> bypass: 2.5V

- ►  $V_{mod}$ : I.6V  $\rightarrow$  ~60mV

- ►  $I_{mod}$ : 3.5A  $\rightarrow$  ~100mA

- $\rightarrow$  Control from DCS works fine

L. Gonella - SLHC-PP Annual Meeting - Feb. 2010

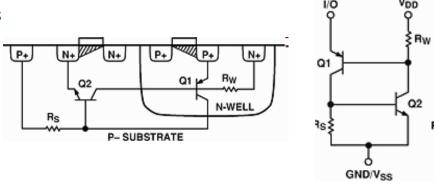

## **Over-Voltage Protection**

- Silicon Controlled Rectifier

- Parasitic elements (BJTs) in CMOS technologies (inverter in IO pads)

- Latch-up condition: I/O voltage  $(U_E^{QI}) > VDD$

- ▶ QI begins to conduct  $\rightarrow$  Q2 switches on  $\rightarrow$  QI draws even more current

- Shorts the supply rails when triggered

- That is exactly what we want!

- Use MOSFETS instead of parasitic BJTs for better control of operation parameters

- Trigger threshold defined by R2/R1

- Want to draw high currents

- RI small

- or use additional 'power' NMOS  $\rightarrow$  bypass

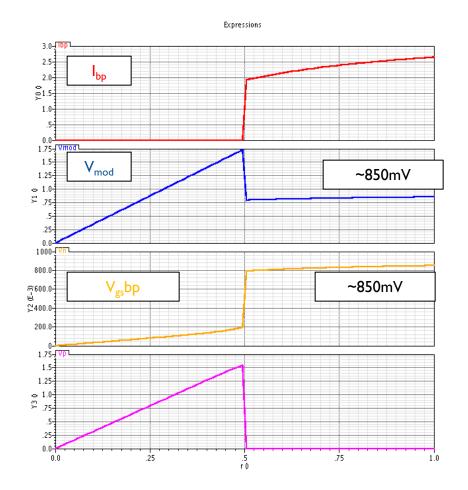

# SCR: Simulation Results

- Sweep of  $R_{mod} \rightarrow V_{mod}$  increases,  $I_{mod}$  constant

- The voltage across the module is effectively clamped down when the SCR activates, however

- ►  $V_{ds}bp = V_{gs}bp \rightarrow impossible to get V_{mod} = 100mV and V_{gs}bp = 2.5V$

- ►  $V_{mod} = 850 \text{mV} \& I_{bp} \approx 3A \rightarrow \text{too high}$ power density

- A SCR is not the optimal solution for our needs and a different OV protection scheme has to be studied

# Summary

- A stave emulator has been developed which allows study of system aspects related to serial powering

- A baseline design has been set up and the FE-I4 LVDS transceiver has been tested, as well as some DCS functionalities

- A serial powered emulator stave is under development to study ShuntLDO performance and AC-coupled data transmission

- Characterization of the ShuntLDO has been performed on single devices, with nominal current and voltage values

- Results show that the ShuntLDO performs according to specifications with a nominal power efficiency of 75%

- Problems with shunt current distribution have been understood and corrected in next version

- Work is ongoing on the Module Protection Chip

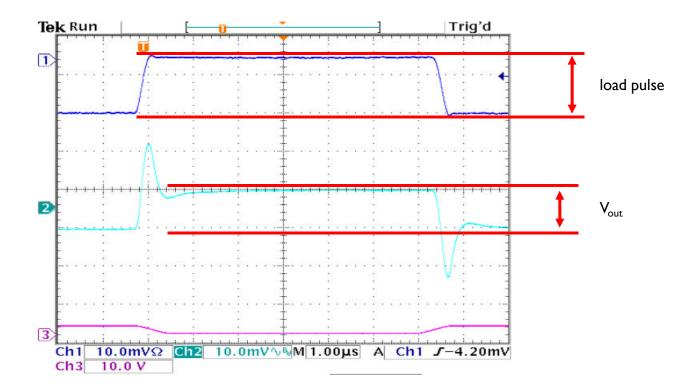

# SHULDO: Load Transient Behavior

- I<sub>load</sub> pulse of I50mA (I5mV measured across I00mΩ)

- IOmV output voltage change

### SHULDO Efficiency

### SHULDO Efficiency