### **Technological blocks for 40 MHz readout**

- Implementation

- Critical issues

- Board status

- Foreseen schedule

### Frederic Marin & Jean-Pierre Cachemiche

## Implementation

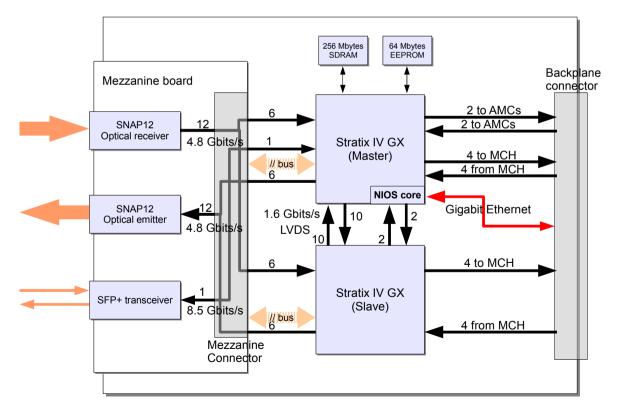

- Main board : 2 FPGAs Stratix IV GX

- Mezzanine board :

- 1 SNAP12 receiver : 12 x 6.25 Gbits/s  $\rightarrow$  emulation of GBT reception

- 1 SNAP12 transmitter : 12 x 6.25 Gbits/s  $\rightarrow$  emulation of emission toward GBT

- 1 transceiver 8.5 Gbits/s  $\rightarrow$  emulation of farm interface

- ➡ availability of Stratix IV GT at 10-11 Gbits/s on 2010

### **Mechanics**

## **Critical issues**

### Power supplies for FPGAs :

25 power supplies required !!

#### Power supplies:

- Vcc: 0.9V core supply voltage VCCPT · 1.5V power supply for programmable technology configuration pins power supply VCCPGM: 3.0 V VCCAUX: 2.5V Auxiliary supply for the programmable power technology 2.5V Battery back up power supply (non utilisé dans ce design) V<sub>CCBat</sub>: I/O pre-driver (for 3.0V and 3.3V) power supply VCCPD: 3.0V 2.5V I/O pre-driver (For lower than 2.5V and equal) power supply VCCPD : - Vccio : 1.8V I/O power supply 2.5V - Vccio : I/O power supply 3.0V Vccio : I/O power supply - Vcc\_clkin : 2.5V differential clock input power supply - VCCD PLL : 0.9V PLL digital power supply - VCCA PLL : 2.5V PLL analog power supply – Vccal: 3.0V Transceiver high voltage power (left side) – Vccar: 3.0V Transceiver high voltage power (right side) - VCCHIP L : 0.9V Transceiver HIP digital power (left side) VCCHIP R : 0.9V Transceiver HIP digital power (right side) 1.1V Receiver power (left side) - VCCRL: - Vccr r : 1.1V Receiver power (right side) 1.1V Transmitter power (left side) Vcct l : 1.1V Transmitter power (right side) - VCCT R :

- V<sub>CCL\_GXBLn</sub>: 1.1V Transceiver clock power (left side)

- V<sub>CCL\_GXBRn</sub>: 1.1V Transceiver clock power (right side)

- V<sub>CCH\_GXBLn</sub>: 1.5V Transmitter output buffer power (left side)

- VCCH\_GXBRn : 1.5V Transmitter output buffer power (right side)

#### Decoupling scheme for FPGAs :

- Estimated consumption full charge = 15A for 0.9V

- 200 decoupling capacitors required !

- Only 75% of capacitors implemented

- Not a problem for the prototype : limited design

- Tests at full charge will be made to validate our decoupling scheme

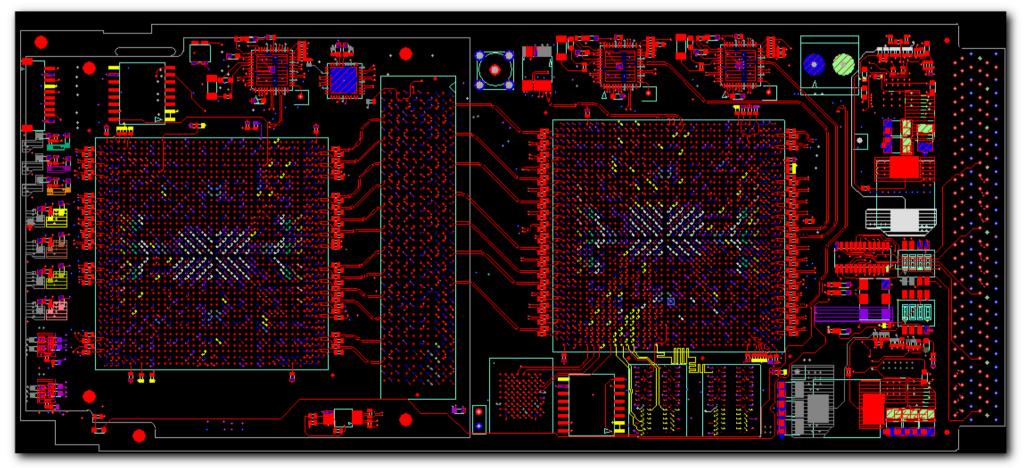

# **Board Layout**

- 684 components, 2 FPGAs 1500 pins

- PCB dimension 73.5 x 181.5 mm

Prototype board top layer view

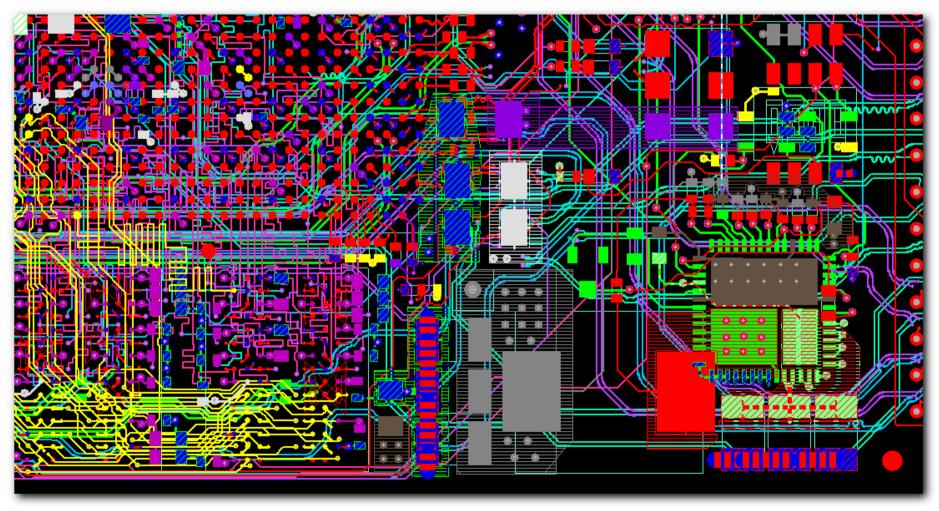

# **Board routing**

Board and its mezzanine are routed: 14 layers, 900 signals, sequential PCB (buried and laser vias)

### **Foreseen schedule**

- November : PCB manufacturing

- December/January : **cabling**

- Start debug : mid January

- First measurements and results : Early March

# Conclusion

- This board will allow us to test :

- GBT protocol compliance at 4.8 Gbits/s

- Signal integrity on copper through mezzanine connector up to 8.5 Gbits/s in and out

- Density issues for implementing large FPGAs

- With this board we are able to validate all technologies required by the 40 MHz read-out board

- By the end of 2010 we will develop a prototype of the 40 MHz board with:

- A 10 Gbits/s implementation

- A form factor suitable for LHCb