#### Lessons learned from GE1/1

G. De Lentdecker (ULB)

#### Content

- GE1/1 achievements

- ➤ GE1/1, GE2/1 & ME0 common points

- Lessons learned

- VFAT3 hybrid design

- GEB design

- > OH design

- Mechanics, power, ...

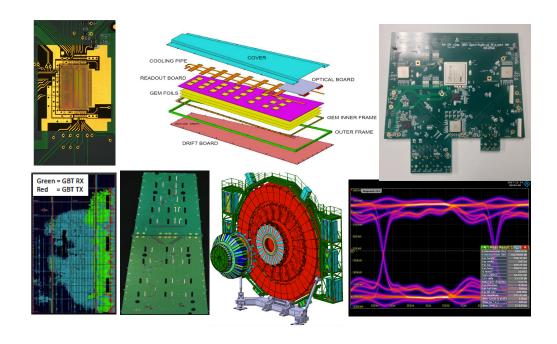

# GE1/1 prototyping steps

Prototype 2a (2015):

Full size GEB (one piece)

VFAT2

Opto-hybrid with Virtex-6, emulating GBT protocol

Back-end: GLIB board **Applications: Test Beam**

Prototype 2b (2016):

Full size GEB (one piece)

VFAT2

Opto-hybrid with Virtex-6 + 1 GBT + 1 SCA, VTTx and VTRx

Back-end: GLIB and CTP7 boards

Applications: Slice Test

Full size GEB (two pieces)

VFAT3a

Opto-hybrid with Virtex-6 + 3 GBT + 1 SCA, VTTx and VTRx

Back-end: CTP7 boards

#### Prototype 3b (Q1 2018):

Full size GEB (two pieces)

VFAT3b

Opto-hybrid with Virtex-6 + 3 GBT + 1 SCA, VTTx and VTRx

Back-end: CTP7 boards

Applications: LS2

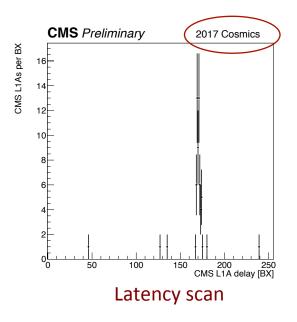

# Achievements: GEMs in P5

- > 5 x v2 super-chambers since January 2017

- VFAT2, Opto-Hybrid v2b (1 GBT+ 1 SCA)

- In global runs since Nov. 2017.

- 1 x v3 super-chamber since February 2018

- Replacing one v2 super-chamber (Multi-channel HV)

- VFAT3b, Opto-Hybrid v3 (3 GBT+ 1 SCA), FEAST, ...

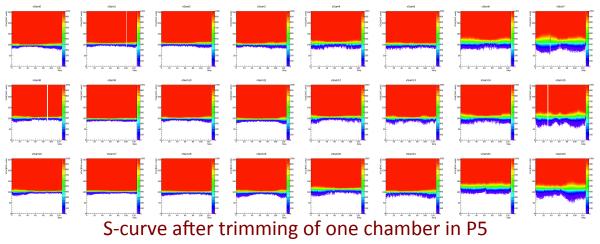

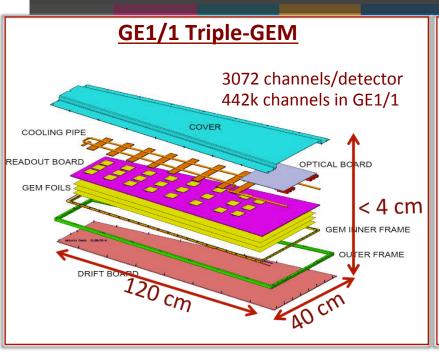

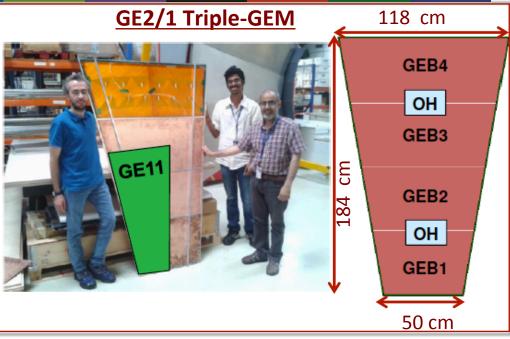

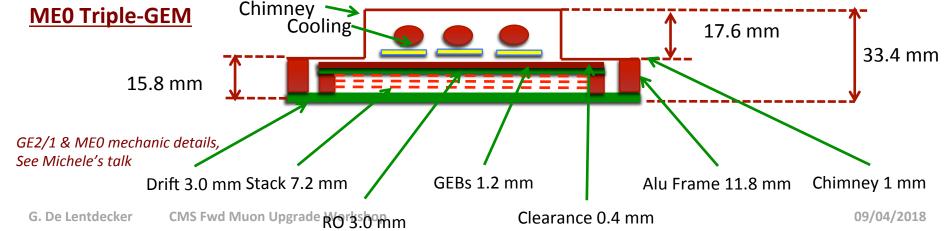

# CMS Triple-GEMs

## GE2/1 and MEo electronics requirements

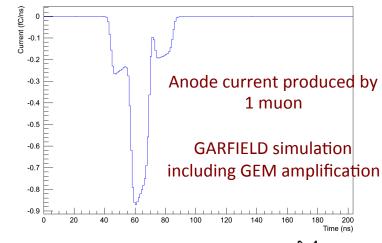

- CMS Triple-GEM

- ➤ signal length: ~60 ns

- detector capacitance > 30 ? pF

- charge range (MIP): 4-110 fC

More details on capa. & charge in Marcus' talk tomorrow

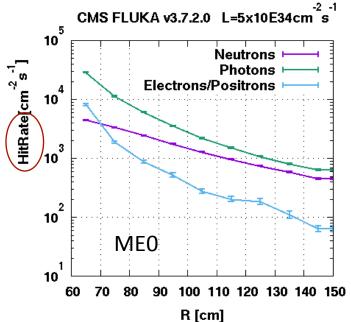

- Expected particle rate

- GE21: similar to GE11 (a few kHz/cm²)

- ME0: up to ~5MHz/cm² (one order higher than GE11)

- CMS Level-1 latency: 12.5 μs

- CMS Level-1 Accept rate: 750 kHz

- Total irradiation dose:

- > 5 krad 1 Mrad (10 krad in GE11)

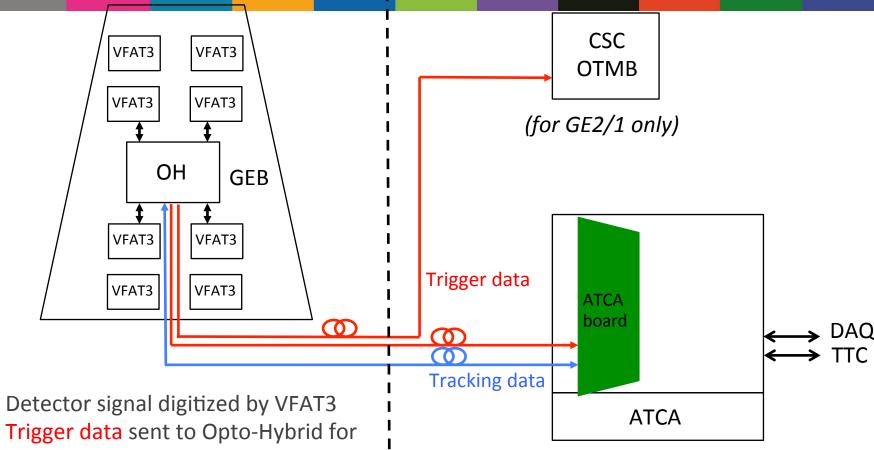

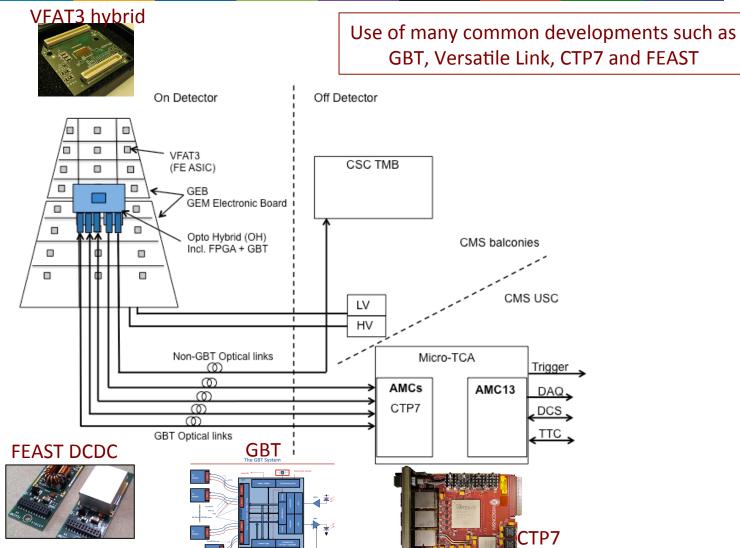

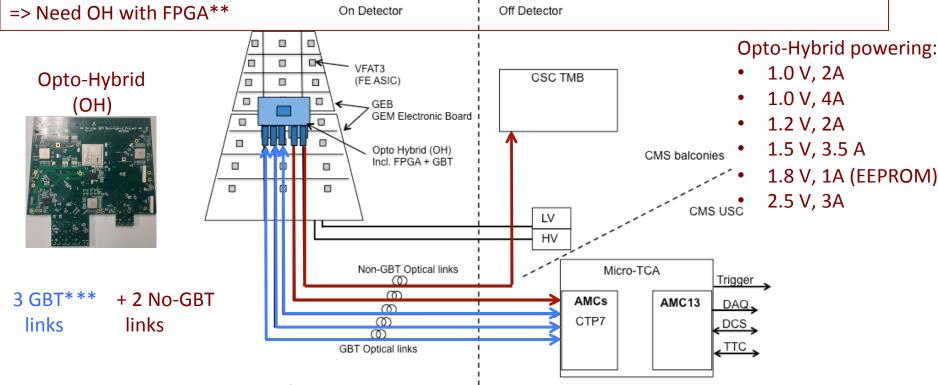

## Overview of the GEM electronics system

- cluster finding (+1 link to OTMB in **GE21**)

- Tracking data, slow ctrl and clock are handled by LpGBT

- Running local trigger

board

Event building and sending to DAQ

Baseline plan based on CTP7-like ATCA

## GE1/1 Electronics overview

Opto-Hybrid (OH)

G. De Lentdecker

**CMS Fwd Muon Upgrade Workshop**

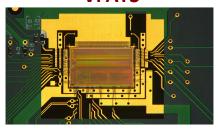

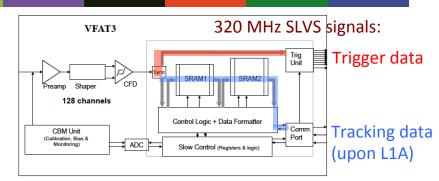

# VFAT3 & GE1/1 VFAT3 hybrid

#### VFAT3

#### Some features:

- Binary chip

- 320 MHz

- L1 latency: up to 12 μs

- Slow control: ePort, **GBT** compatible

- Trigger data: 1bit= OR of 2 strips (+DDR option)

#### **Lesson learned:**

Fabrication

Wafer

Processing

Hybrid PCB

VFAT3 Hybrid Assembly

This procedure is complicated and difficult to do. At the limit of industrial capabilities.

Preference is to package VFAT3 for future use.

VFAT3 details, see Paul's talk

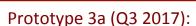

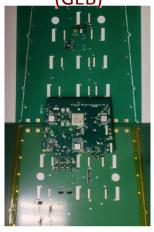

## The GEB board

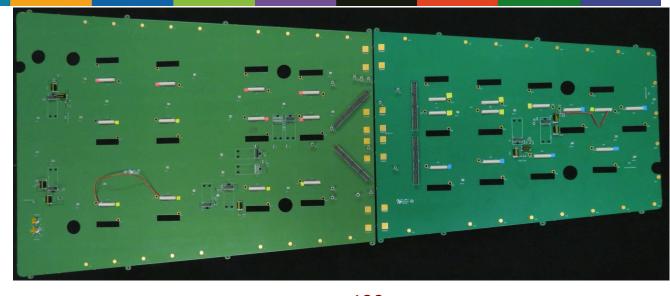

#### The GEB

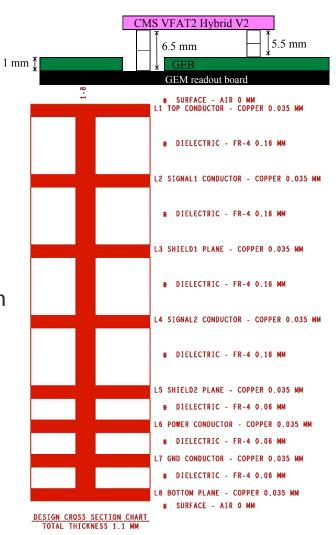

- 8-layer PCB

- Carry signals between VFAT3s and OH

- Carry power from FEASTs to VFAT3 and OH

120 cm

On paper it looks like just a passive PCB carrying signals, providing power and ground but it is much more complex:

- large number of connections (~500 differential signals, 10 FEASTs, AGND & DGND to every VFAT3)

- tight mechanical constraints

- limited thickness ~1mm -> limited number of layers

- Flatness

- Many connectors -> mechanical stress

### GEB lesson learned

- Manufacturing >1m long PCB

- At the limit of industrial capabilities

- Very few companies can manufacture 120 cm long PCBs

- Expensive, yield issues

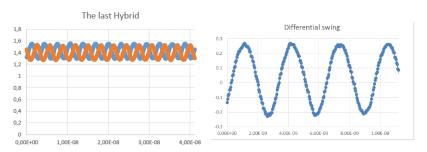

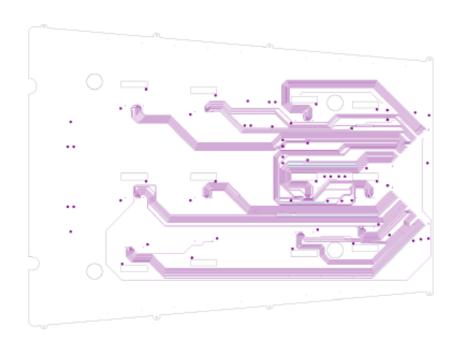

- Concerns about signal integrity

- Reminder, we use 320 MHz SLVS signals

- ➤ An example of a clock signal with 320 LVDS:

Note: we did not investigate further but rather design a split GEB for GE1/1

1 piece GEB (Slice Test)

### GEB lesson learned

- GEB thickness limited to ~1mm

- Limited number of layers in PCB

- > 1 power plane

- > 1 GND plane

- 2 signal layers

- > 1 shield layer

- This shield layer between GEB signal lines and Read Out Board (ROB) was added from our Slice Test experience

More on Grounding in Cameron & Brian's talk tomorrow

Matching signal lines lengths for VFAT3s synchronization

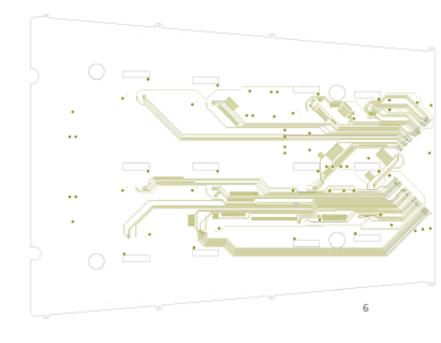

# GEB signal layers

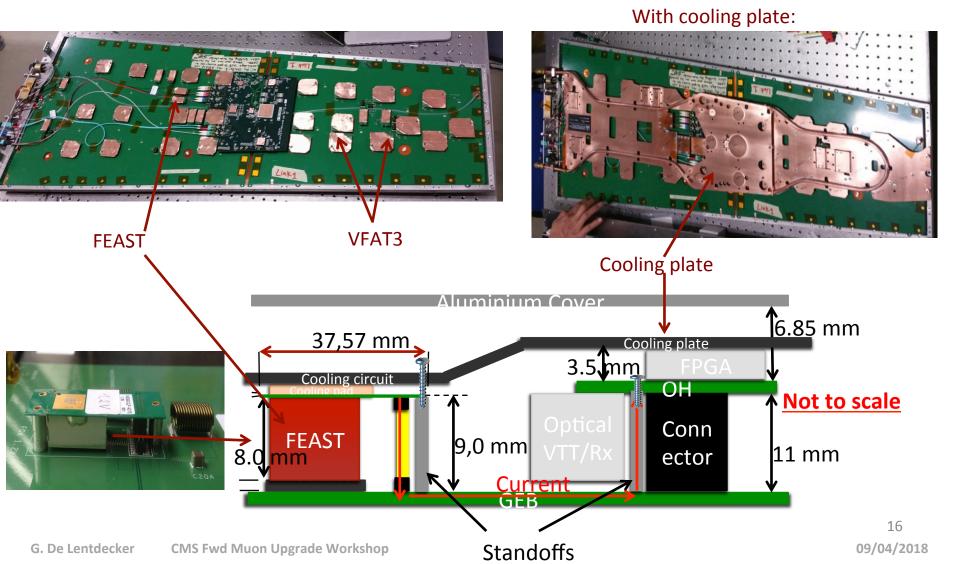

#### Power

- All the FE components are powered from FEASTs

- 4 x 1.2 V for 24 VFATs

- ➢ 6 for OH

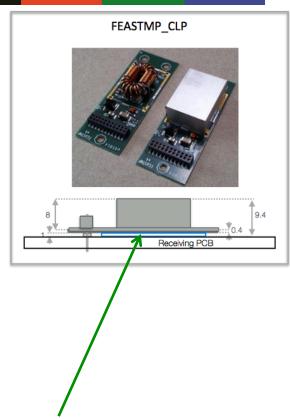

- Some key features of the FEASTS:

- Input voltage: 5 to 12 V

- Need an Enable Voltage (3 V)

- Limited output current: 4A

- Limited output power: 10 W

- Maximum temperature: ~75°C

- Beyond, FEAST shutdowns by itself

- Need good contact with cooling; cooling from the bottom of the PCB

- ➢ In GE1/1, FEAST are placed up-side down (see next page)

- If you want to modify the PCB (to enlarge the holes or whatever) it is at your charge

# Opto-Hybrid (OH)

The Trigger data (FastOR) from 24 VFAT3s represent 61.44 Gbps => requires on-detector procesing\* In addition these data have to be transmitted to existing CSC Trigger Mother Board (oTMB) which is not compatible with GBT speed.

\*To relax time adjustment in FPGA firmware, track length should be adjusted on GEB

\*\*\* 1GBT can handle up to 10 VFAT3 \*\* Chosen FPGA (Virtex-6) is the same as used on CSC ME1/1 chambers

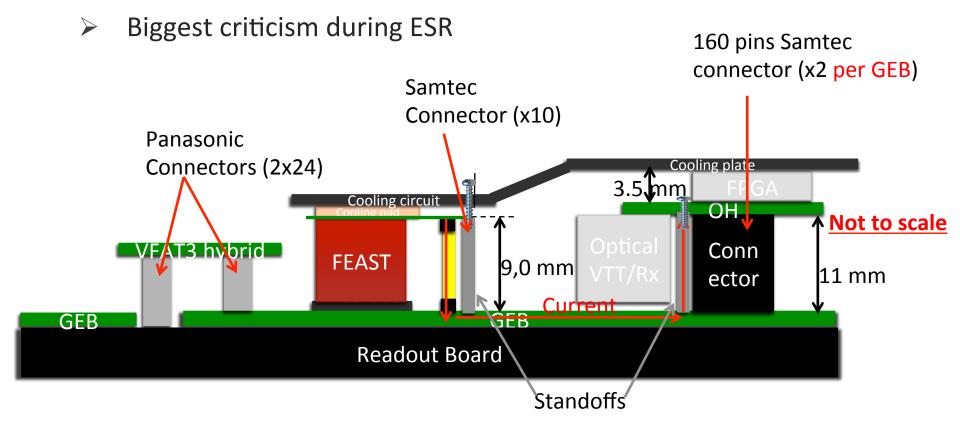

### Mechanics

### Mechanics

- Many screws (90)

- Some very small (M2 for FEAST)

- Standoffs are fragile

- Difficult to solder

- Some connected to GEB GND

- Reinforced with Araldite

#### Mechanics

(Too) many connectors

### Other lessons

- Choose common design software (cadence/altium)

- > To allow other designers to review the designs

- Use repository and versioning to store and share design files

- Keep track of changes

### Conclusions

- Although GE2/1 and ME0 baseline is

- LpGBT

- Packaged VFAT3

- FlexPCB

#### first GE2/1 prototypes will very much look like GE1/1 (in much larger)

4 GEBs with many mechanical constraints and many interfaces will require several prototype iterations

|       | date        | milestone description                                                                    | status   |

|-------|-------------|------------------------------------------------------------------------------------------|----------|

| GE2/1 | 21 Mar 2017 | Key detector system design parameters are defined based on performance requirements      | achieved |

|       | 19 Jun 2017 | On-chamber electronics preliminary design completed and interfaces defined               | achieved |

|       | 12 Mar 2018 | Off-chamber electronics preliminary design completed and interfaces defined              | on track |

|       | 1 May 2018  | A full size GE2/1 prototype with partially instrumented readout built and tested         | on track |

|       | 8 May 2018  | Det. design parameter optimization completed, final design selected for demonstrator     | on track |

|       | 1 Jun 2018  | On-chamber electronics prototypes engineering design complete                            | on track |

|       | 3 Aug 2018  | → GE2/1 PRR for the On-Detector Services                                                 | on track |

|       | 18 Oct 2018 | On-chamber electronics prototype electronics manufacturing and testing is complete       | on track |

|       | 13 Nov 2018 | → GE2/1 PRR for the Foil Production                                                      | on track |

| MEO   | 21 Mar 2017 | Key detector design parameters are defined based on performance requirements             | achieved |

|       | 11 Jun 2017 | Irradiation studies, assessment of performance/longevity with small prototypes completed | achieved |

|       | 25 Jul 2017 | On-det. & off-det. electronics preliminary design complete and interfaces defined        | achieved |

|       | 18 Dec 2018 | Chamber (stack) prototype mechanical design completed                                    | on track |

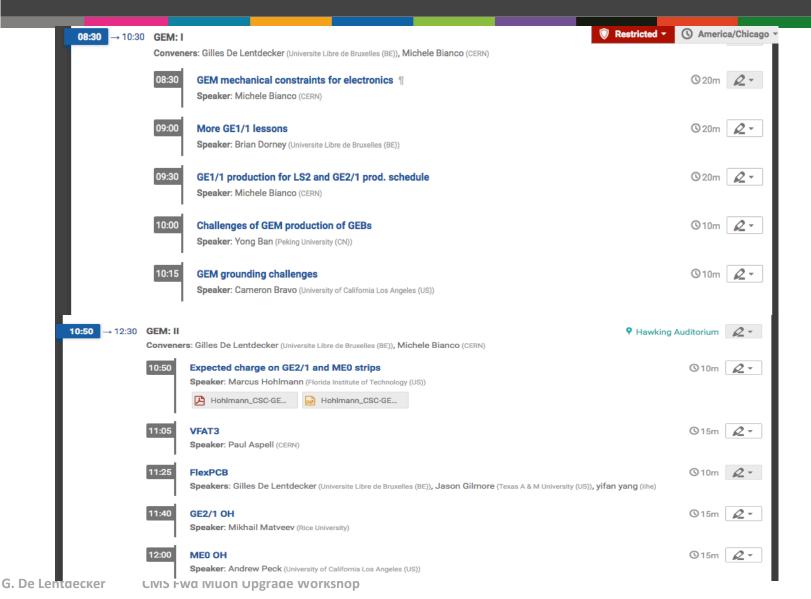

### More details tomorrow

# GE2/1 Timeline

- GE2/1 chambers are foreseen to be installed into CMS during the EYTS 2022 and 2023 (one disk per year)

- Module pre-production is expected to start at the end of GE1/1 chamber production, end 2018, right after the EDR

- First GE2/1 electronics prototype (OH + GEB): Q2 2018

- Q3-Q4 2018: design second version (design & tests)

- Q1 2019: Validation with demonstrator

- > 2019-2020:

- final design

- test & pre-prod.

- > prod

### **MEo Timeline**

- ME0 chambers are foreseen to be installed in to CMS during LS3 (2024-2025)

- Module pre-production is expected to start beginning 2021

- First ME0 electronics prototype (OH + GEB) by end of 2019

- 2020: second version (design & tests)

- > 2021:

- Q1: final design

- Q2-Q3: test & pre-prod.

- Q4: prod