### **Calibrations of PSD NA61**

#### Calibration program for main PSD NA61, April - May 2018:

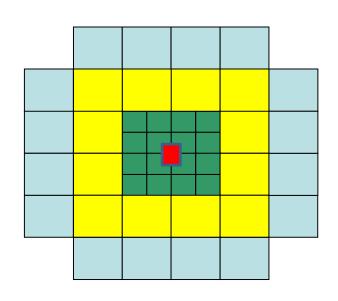

- muon + proton calibration scan of all 45 modules (16 small (10x10 cm<sup>2</sup>), 28 large (20x20 cm<sup>2</sup>) and 1 short (10x10 cm<sup>2</sup>))

- muon + proton calibration scan at reduced HV on SiPMs in small modules (for PbPb 2018)

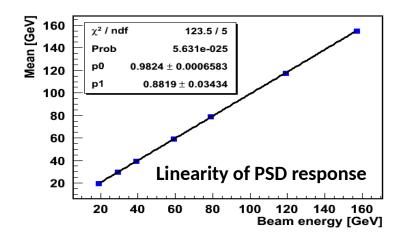

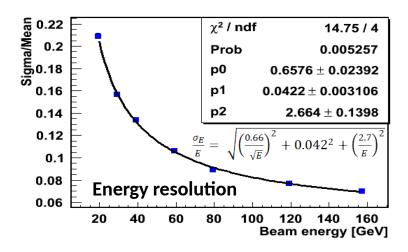

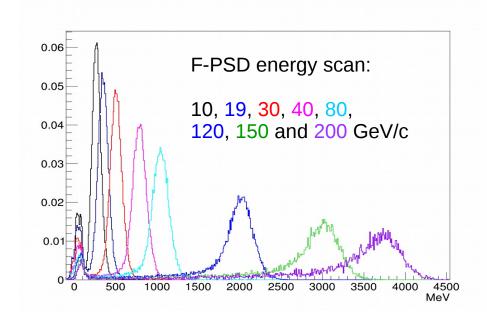

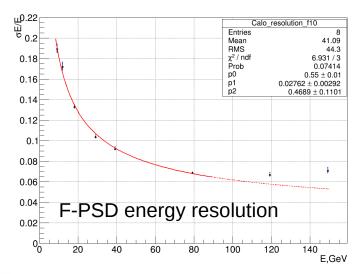

- energy scan of calorimeter response 10, 19, 30, 40, 80, 120, 150 and 200 GeV/c beams

- LED calibration of one large module for light yield estimation

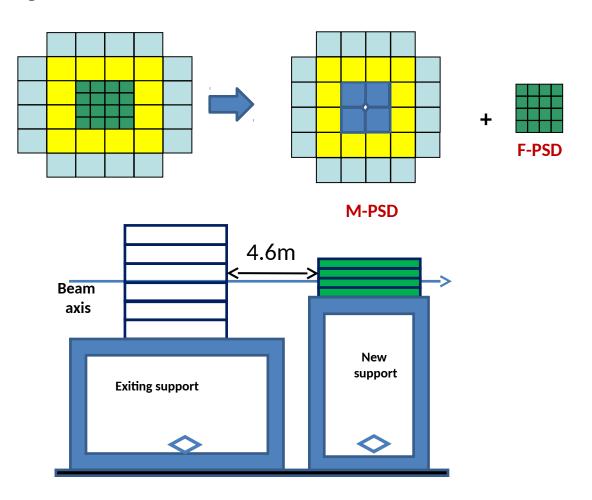

## **Proposed PSD upgrade (2017)**

Replace 16 central small modules in present PSD by 4 new large modules with truncated edge to have hole in the center with 60 mm diameter and use existing 16 modules as new second calorimeter.

## Photos of F-PSD behind main PSD (2018)

## **PSD** performance

#### Different variants for PSD readout

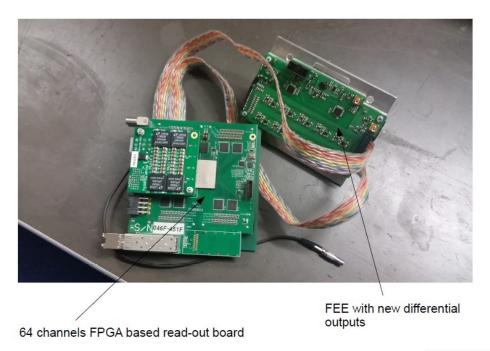

#### Dubna ADC64s2 readout board.

- 64 MHz pipe-line ADCs.

- 64 channes on board.

- 1 kHz trigger rate tested.

- Differential amplifiers and ADCs.

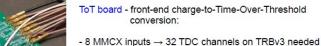

#### ToT FEE + TRB3 board.

- 256 channes on TRB3 board.

- NINO chip based design.

- DAQ functionality.

- Performance is to be tested.

TRBv3 - multi purpose time digitisation board:

- 23 ps RMS TDC (FPGAs)

- up to 256 channels

- DAQ functionality

- fast data transfer via gigabit Ethernet

- 6 IVIIVICA IIIpuls -> 32 TDC charines on TNBV3 fleeded

- NINO chip based design

- threshold settings through TRB3 SPI protocol

# Thank you for the beam!