# CMOS Active Pixel Sensors for High Energy Physics

Luciano Musa

15<sup>TH</sup> VIENNA CONFERENCE ON INSTRUMENTATION

#### ① Prelude

Overview of CMOS Image Sensors

#### 2 First use of CMOS pixel sensors in HEP

- STAR Heavy Flavor Tracker

- ALICE Inner Tracking System

#### **3** Novel Developments

Fully depleted sensors, wafer-scale integration, back-side processing

#### 4 Some example of non HEP applications

# Digital Imaging Revolution

Digital imaging began with the invention of the Charge-Coupled Device (CCD) in 1969

Start of the the digital imaging revolution

Boyle and Smith's invention improved commercial and consumer products for decades and is one of the most important technological innovations of the past half-century

Since its inception, digital imaging has progressed through improvements in CCDs and with the emergence of Complementary Metal-Oxide Silicon (CMOS) Image Sensor technology

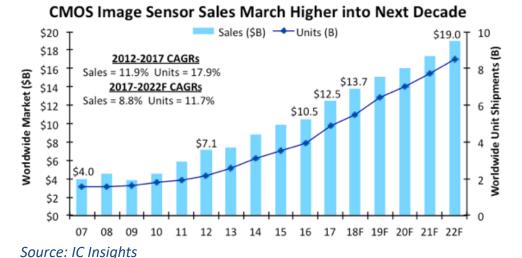

Since 10 years CMOS has become the leading imaging technology driving the second golden age ...

Nobel Prize in Physics 2009

Willard S. Boyle and George E. Smith "for the invention of an imaging semiconductor circuit - the CCD sensor."

# CMOS Image Sensor (CIS)

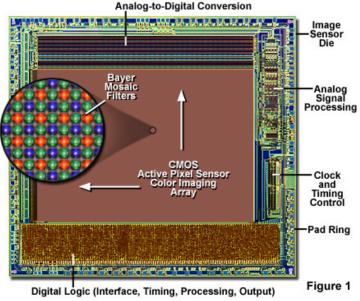

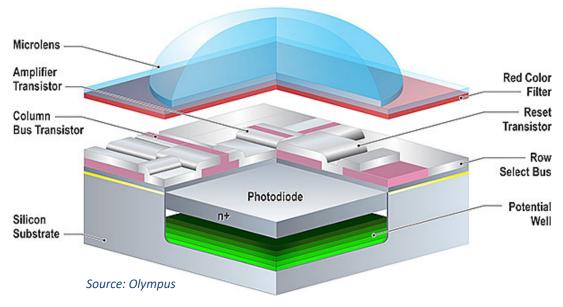

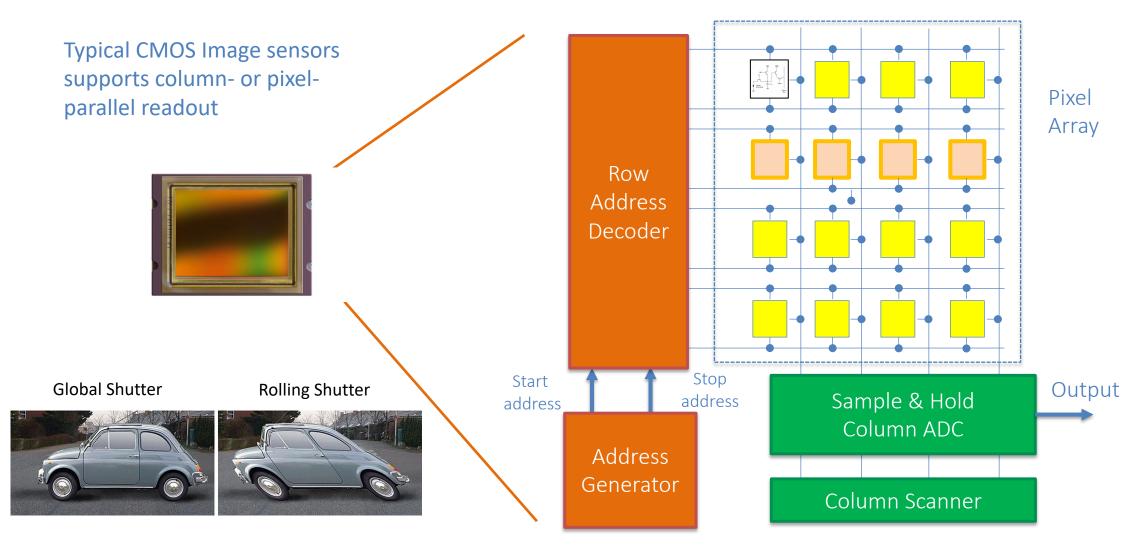

#### CMOS Image Sensor Integrated Circuit Architecture

Source: Olympus (optical microscopy)

camera phones, vehicles, machine vision, human recognition and security systems

⇒ drive CMOS image sensors development and sales cellular camera phones account for 62% of the sales

90% of the total image sensor sales in 2017 it was 74% in 2012, 54% in 2007

#### (Re)-invented in the early '90

- All-in-one: Electronic Camera On Chip

- Standard CMOS technology

- ⇒ lower production cost significantly

- ⇒ simpler integration of complex functionalities

- Very small pixels (today  $\sim 1 \mu m$ , 40M pixel)

- Single low-supply and much lower power consumption

- Increased speed (column- or pixel- parallel processing)

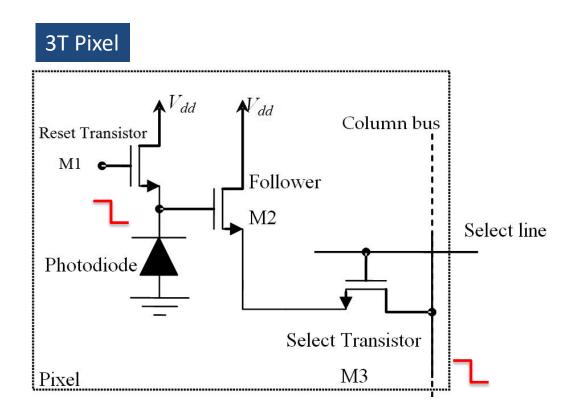

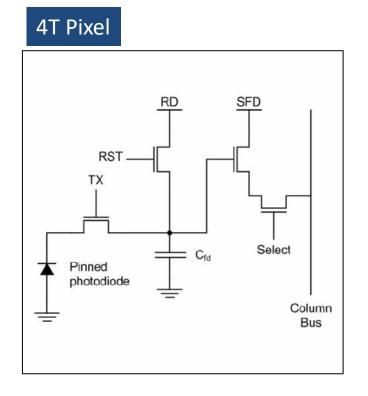

#### Structure of a CIS Pixel

#### Structure of a CIS Pixel

The photodiode usually occupies 20-30% of the pixel surface ... the rest if occupied by the in-pixel electronics

"integration time" = "exposure time", time between two consecutive reset pulses

Today, more complex structures (5T, 6T, ...) are also commonly used

# CMOS Image Sensors (CIS)

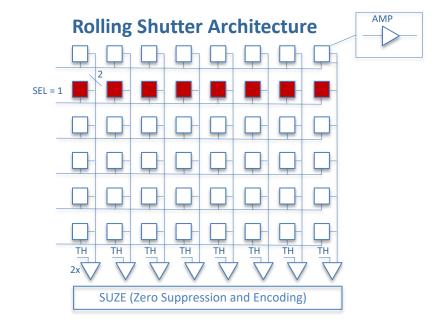

#### Rolling Shutter or Global shutter

# CMOS Image Sensors (CIS)

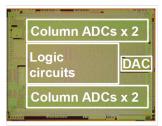

#### Industry's first 3-layer Stacked CMOS Image Sensor with DRAM for Smartphones (presented at ISSCC, Feb 2017)

Pixel array

DRAM + row drivers

Source: Sony/ISSCC

Image processor

Source: Sony

Advanced 3D assembly techniques make distinction between hybrid (separate sensor and readout chip) and monolithic more vague

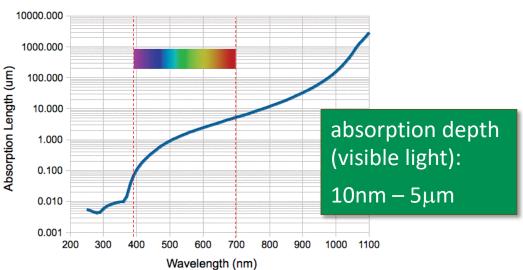

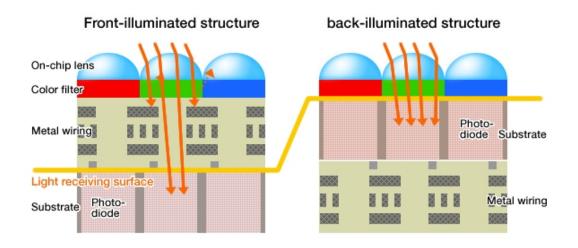

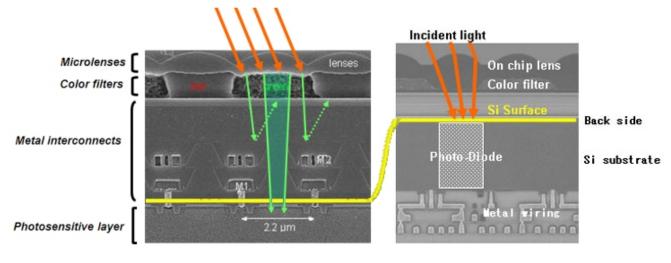

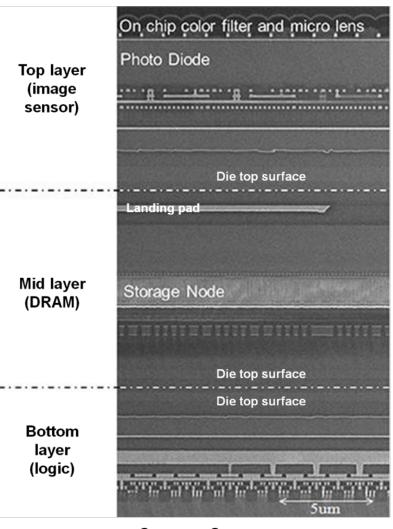

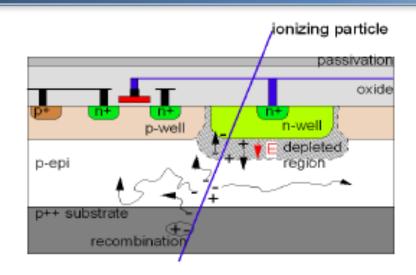

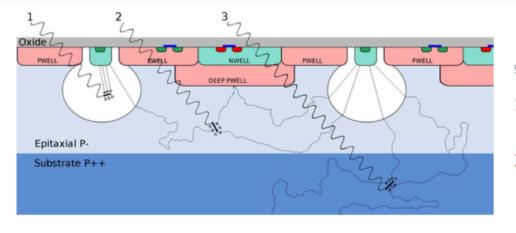

In a standard CMOS image sensor (in the early days) the photodiode is implanted in low-resistivity silicon

Depletion region is shallow, charge collection efficiency is low

Moreover the detector element covers only a small fraction of the pixel area

... not suitable for the measurement of single charged particles

9

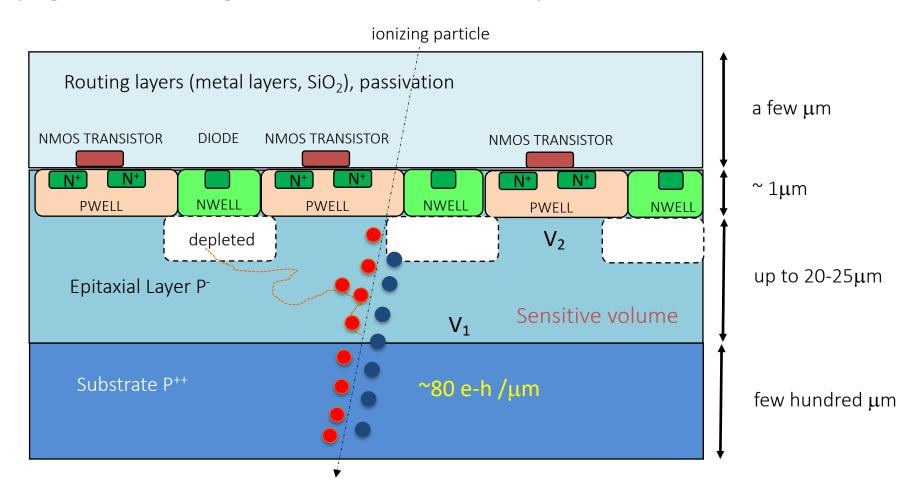

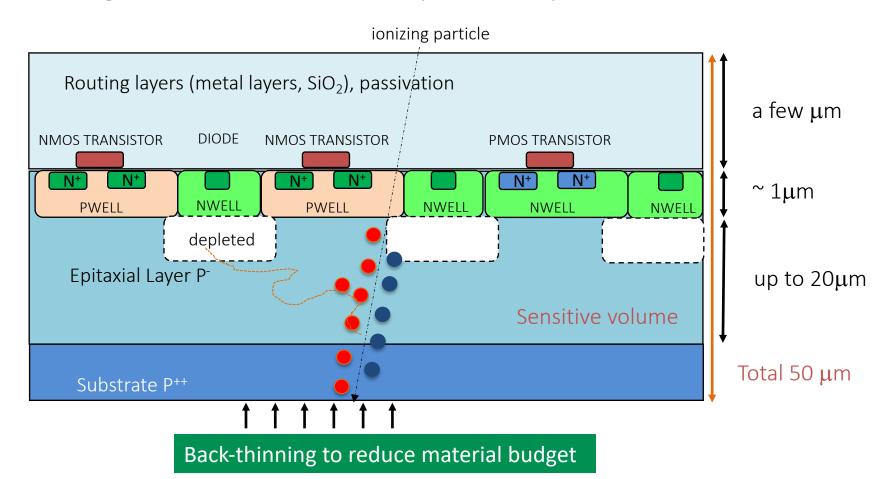

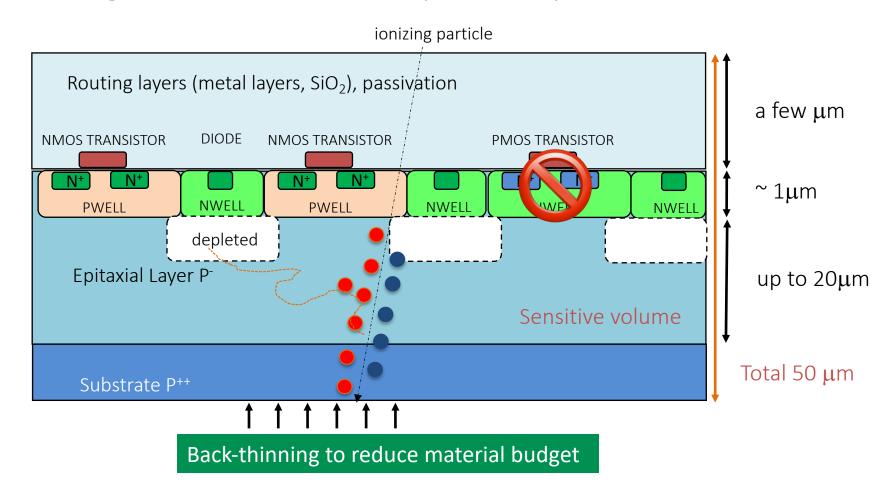

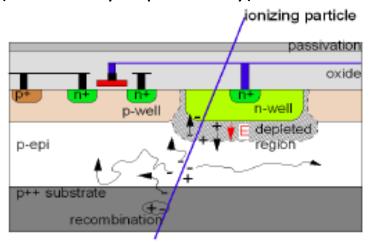

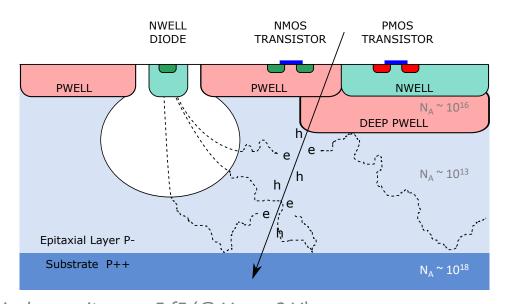

Use of an epitaxial layer with doping few order of magnitude smaller than one of the p++ substrate

Potential barriers exist at its boundaries

$$V_1 = \frac{kT}{q} \ln \frac{N_{sub}}{N_{epi}}$$

$$V_2 = \frac{kT}{q} ln \frac{N_{PWELL}}{N_{epi}}$$

which keep minority carriers confined in the epi-layer ....

... till they reach the depleted region underneath the NWELL collection electrode

Doping of epitaxial layer few order of magnitude smaller than that of the p-well or the p++ substrate

Potential barriers exist at its boundaries

$$V_1 = \frac{kT}{q} \ln \frac{N_{sub}}{N_{epi}}$$

$$V_2 = \frac{kT}{q} ln \frac{N_{PWELL}}{N_{epi}}$$

which keep minority carriers confined in the epi-layer ....

... till they reach the depleted region underneath the NWELL collection electrode

#### Doping of epitaxial layer few order of magnitude smaller than that of the p-well or the p++ substrate

Potential barriers exist at its boundaries

$$V_1 = \frac{kT}{q} \ln \frac{N_{sub}}{N_{epi}}$$

$$V_2 = \frac{kT}{q} ln \frac{N_{PWELL}}{N_{epi}}$$

which keep minority carriers confined in the epi-layer ....

... till they reach the depleted region underneath the NWELL collection electrode

# The inception of CMOS MAPS for charged particle tracking

Nuclear Instruments and Methods in Physics Research A 458 (2001) 677-689

NUCLEAR

INSTRUMENTS

& METHODS

IN PHYSICS

RESEARCH

Section A

www.elsevier.nl/locate/nima

A monolithic active pixel sensor for charged particle tracking and imaging using standard VLSI CMOS technology

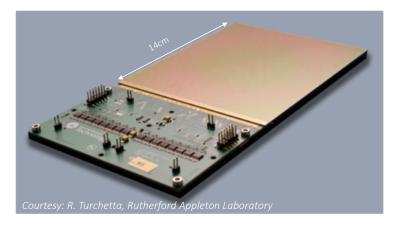

R. Turchetta<sup>a,\*</sup>, J.D. Berst<sup>a</sup>, B. Casadei<sup>a</sup>, G. Claus<sup>a</sup>, C. Colledani<sup>a</sup>, W. Dulinski<sup>a</sup>, Y. Hu<sup>a</sup>, D. Husson<sup>a</sup>, J.P. Le Normand<sup>a</sup>, J.L. Riester<sup>a</sup>, G. Deptuch<sup>b,1</sup>, U. Goerlach<sup>b</sup>, S. Higueret<sup>b</sup>, M. Winter<sup>b</sup>

<sup>a</sup>LEPSI, IN2P3/ULP, 23 rue du Loess, BP20, F-67037 Strasbourg, France <sup>b</sup>IReS. IN2P3/ULP, 23 rue du Loess, BP20, F-67037 Strasbourg, France

In a standard CMOS image sensor the photo diode is integrated in low-resistivity silicon:

- □ Standard CMOS substrate

- ⇒ Depletion region is shallow, charge collection efficiency is low

Moreover the detector element covers only a small fraction of the pixel area

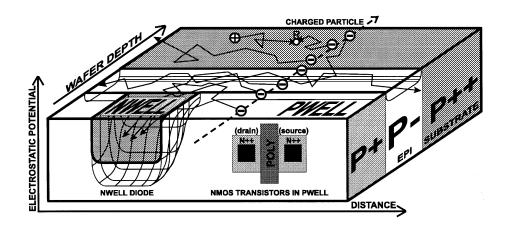

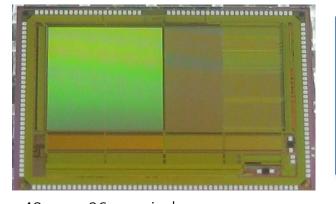

Integration of a sensor in  $0.6\mu m$  CMOS process

- Twin (P and N) tubs

- Implanted in lightly doped (P-) epitaxial silicon layer

- Grown on top of the highly doped (P++) substrate

The charge collection diode is made of the junction between the NWELL and the P-type epitaxial layer

# Development of CMOS APS – MIMOSA series

p-type crystalline epitaxial layer hosts n-well charge collector

Signal is generated in a high-resistivity (> 1 k $\Omega$ cm) epi-layer ~20 $\mu$ m thick (larger values possible)

Early versions with thin and low resistivity epi-layer

R&D mostly with AMS 0.6μm and 0.35μm technology

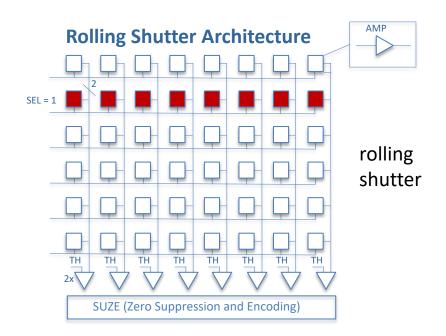

Only one transistor type in the active area (NMOS)

- ⇒ 2T or 3T in-pixel circuit

- ⇒ Rolling shutter architecture for matrix analogue readout

#### epi-layer not fully depleted

- ⇒ Charge collected (mostly) by diffusion and drift

- ⇒ Typical charge collection time < 100ns

Sensitive to radiation induced displacement damage in the epi layer  $\Rightarrow$  ok for applications with up to  $\sim 10^{12}$  1MeV N<sub>eq</sub>/cm<sup>2</sup>

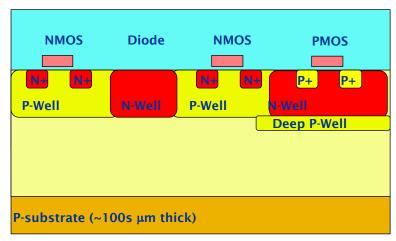

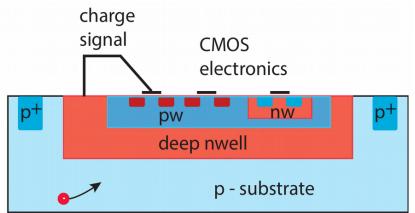

#### The INMAPS Process

"Monolithic Active Pixel Sensors (MAPS) in a Quadruple Well Technology for Nearly 100% Fill Factor and Full CMOS Pixel"

R. Turchetta et al., Sensors 2008, 8, 5336-5351; DOI: 10.3390/s8095336

Standard CMOS with additional deep P-well implant Quadruple well technology

100% efficiency and CMOS electronics in the pixel

#### New generation of CMOS APS for scientific applications with complex CMOS circuitry inside the pixel (TowerJazz CIS 180nm)

#### TPAC - for ILC ECAL (CALICE)

50μm pixel

PIMMS – for TOF mass spectroscopy

70µm pixel

CHERWELL – Calorimetry/Tracking

48 μm x 96 μm pixel

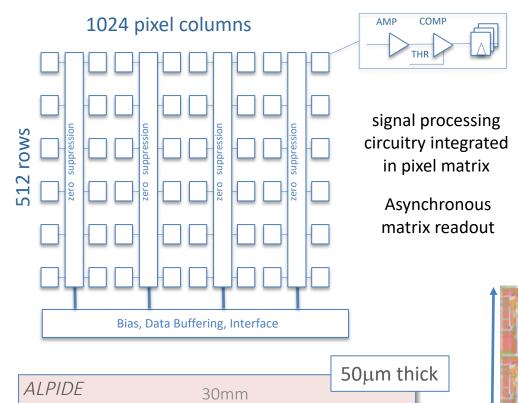

#### ALPIDE – Tracking

$27 \mu m \times 29 \mu m pixel$

# Development of CMOS APS (1999 – 2015)

Owing to the industrial development of CMOS imaging sensors and the intensive R&D by HEP community ...

... several experiments have selected CMOS APS (STAR, ALICE, CBM, NICA MPD, sPHENIX, Mu3e)

... and now intensive R&D ongoing for HL-LHC (ATLAS) and LC

**CBM MVD** 0.08 m<sup>2</sup> - 146 M pixel

ALICE ITS Upgrade (and MFT) 10 m<sup>2</sup> - 12 G pixel

sPHENIX  $0.2 \text{ m}^2 - 251 \text{ M pixel}$

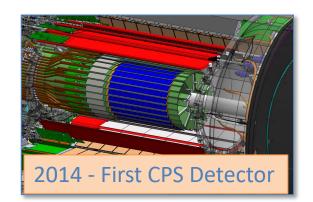

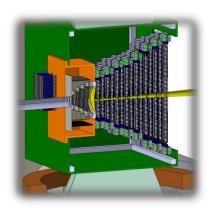

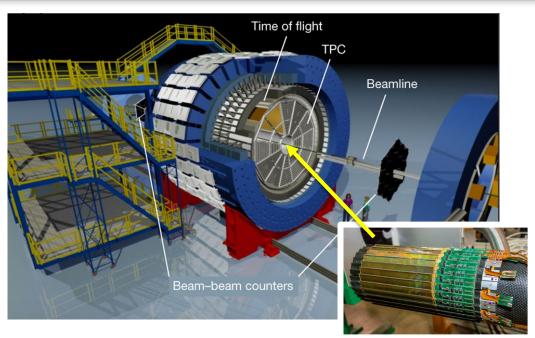

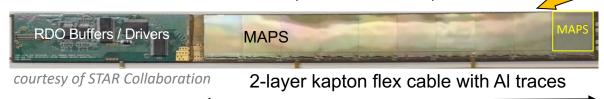

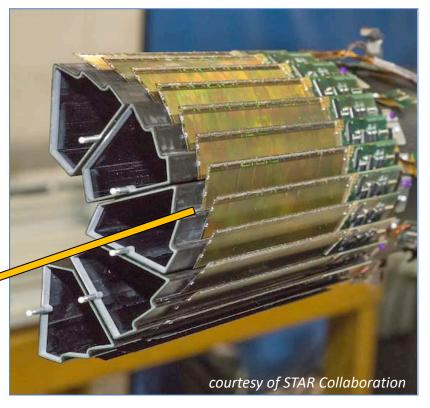

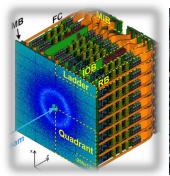

#### First use of CMOS APS in HEP - STAR Pixel Detector

- 2 layers (2.8cm and 8cm radii)

- 10 sectors total (in 2 halves)

- 4 ladders/sector

20 to 90 kRad / year  $2*10^{11}$  to  $10^{12}$  1MeV  $n_{eq}/cm^2$

Ladder with 10 MAPS sensors (~ 2×2 cm<sup>2</sup> each)

356 M pixels on ~0.16 m<sup>2</sup> of Silicon

- Full detector Jan 2014

- Physics Runs in 2015-216

Radiation length (1<sup>st</sup> layer):  $x/X_0 = 0.39\%$  (Al conductor cable)

#### First use of CMOS APS in HEP - STAR Pixel Detector

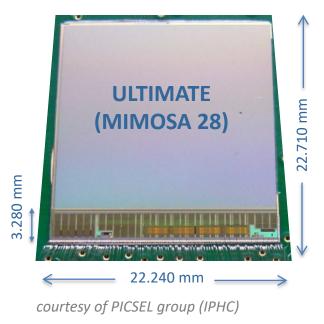

Process: AMS 0.35µm twin-well CMOS (NMOS only in pixel array)

courtesy of PICSEL group (IPHC)

20  $\mu$ m high-resistivity p-epi layer (~ 800  $\Omega$  cm)

#### Matrix

- pixel size:  $20.7 \mu m \times 20.7 \mu m$

- 928 rows x 960 columns ~ 1M pixel

- in-pixel circuit: 2T structure

- Correlated Double Sampling

#### Periphery

- end-of-column discriminators and zero suppression

- ping-pong memory for frame readout (1500 word)

- 2 LVDS output @160 MHz

- $185.6 \mu s$  integration time

- ~160 mW/cm<sup>2</sup> power dissipation

#### First use of CMOS APS in HEP - STAR Pixel Detector

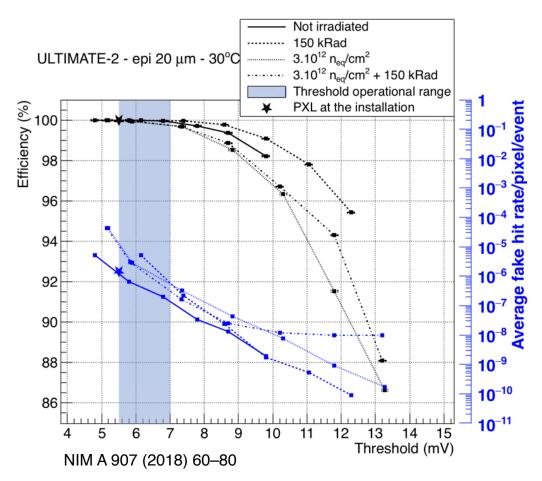

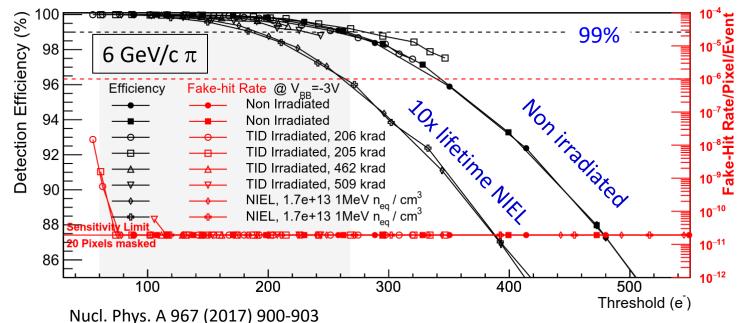

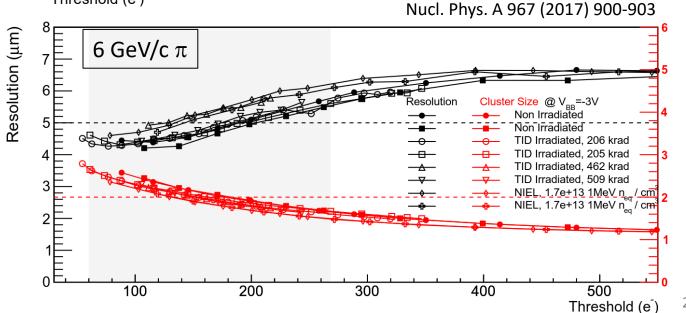

#### Detection efficiency and fake hit rate

#### ENC ≤ 15 $e^{-}$ at 30-35 °C

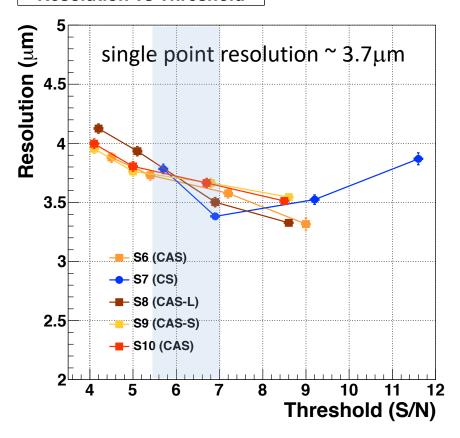

#### **Spatial Resolution**

#### **Resolution vs Threshold**

Single point resolution  $\approx 3.7 \mu m$

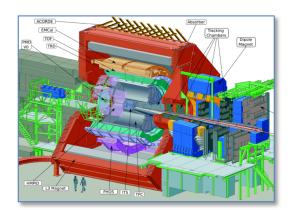

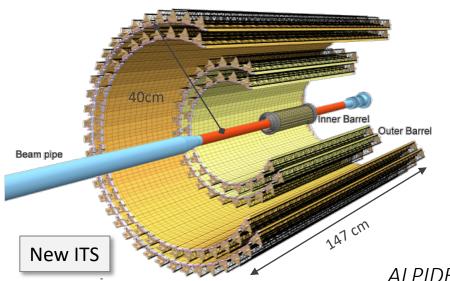

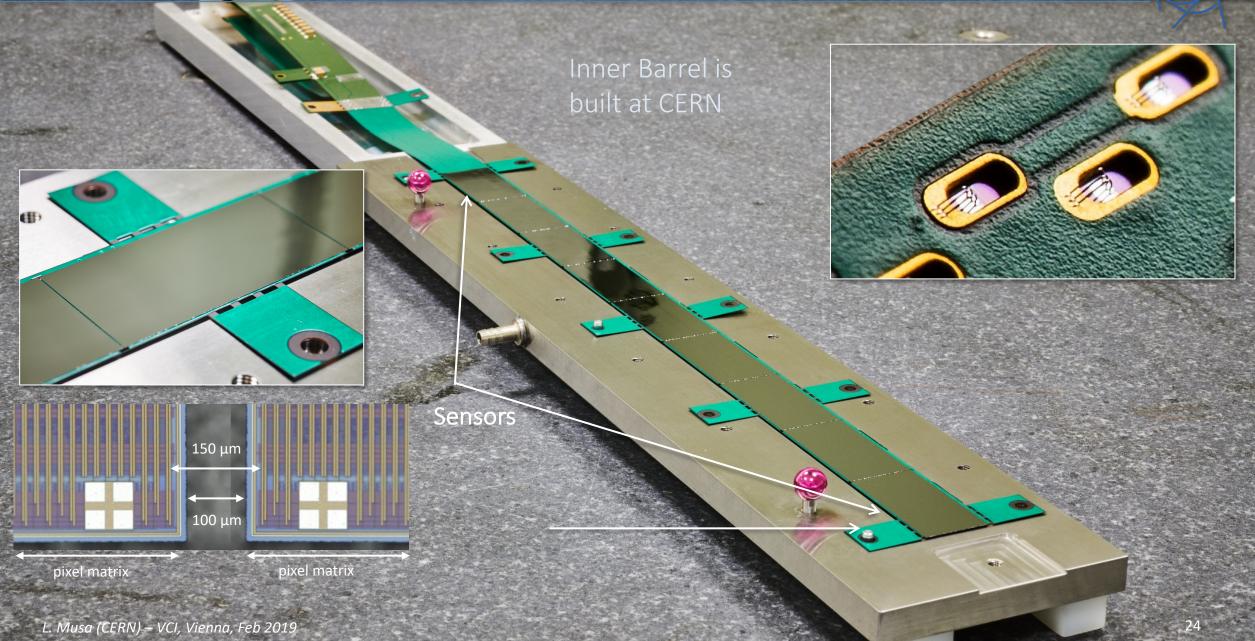

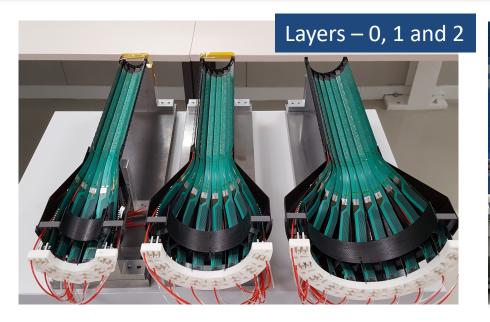

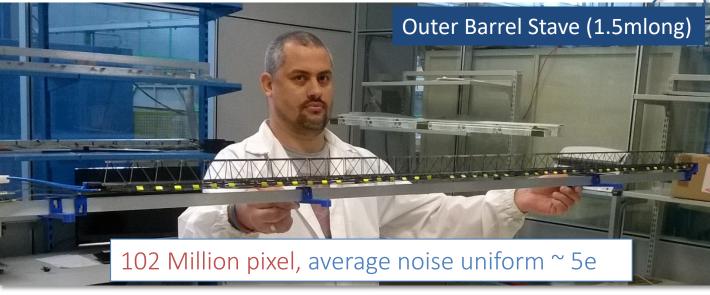

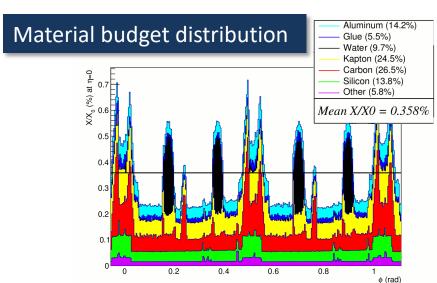

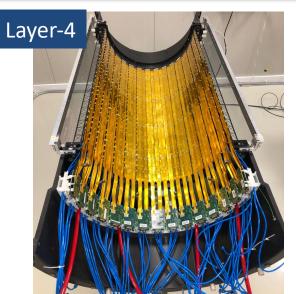

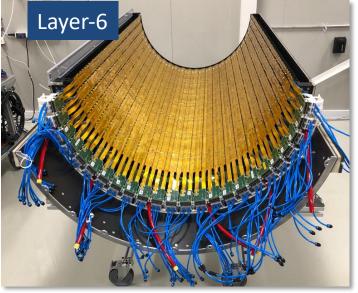

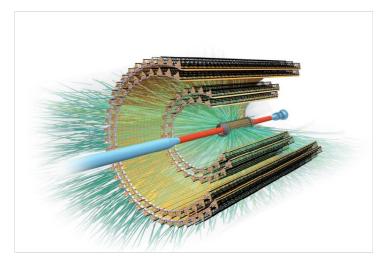

# New ALICE ITS: closer to IP, thinner, higher position resolution

Closer to IP: 39mm → 22mm

Thinner: ~1.14% → ~ 0.3% (for inner layers)

Smaller pixels:  $50\mu \text{m} \times 425\mu \text{m} \Rightarrow 27\mu \text{m} \times 29\mu \text{m}$

Increase granularity: 20 chan/cm<sup>3</sup> → 2k pixel/cm<sup>3</sup>

Faster readout:  $x 10^2 \text{ Pb-Pb}, x 10^3 \text{ pp}$

10 m<sup>2</sup> active silicon: 12.5 G-pixels,  $\sigma \approx 5 \mu m$

$1.5 \le \eta \le 1.5$

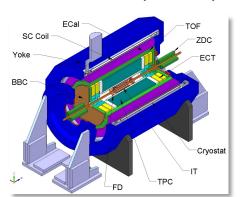

ALPIDE (ALICE Pixel Detector) - Developed for the ALICE upgrade (ITS and MFT) will be used for several other HEP detectors and non HEP applications

#### NICA MPD (@JINR)

#### sPHENIX (BNL)

#### proton CT (tracking)

CSES – HEPD2

Talk of Wladyslaw Henryk Trzaska, Tue Talk of

Talk of Naomi Van Der Kolk, Tue

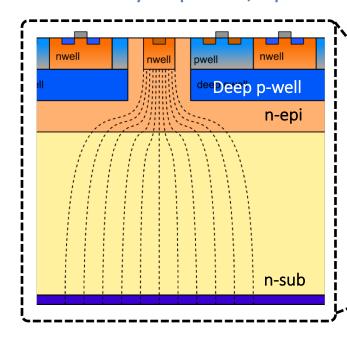

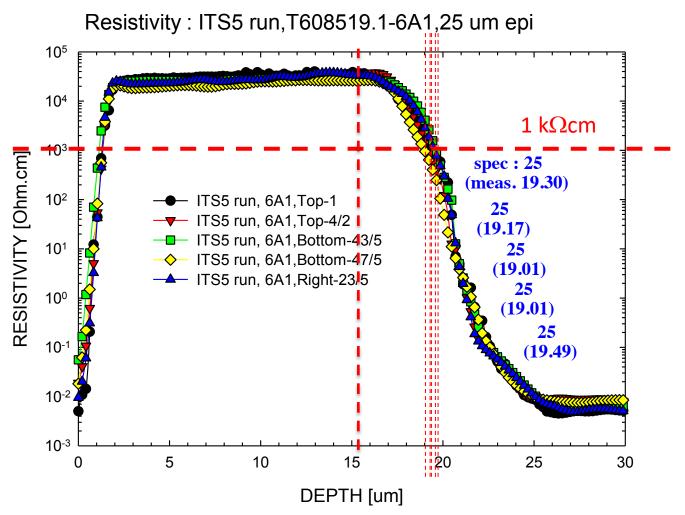

#### CMOS Pixel Sensor using TJ 0.18µm CMOS Imaging Process

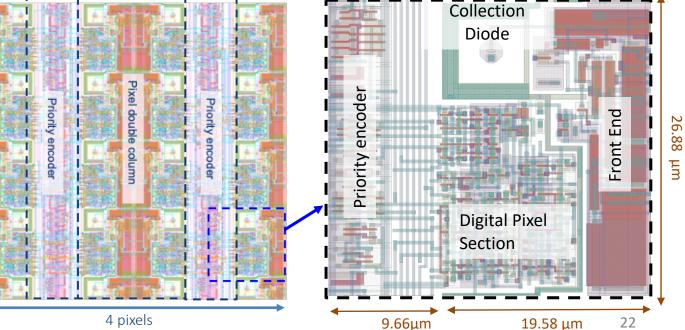

28 µm 2 x 2 pixel volume Artistic view of a SEM picture of ALPIDE cross section  $C_{in} \approx 5 \text{ fF}$ Q<sub>in</sub> (MIP) ≈ 1300 e ⇒ V ≈ 40mV

collection electrode

- pixel capacitance  $\approx 5$  fF (@  $V_{hh} = -3$  V)

- High-resistivity (>  $1k\Omega$  cm) p-type epitaxial layer (25 $\mu$ m) on p-type substrate

- Small n-well diode (2  $\mu$ m diameter), ~100 times smaller than pixel => low capacitance (~fF)

- Reverse bias voltage (-6V <  $V_{BB}$  < 0V) to substrate (contact from the top) to increase depletion zone around NWELL collection diode

- Deep PWELL shields NWELL of PMOS transistors

full CMOS circuitry within active area

pags over matrix

pixel matrix

130,000 pixels / cm<sup>2</sup> 27x29x25  $\mu$ m<sup>3</sup>

charge collection time <30ns ( $V_{bb} = -3V$ )

Max particle rate: 100 MHz/cm<sup>2</sup>

fake-hit rate: < 1 Hz/cm<sup>2</sup>

power:  $\approx 300 \text{ nW /pixel (} < 40 \text{mW/cm}^2\text{)}$

#### Matrix Layout

#### Pixel Layout

periphery

Large operational margin with only 10 masked pixels (0.002%), fake-hit rate  $< 2 \times 10^{-11}$  pixel/event

Non irradiated and TID/NIEL chips similar performance

5  $\mu$ m resolution @ 200 e<sup>-</sup> threshold Chip-to-chip negligible fluctuations

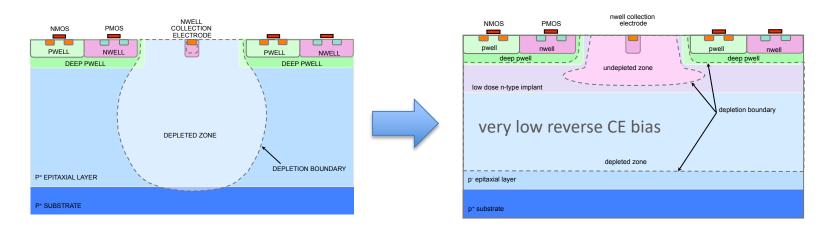

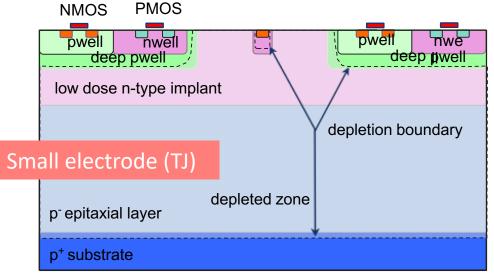

# Fully depleted MAPS – small electrodes with TJ modified process

A process modification for CMOS Active Pixel Sensors (side activity of ALICE R&D)

A possible solution to achieve full depletion of the sensitive layer combined with a low capacitance electrode is to implement a planar junction separate from the collection electrode

Standard Process (+DEEP PWELL)

Modified Process with low-dose n-type implant (+DEEP PWELL)

The process modification requires a single additional process mask with no changes on the sensor and circuit layout

For details on process modification and experimental results: W. Snoeys et al. NIM, A 871C (2017) pp. 90-96

The ALICE test vehicle chip (investigator) and prototype ALPIDE chips exist with both flavors

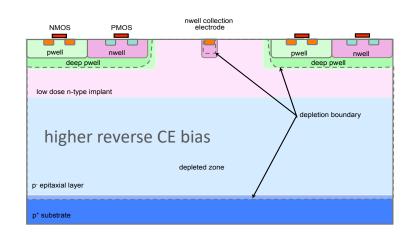

# Fully depleted MAPS – small electrodes with TJ modified process

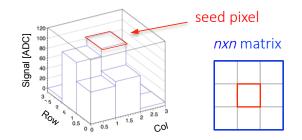

#### Signal and cluster distribution from a <sup>55</sup>Fe source for standard and modified process

Modified Process 1 = higher dose, Modified Process = lower dose

J. Van Hoorne et al., NSS 2016

Tests performed on investigator chip (same pixel as ALPIDE)

Pixel size:  $28 \times 28 \mu m^2$ , CE:  $2 \times 2 \mu m^2$  centered in a  $8 \times 8 \mu m^2$  opening,

P-well & substrate @ -6V, CE @ 1V

- For a lower dose (MP1) a no sensor capacitance penalty

- For modified process, larger fraction of single pixel clusters (see also fraction of signal within the peak in A)

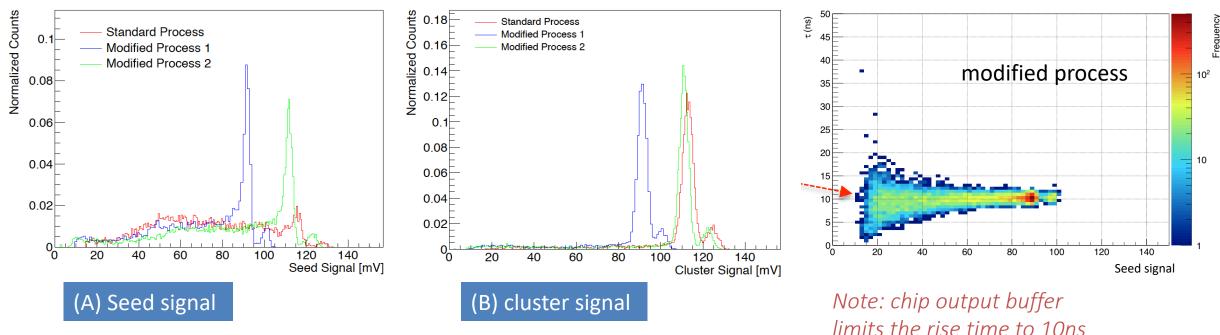

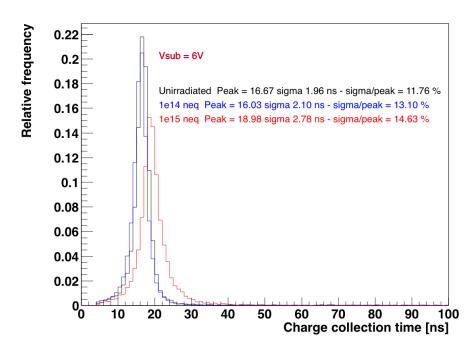

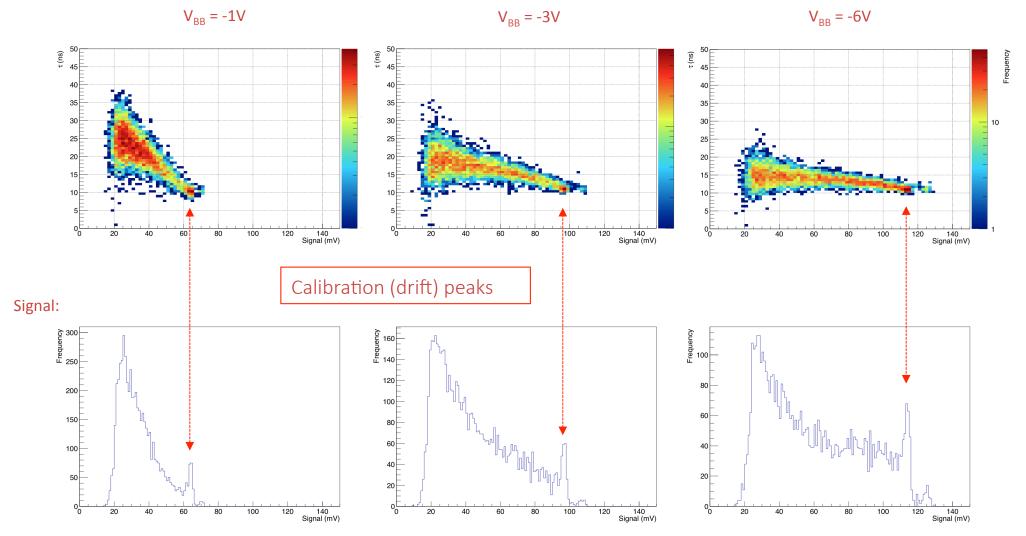

# TJ modified process – charge collection time

28

<sup>90</sup>Sr measurements on modified process samples (different setup, different pixel w.r.t. before)

- Non-irradiated

- $1 \times 10^{14}$  1MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL) and 100krad (TID)

- $1 \times 10^{15}$  1MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL) and 1Mrad (TID)

#### H. Pernegger et al 2017 JINST 12 P06008

Tests performed on investigator chip (different pixel wrt to ALPIDE) Note: chip output buffer limits the rise time to 10ns Pixel size:  $50 \times 50 \ \mu\text{m}^2$ , CE:  $3 \times 3 \ \mu\text{m}^2$  centered in a  $18 \times 18 \ \mu\text{m}^2$  opening,  $25 \mu\text{m}$  epi

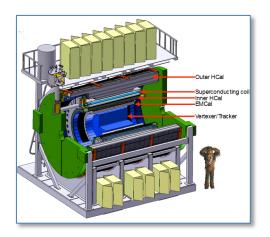

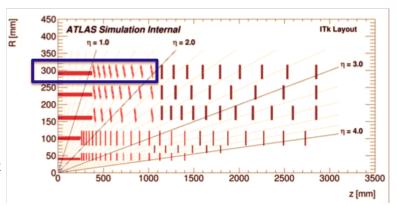

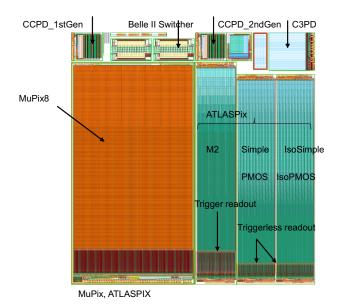

# New developments for ATLAS ITk L4

#### Outermost layer of ITk Pixel Barrel

- 2016 quad modules

- 3m<sup>2</sup>

#### For 4000 fb<sup>-1</sup>

- TID = 80 Mrad

- NIEL =  $1.5 \times 10^{15} \, n_{eq}/cm^2$

# Monolithic CMOS sensors are considered as option for the outermost layer

- Saves bump bonding for 45% of outer barrel system

- Cost reduction and reduce module assembly time

#### Three developments on three technologies

- Large CE: LFOUNDRY (Monopix) Toko Hirono, Thu

- Small electrode: TJ modified process (MALTA, Monopix)

Enrico Junior Schioppa, Thu

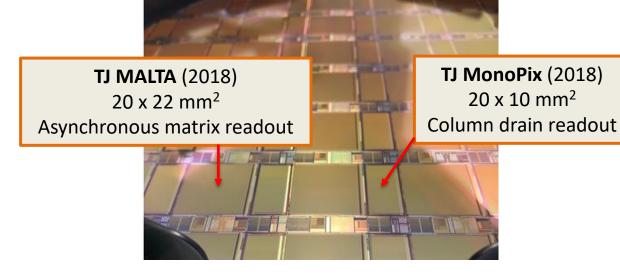

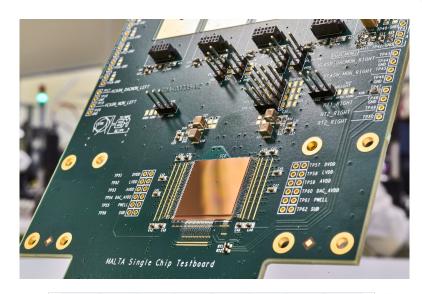

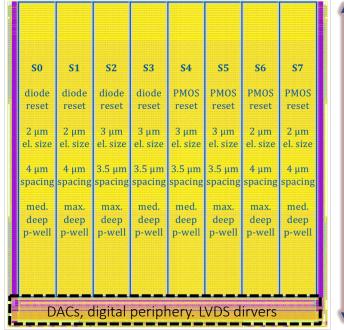

# New developments for ATLAS ITk: small electrode TJ modified process

Design of two large scale demonstrators

Collaboration CERN - Bonn

- The 512 x 512 pixel 8 sectors

- Front-end is a development from the ALPIDE one

- Design based on low-power analogue front-end and an asynchronous architecture to readout the pixel matrix

18.6 mm

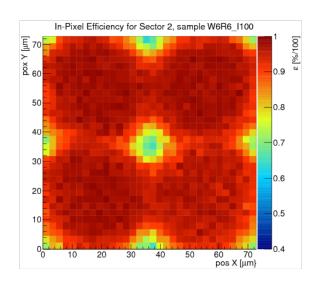

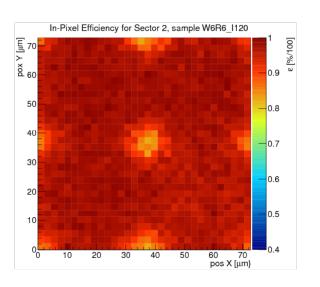

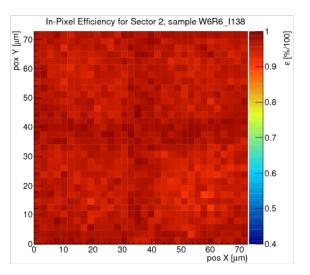

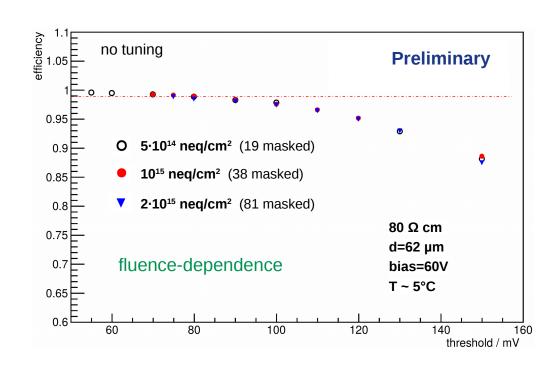

# MALTA – efficieny in test beam before and after irradiation

#### Unirradiated:

lowering the threshold gives the full efficiency

#### Decreasing threshold from ~600 e<sup>-</sup> to ~250e- (unirradiated) / ~350e<sup>-</sup> (irrad.)

Could not reach Lower threshold (RTS + Making issues)

New prototypes that fix both problems are currently under test

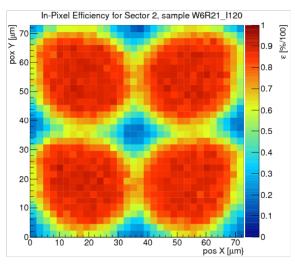

Neutron irradiated  $5x 10^{14} n_{eq}/cm^2$

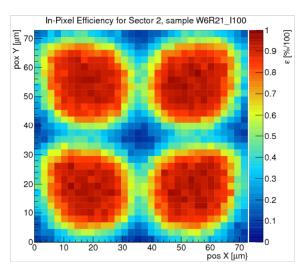

Inefficiency in pixel corners due to low lateral electric field

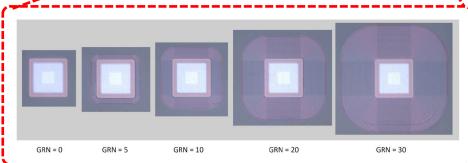

# MALTA – efficiency in test beam before and after irradiation

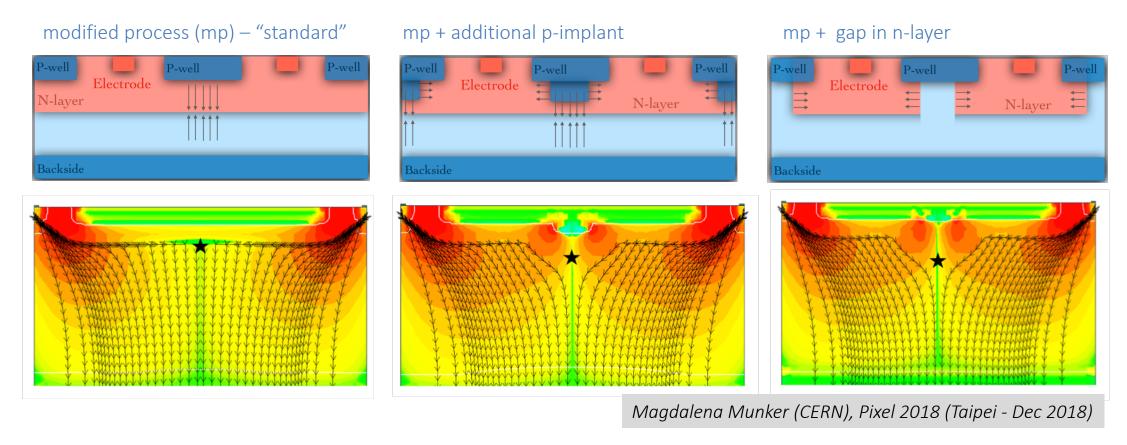

TJ modified process: E field minimum at pixel corners => charges pushed to the minimum before they propagate to CE

Additional p-implant or gap in n-layers: bend the field towards the CR, shorted drift path

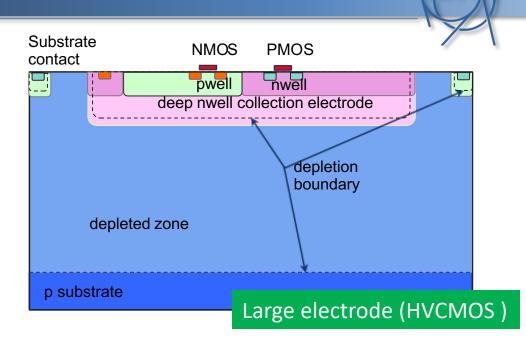

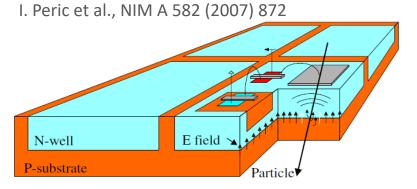

# HV CMOS – developments for the Mu3e tracker and ATLAS

CERN

- Compatible with standard CMOS technology

- Triple well process on p-type substrate (20- 1000  $\Omega$  cm)

- Prototypes with var CMOS processes (AMS, TSI, LFounfry)

The HV CMOS Collaboration

- The collection diode occupies a large part of the pixel

- Electronic circuits inside deep n-well

- HV O(60 120V) contacts at the top side

- MUPIX8 pixel: 80x81 μm<sup>2</sup>

- Circuitry in the collection diode introduces additional sensor capacitance

- Keep pixel circuitry as simple as possible

- Confine digital circuitry at the periphery

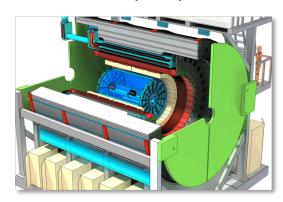

# MUPIX8 - a full-scale HV-CMOS prototype for the Mu3e tracker

#### Time resolution with timewalk correction

# $\sigma_{\text{time}} = 6.4 \text{ ns}$

#### Efficiency and fake hit rate

courtesy of I. Peric and A. Schoening

# INFN projects SEED and ARCADIA: two phases of the same development

#### The SEED project successfully demonstrated a fully depleted, up to 300 µm thick MAPS sensor

- LFoundry 110nm CMOS process.

- Sensor nodes are n-type implantation (become insulated only with full substrate depletion)

- The high resistivity, floating zone n-type substrate is depleted by negative voltage at the p+ backside

- Deep pwell implantations allows implementing <u>full CMOS gates</u>

Collection n+/n implants

nwell guard ring (dedicated pad)

Perypheral electronics

nwell movel powell

n-epi

Substrate contacts (holes in deep pwell)

Backside contact: glued on package with conductive epoxy

- Double-sided lithography was used for the processing of the backside layers (5 extra masks)

- The backside p+ implantation was done after thinning the substrate, and activated with laser annealing

- To avoid early breakdown, termination structures with floating guard rings have been added at the borders

Different guard-rings on the backside diodes

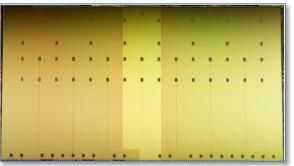

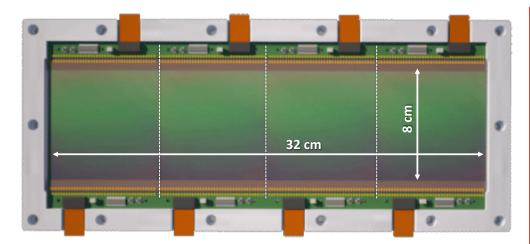

# CMOS APS – wafer-scale integration

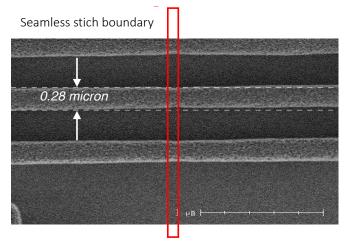

Photolithographic process defines wafer reticles size  $\Rightarrow$  Typical field of view O(2 x 2 cm<sup>2</sup>)

Reticle is stepped across the wafers to create multiple identical images of the circuit(s)

A stepping process called "stitching" allows building sensors of arbitrary size, the only limit being the size of the wafer.

- Reticle made of blocks

- Printing only individual blocks at each step with a tiny well-defined overlap

These days, stitching is widely applied in the digital imaging industry (e.g. large flat panels for medical and dental X-rays)

Ultra-thin chip (<50 um): flexible with good stability

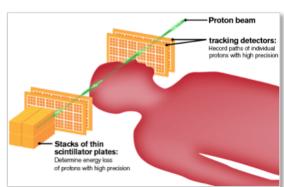

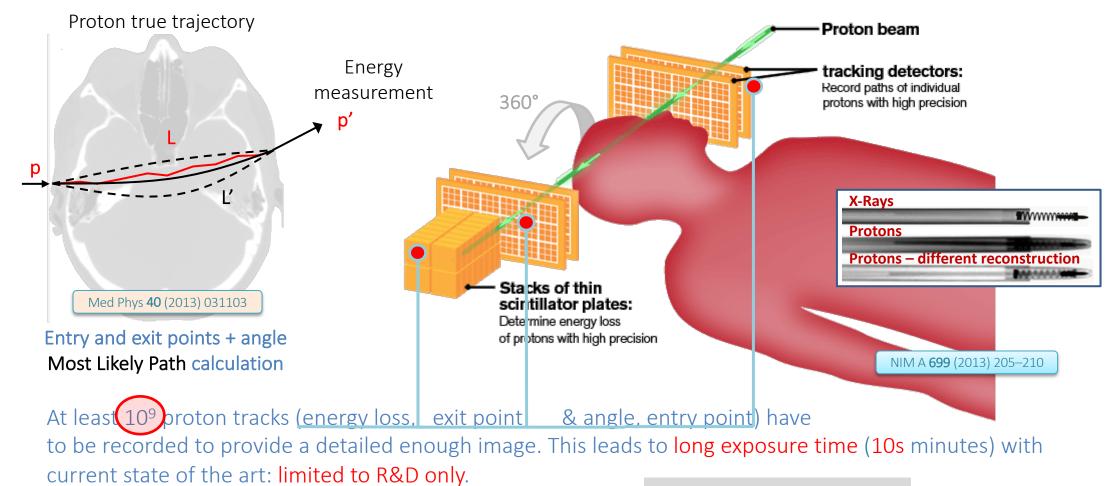

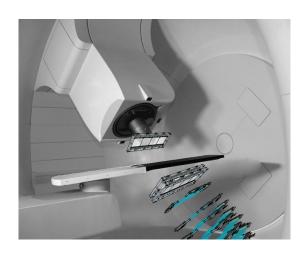

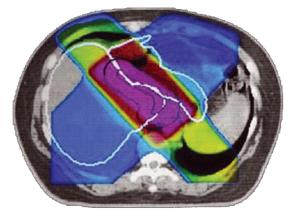

# Medical imaging can be further improved moving to Medical Tracking

The pCT works on the same principle as a "standard" x-rays CT: recording particles passing through the target from different angles to reconstruct a 3D image. Main difference is that, while photons are simply absorbed, protons also scatter

#### Medical tracking requires sensors which still DO NOT EXIST

- Fast (> 10 MHz cm<sup>-2</sup>) proton tracking at low power in silicon (50 mW cm<sup>-2</sup>)

- Monolithic, thinned ( $\leq 50 \, \mu m$ ) and large area ( $> 16 \, cm^2$ ) device to minimize proton scattering.

- No support structure behind the silicon

- Cost effective, reliable, simplified commissioning & operations, commercial process (for large production)

- Low voltage for real clinical usage

#### ALPIDE is an excellent starting point, currently used by many groups for medical R&D

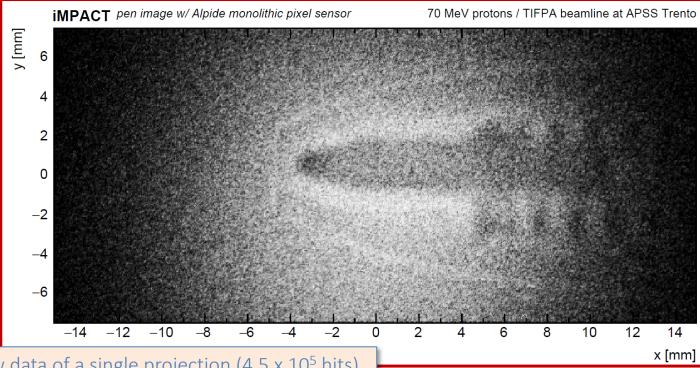

ALPIDE used to take a demonstrative proton radiography of a pen:

metal, different plastic densities, air distinguishable

Talk of Ganesh Tambav, Thu

raw data of a single projection (4.5 x 10<sup>5</sup> hits)

38

# Concluding Remarks

Large area, monolithic, low power pixel sensors are enabling devices for many cutting-edge research field and practical application: HEP trackers, medical imaging, space-borne instruments, FEL imagers, etc...

<u>The HEP community is in an unique position</u> to bridge between different fields and drive for sensors advancement, leveraging on the last decades experience and acquired know-how!

# Concluding Remarks

Large area, monolithic, low power pixel sensors are enabling devices for many cutting-edge research field and practical application: HEP trackers, medical imaging, space-borne instruments, FEL imagers, etc...

<u>The HEP community is in an unique position</u> to bridge between different fields and drive for sensors advancement, leveraging on the last decades experience and acquired know-how!

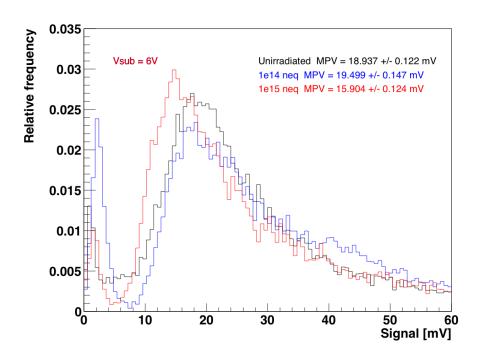

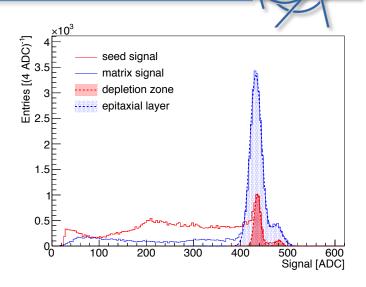

### X-ray detection in a sensor with std process

<sup>55</sup>Fe: two X-Ray emission modes:

- L. K- $\alpha$ : 5.9keV (1640 e/h in Si), rel. freq.: 89.5%, attenuation length in Si: 29 $\mu$ m

- K-β: 6.5keV (1800 e/h in Si), rel. freq.: 10.5%, attenuation length in Si: 37μm

For X-ray absorption in sensors fabricated with the std process, three cases can be defined

- 1. Absorption in depleted volume: charge collected by drift, no charge sharing, single pixel cluster

- These events populate the calibration peak in the signal histogram

- Charge collection time expected to be <1ns</li>

- 2. Absorption in non depleted volume of the epitaxial layer: charge partially collected by diffusion and then drift, charge sharing depending on position of X-Ray absorption

- Charge collection time expected to be dependent on distance of X-Ray absorption from the depleted volume, and longer than events of case 1.

#### 3. Absorption in substrate

• Contribution depending on depth of X-Ray absorption, and charge carrier lifetime within substrate

41

# TJ standard process – charge collection time and seed signal

Tests performed on investigator chip (same pixel as ALPIDE) with analogue readout

Pixel size:  $28 \times 28 \mu m^2$ , CE:  $2 \times 2 \mu m^2$  centered in a  $8 \times 8 \mu m^2$  opening, P-well & substrate @ -6V, CE @ 1V

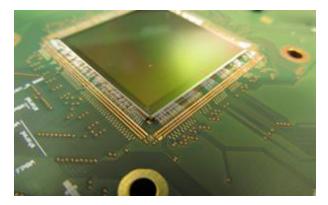

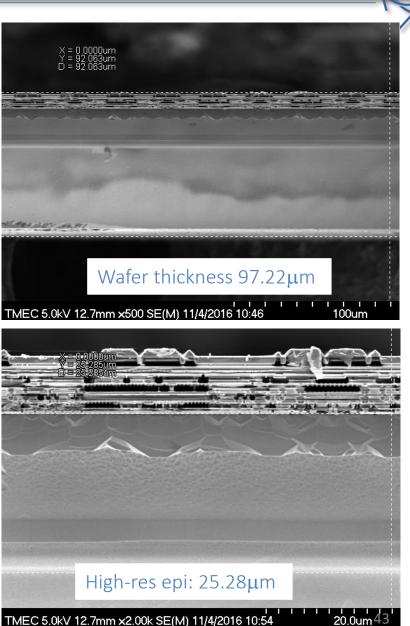

# **ALICE CMOS Pixel Sensor**

Blank Wafers QA at TMEC (SRP and XSEM measurements)

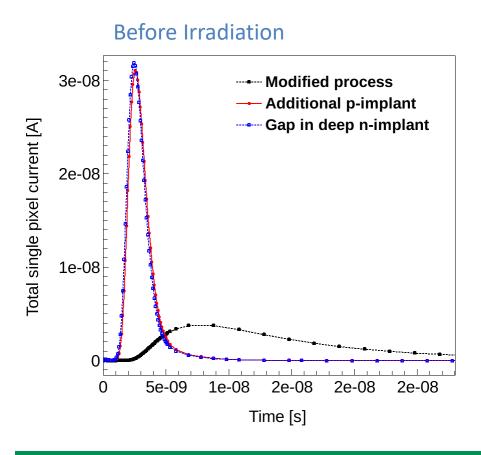

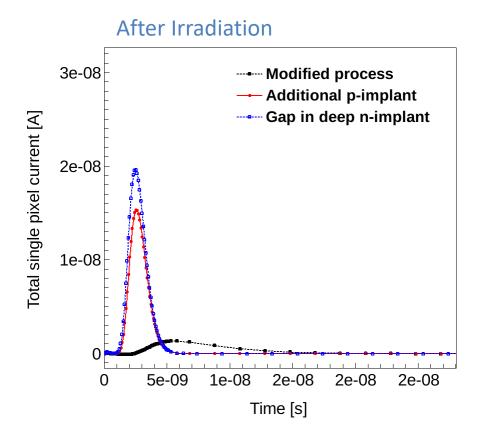

# TJ modified process with additional p-implant or with gap in n-layer

#### Current pulse signal

Magdalena Munker (CERN), Pixel 2018 (Taipei - Dec 2018)

Significantly faster charge collection for design with additional p-implant and gap in n-layer

New prototypes with both type of further process modifications are presently being tested