# A novel HV silicon JFET for ATLAS, and other silicon R&D activities at BNL 32<sup>nd</sup> RD50 workshop – 4-6 June 2018 Hamburg

Gabriele Giacomini, Wei Chen, Francesco Lanni, David Lynn, Alessandro Tricoli (Brookhaven National Lab)

Enrico Rossi (Stony Brook University and Brookhaven National Lab)

## Outline

#### Activities on-going at Brookhaven National Lab:

- HV silicon JFET for multiplexing in ATLAS Inner Tracker (ITk) for HL-LHC phase

→ BNL is involved in strip sensor stave R&D and constructions

- LGAD R&D

→ High Granularity Timing Detector

- Commissioning of BLIP, a new irradiation facility for silicon R&D

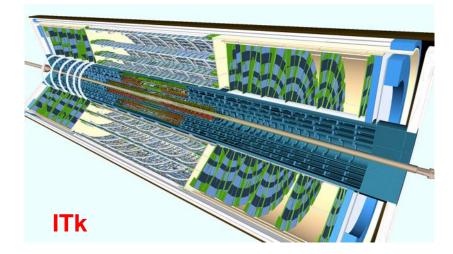

## HV multiplexer in ATLAS ITk

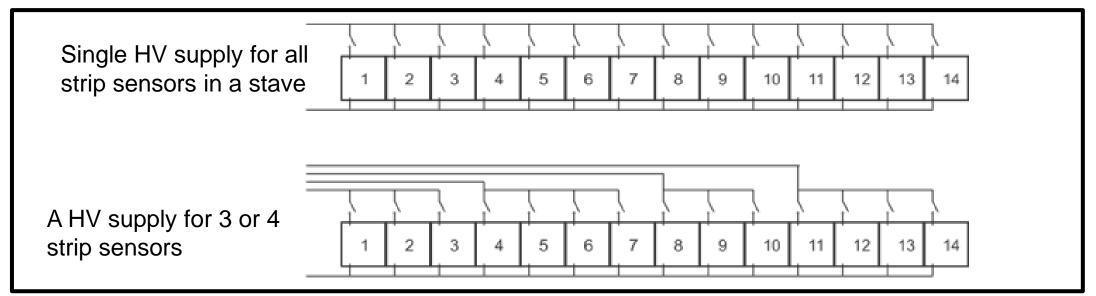

- Cable space limitations do not permit each module in the stave to have its own HV power supply

- The solution has been proposed by BNL: have multiple modules connected to the HV bus with slow controlled switch that can disconnect malfunctioning sensors

- Transistor must switch greater than 500V, be radiation hard and operate in a 2 T magnetic field

- Converged on Panasonic GaNFET as single candidate

- devices powered either in on- or off-state survived irradiations with pions, neutrons, photons and protons

- Can we do a HV-JFET made of silicon ?

## Standard planar JFET

It is a basic electronic device solvable analytically. Essentially a 1-D structure.

$V_{drain-qate}$  is limited by the breakdown at that junction.

*n*-channel, doping 1e16cm<sup>-3</sup>, thickness =1 $\mu$ m, width = 1 $\mu$ m, length = 5 $\mu$ m

A CENTURY OF SERVICE

Power semiconductor devices go vertical: the high voltage falls in the High Resistivity thick bulk. Example: power MOSFET, thyristors (SCR), pin diode.

#### **Can we do a Vertical JFET?**

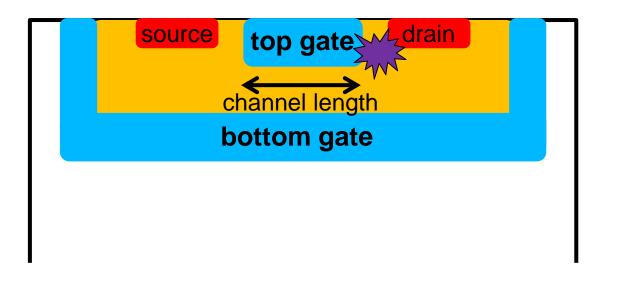

## The vertical HV Silicon JFET

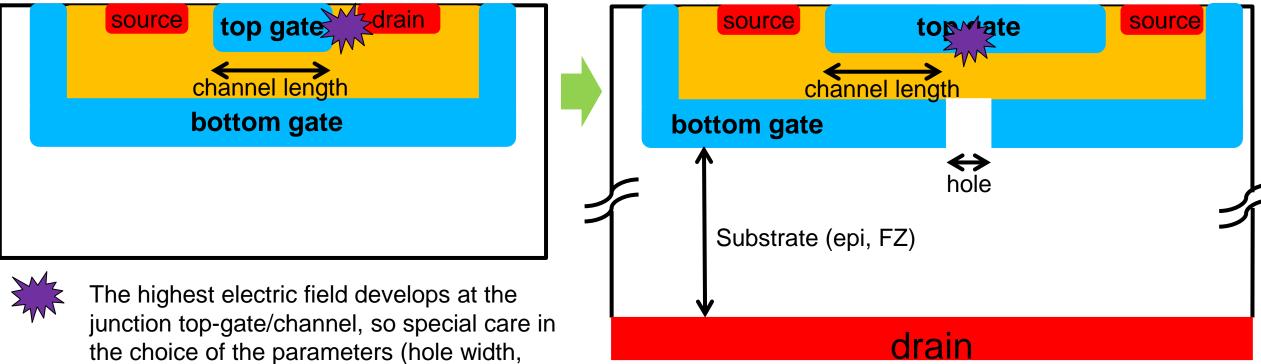

We can modify the structure of the standard JFET by making a hole in the bottom-gate. Over the hole, the top-gate. The channel and the source as in the standard JFET. The drain is the back contact. The current flows (= drifts) from source to drain through the hole in the bottom-gate.

The high voltage applied to the drain falls in the thick substrate, being the bottom-gate almost a planar implant.

A CENTURY OF SERVICE

channel doping concentration). GR termination also needed at the border of the bottom-gate.

## **TCAD** simulations

**Electron Current Density**

Top-gate @-0.5V

drain @ +300

source

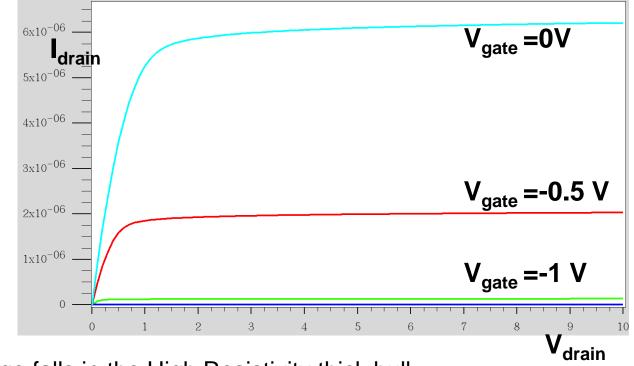

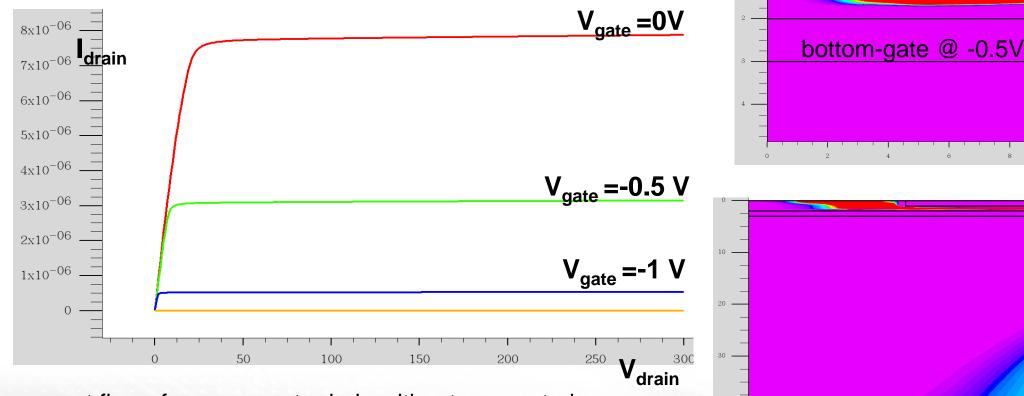

TCAD simulations show that it works!

- The ON currents are essentially the same.

- Also the pinch-off gate-voltage is the same.

- high V<sub>D saturation</sub>, because the bottom-gate shields the drain voltage, so that the channel gets its pinch-off voltage at high V<sub>D</sub>

The current flows from source to drain without encountering any potential barrier. Then it spreads into the resistive bulk.

## A few Points to be considered

#### Choice of the substrate:

→ resistivity as low as possible to avoid a high-resistance path for the ON current. But,  $V_{BD}$  depends on the doping, so a compromise has to be chosen. Once we set the max operational voltage (<  $V_{BD}$ ), we can choose the doping and the thickness of the epitaxial layer.

For example, we want V\_{BD} > 600V, so N\_C = 1e14cm^{-3} and 50  $\mu m$  thick is OK

Fabricated test diodes show  $V_{BD} > 600V$ , but the GR termination has to be redesigned, for not standard N<sub>C</sub>.

#### Dimension of the hole:

The larger the hole, the higher the electric field, but the smaller the V<sub>Dsat</sub>, also here a compromise.

#### Horn effect:

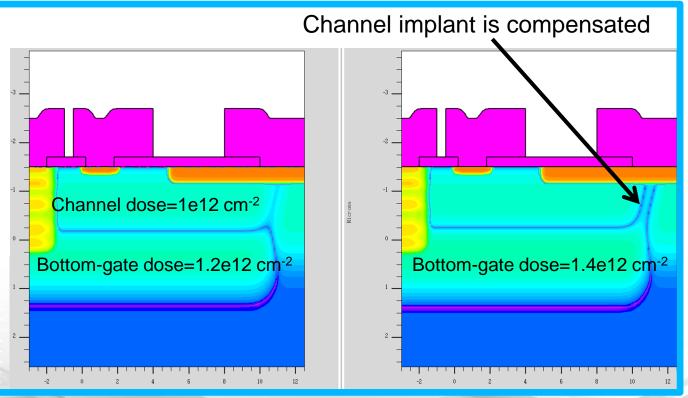

When implanting the bottom gate, the implant is blocked in the hole region by a thickness of resist and oxide. But at the border of this region some implant passes and leaves an unwanted doping. This horn can compensate the channel doping. So in turns, it sets a limit to the doping of the bottom gate.

For the real, fabrication we can choose within a limited range of parameters (splittings will help).

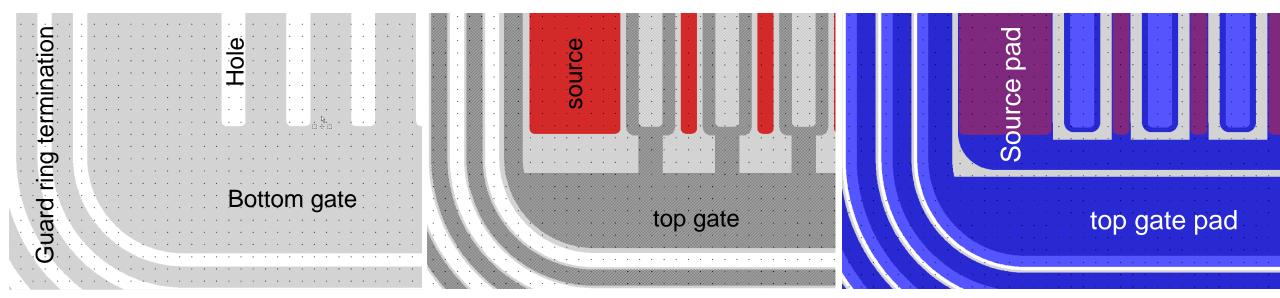

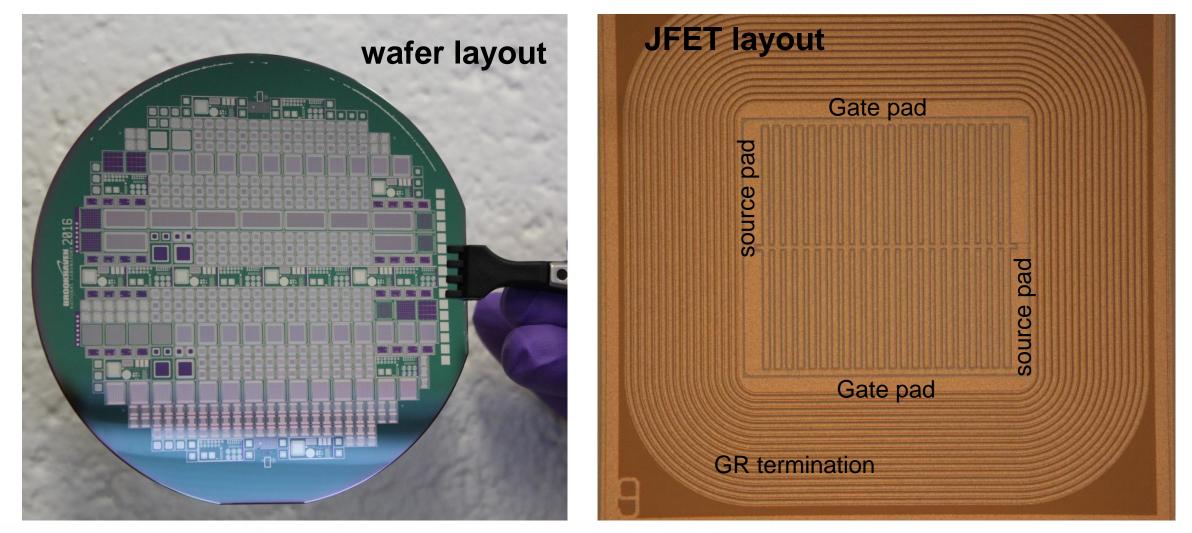

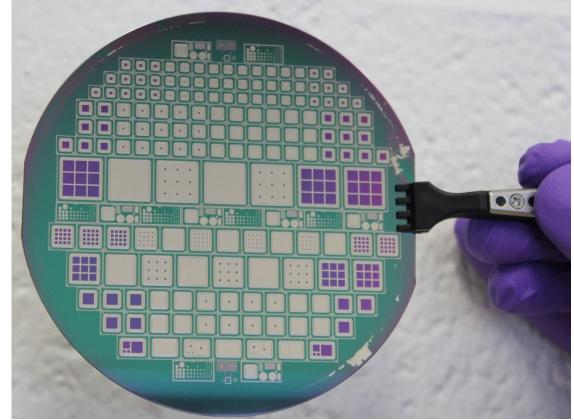

## The layout-1

#### 6 photolithographic masks, 4 implants.

Interdigitated design to increase the gate width and thus the ON current (especially after irradiation). The active area is 1x1 mm<sup>2</sup>, which sets the gate width to 20 cm. Triode configuration, top-gate connected to the bottom-gate.

Both *n*-type and *p*-type JFET, on 4" epitaxial wafers (TOPSIL): 50µm thick, N<sub>C</sub>~ 1e14cm<sup>-3</sup>.

#### The layout-2

Process splittings in the dose of the channel, mainly to fight the horn effect. Layout splittings in the width of the hole and in the length of the channel.

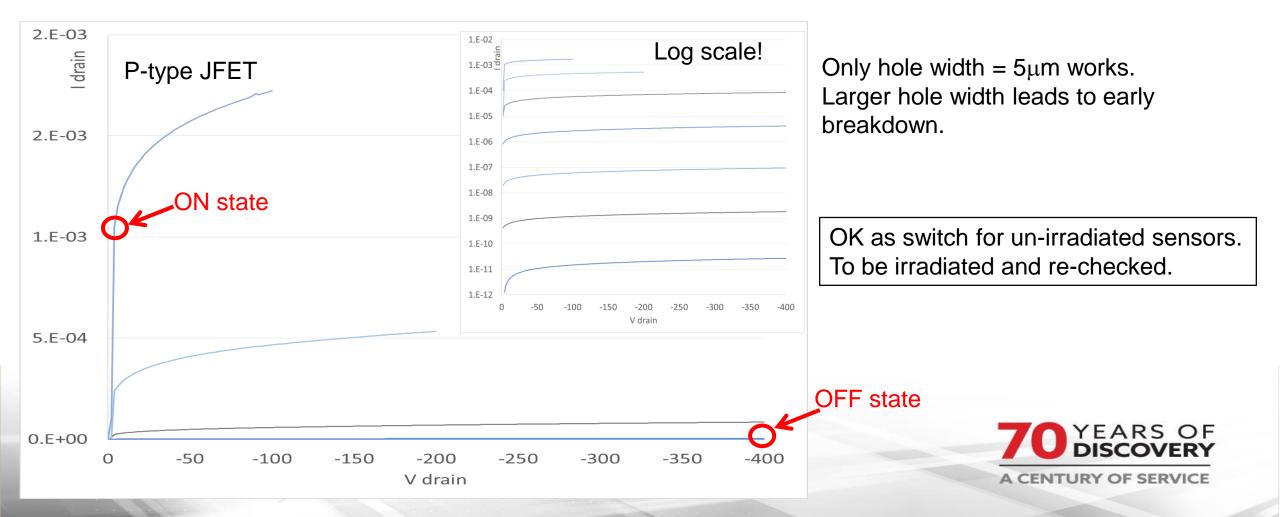

## IV characterization

- Lower channel doses feature a closed channel already at V<sub>gate</sub>=0 V (out of 4 wafers, 2 are OK).

- Higher Channel doses have lower V<sub>BD</sub>.

N-type HV JFETs have  $V_{BD}$  at 600V or 400V (for a channel dose of 6 and 8e12 cm<sup>-2</sup>, respectively) P-type HV JFETs have  $V_{BD}$  at 400V or 250V (for a channel dose of 5 and 7e12 cm<sup>-2</sup>, respectively)

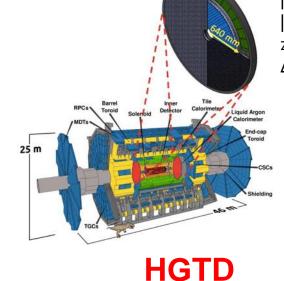

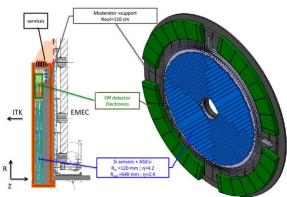

## Other on-going activities at BNL

## Silicon R&D: LGADs

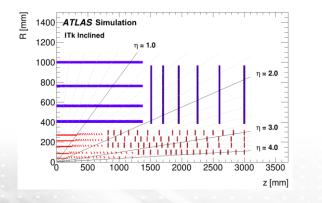

Microstrip for the Inner Tracker (ITk)

and High Granularity Timing Detector (HGTD) of ATLAS

$|\eta|>2.4$  (R=640mm)  $|\eta|<4.0$  (R=120mm) z=3500 mm  $\Delta z = 7.5$  cm

involved in testing LGADs fro

We are involved in testing LGADs from HPK and CNM, through TCT, CSA, fast current amplifier (SCIPP), and dedicated ALTIROC ASIC for the ATLAS HGTD.

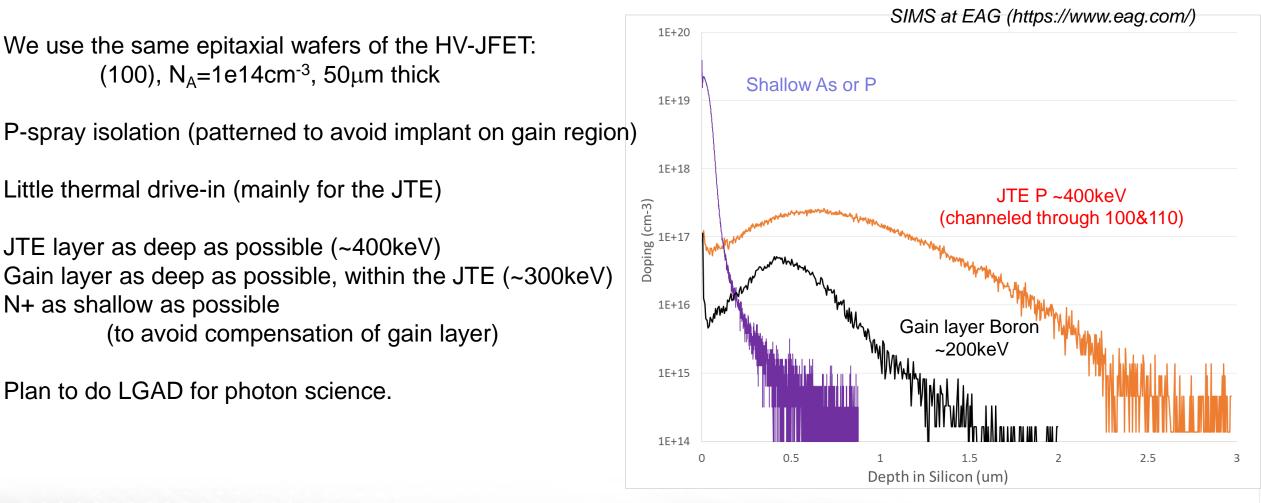

## 2- LGAD R&D

**70** YEARS OF DISCOVERY A CENTURY OF SERVICE

## 2- LGAD R&D

4" layout with 1x1 mm<sup>2</sup>, 2x2 mm<sup>2</sup>, 3x3 mm<sup>2</sup> and arrays.

First fabrication shows low leakage currents (< 1nA/cm<sup>2</sup>), high breakdown voltage but no gain, so need to tune the doping profiles.

New run expected to complete on June 2018.

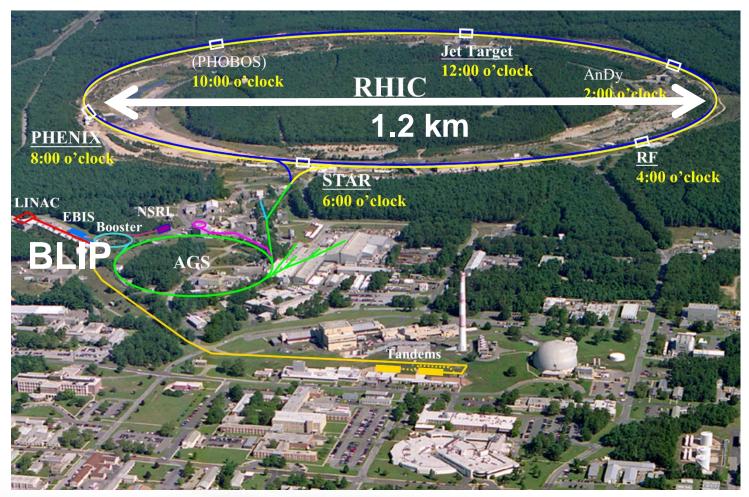

#### 3- Commissioning of BLIP as a new irradiation facility for silicon R&D

The Brookhaven Linac Isotope Producer (BLIP) consists of a beam line and target area for isotope production.

It uses protons up to 200 MeV and up to 110  $\mu A$  from the BNL Linac.

BLIP generally operates parasitically with the BNL nuclear physics program at the Relativistic Heavy Ion Collider (RHIC).

It produces certain commercially unavailable radioisotopes to distribute to the nuclear medicine community and industry (research to develop new radioisotopes desired by nuclear medicine investigators).

In coll. with James Kierstead, Nicolaos Simos (BNL), Keith Baker, Christian Weber (Yale University)

https://www.bnl.gov/cad/accelerator/

A CENTURY OF SERVICE

BLIP would be ideal for Si sensor irrad. as it can provide mmissioning of BLIP

- Both protons and neutrons

- Adjustable proton energies (65 MeV to 200 MeV) and currents (few  $\mu$ A to 110  $\mu$ A)

- Low cost

- Proximity to BNL Physics Dept.

We already received interest in BLIP from several collaborators

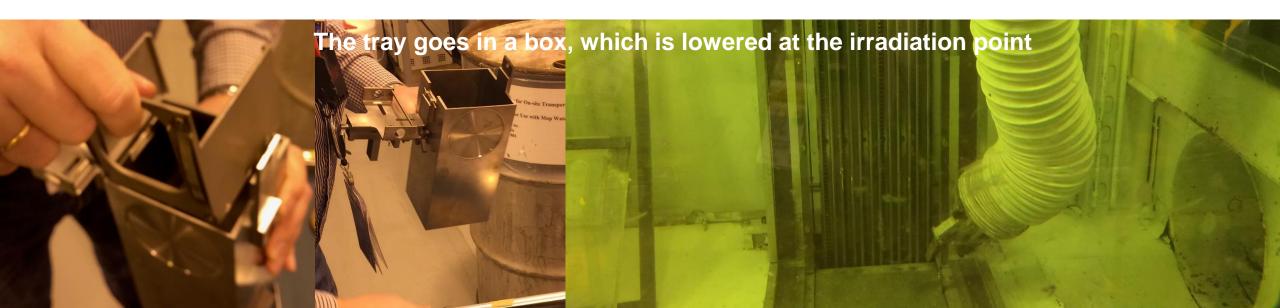

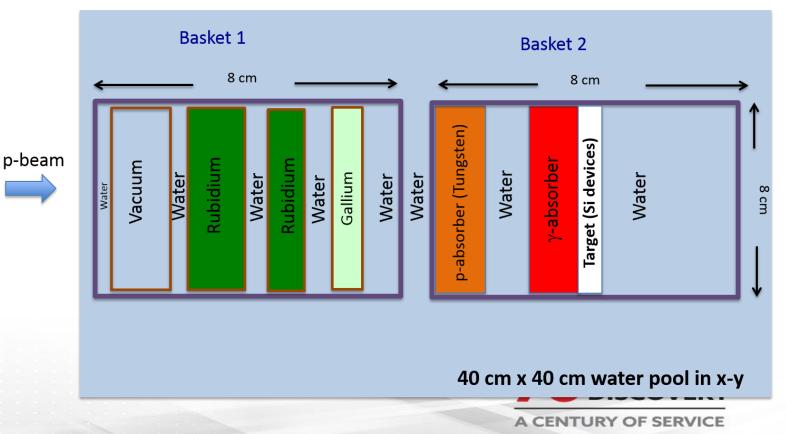

The samples are loaded down into a 9m deep well, water cooled. Two baskets along the beam:

- first (upstream) for proton irradiation,

- second (downstream) for spallation neutron irradiation. Runs parasitically to proton irradiation. Protons are absorbed in first basket and in additional absorber in II basket.

Gamma absorbed in II basket too.

Neutron Fluence is ~1e15 1-MeV n<sub>eq</sub>/cm<sup>2</sup>/hr.

- proton contamination during neutron irradiation of 1-10 Mrad/hr and negligible EM contamination (FLUKA simulations).

#### Conclusions

- Custom fabrication of not-standard devices

→ HV-JFET successful (still irradiation campaign to do)

- LGAD development, fabrication and testing

- Plans to have an irradiation facility in house

#### Post-doc position open at BNL:

https://inspirehep.net/record/1672347

Back up

#### Sensors are held in between two aluminum plates

#### The plates in a holder

#### A few plates fill up a tray