# From Chip Matrix to the 'Ideal Chip' for MPGD

Sorin Martoiu, CERN PH/DT

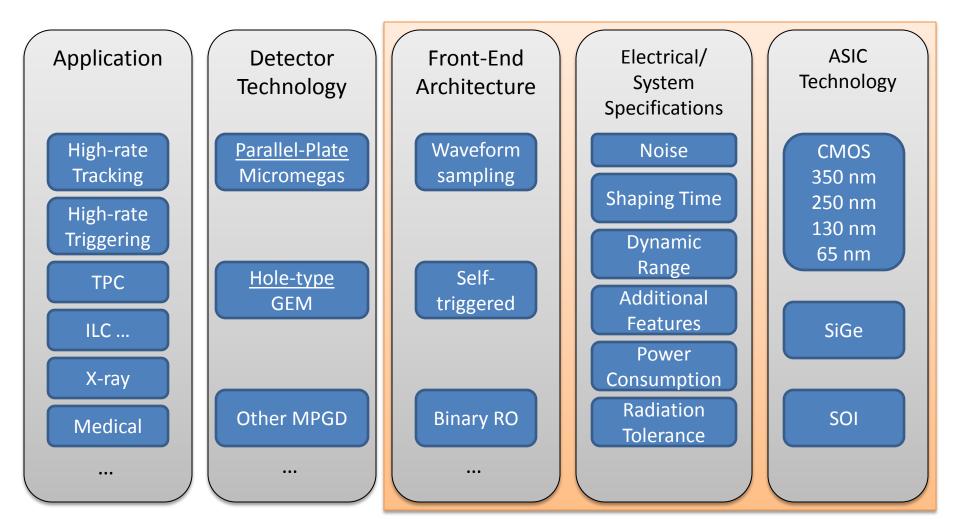

# "Ideal Chip" Specification

# Applications

- total rate = ... 25 kHz/mm<sup>2</sup>

- rate/channel = ?

- spatial resolution = 10 ... 100 um

- temporal resolution = 1 .. 25 ns

- energy resolution = ?

- efficiency = 95 ... 99 %

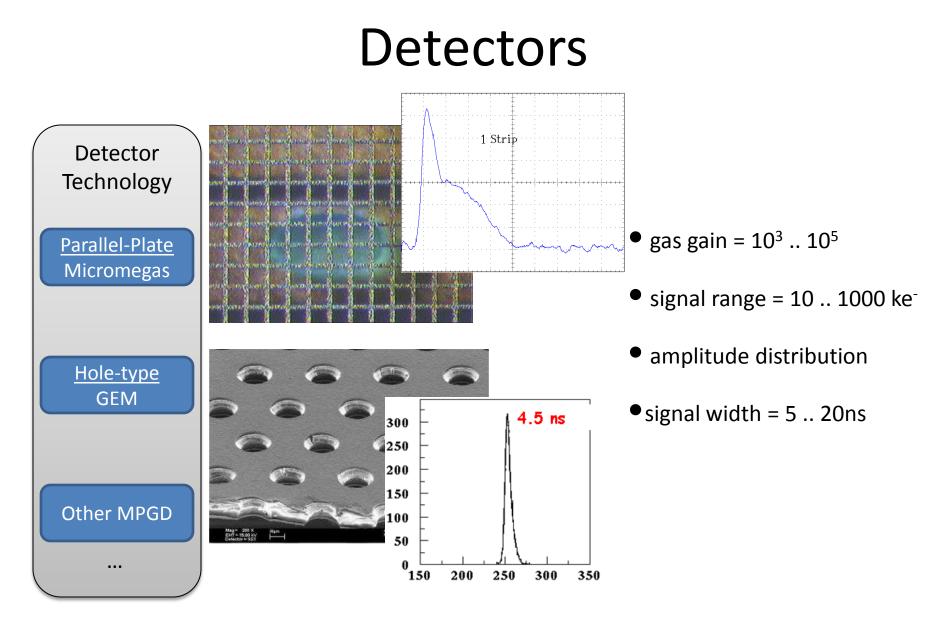

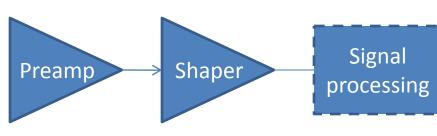

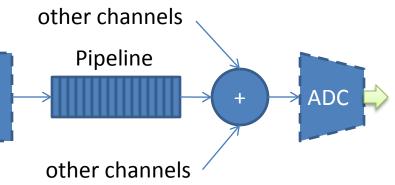

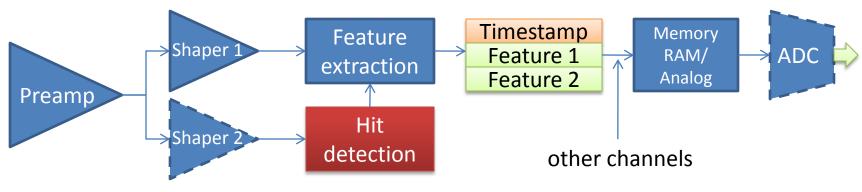

## **Front-End Architecture**

• Waveform sampling

Self-triggered channel

## **Front-End Architecture**

|                                                                                                               | Pros                                                                                                                                                                                                                                                               | Cons                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Waveform sampling<br>•analog: <i>APV25, Beetle</i><br>•binary: <i>VFAT</i><br>•digital: <i>(S)ALTRO, SVX4</i> | <ul> <li>simple (relatively)</li> <li>versatile</li> <li>off-line data processing <ul> <li>pile-up rejection/detection</li> <li>systematic error correction</li> <li>advanced feature</li> <li>extraction</li> </ul> </li> <li>data rate ~ trigger rate</li> </ul> | <ul> <li>high data/event</li> <li>readout time</li> <li>needs external trigger</li> <li>no zero-suppression</li> </ul>                                                                                 |

| Self-triggered channel<br>Example: MSGCROC                                                                    | <ul> <li>zero-suppression</li> <li>optimal data/event</li> </ul>                                                                                                                                                                                                   | <ul> <li>less versatile <ul> <li>pile-up rejection</li> <li>difficult</li> <li>limited off-line</li> <li>processing</li> </ul> </li> <li>data rate ~ event rate</li> <li>high R/O bandwidth</li> </ul> |

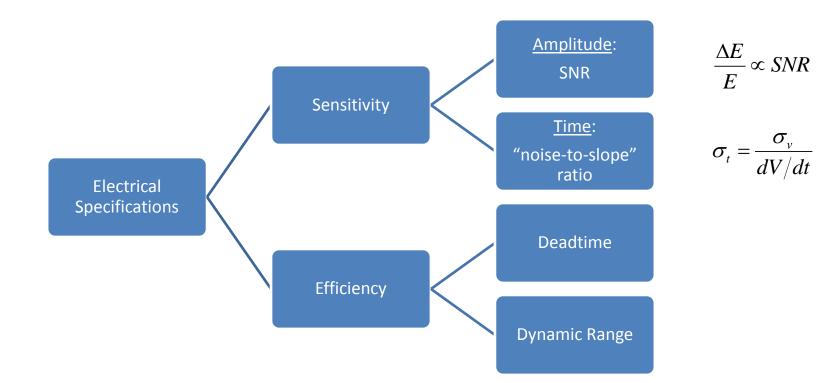

## **Electrical Specifications**

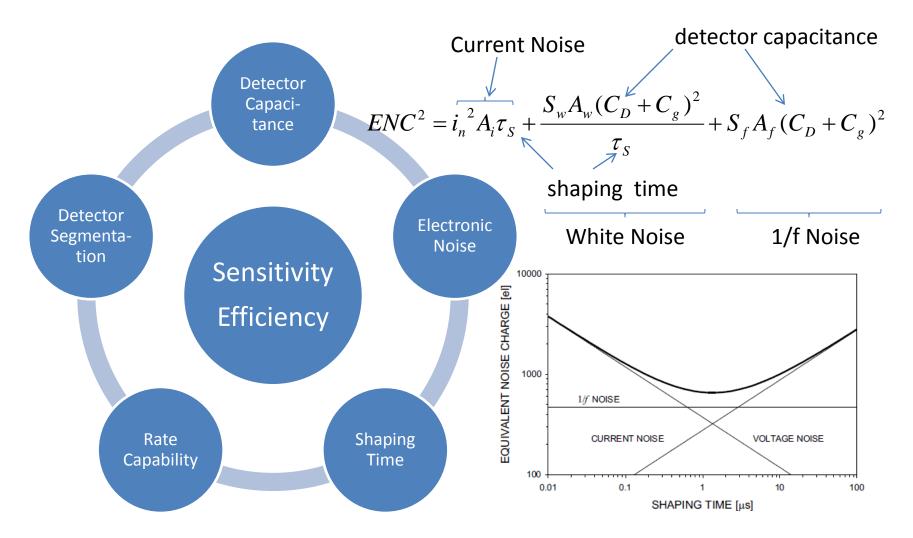

## Sensitivity vs. Efficiency

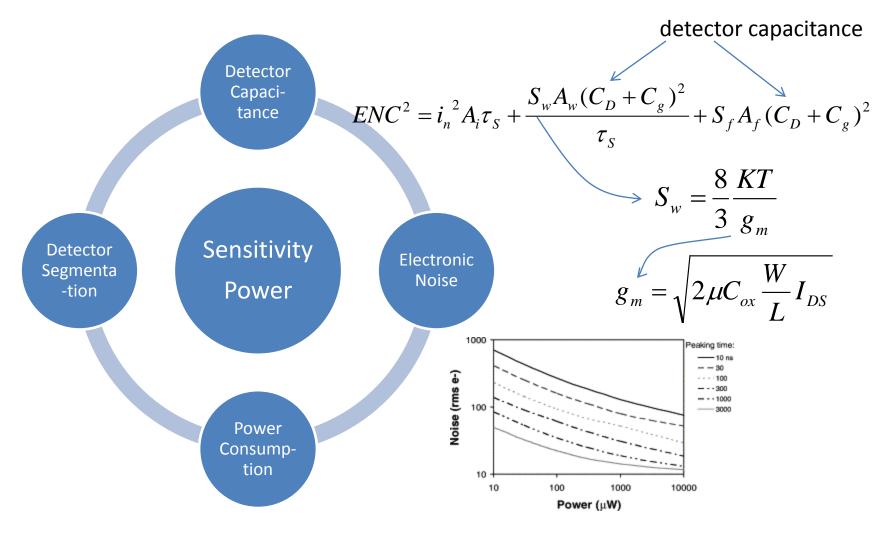

### Sensitivity vs. Power

## **Capacitive Matching**

• 1/f noise dominant

• white noise dominant

• No preamplifier can provide optimum noise performance for every detector

10

# Technology

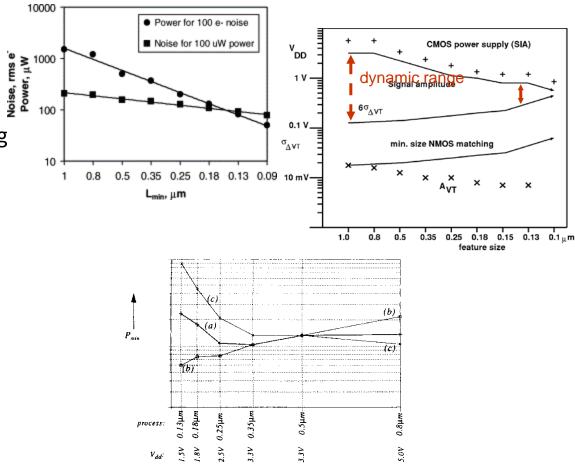

**CMOS** scaling

- better noise performance

- lower dynamic range

- optimum technology for analog design appears to be around the 0.25um node

- Digital circuits clearly benefit from scaling

- <u>Smaller ADCs</u>

- More powerful digital signal processing

- (Auto)calibration and error correction digital circuits could compensate the analog performance deficit

Fig. 8. Minimum power consumption for a voltage follower circuit (with constant topology, SINAD and maximum signal frequency). (a) Made in various processes, operated at their corresponding supply voltages. (b) Made in various processes, all operated at  $V_{dd} = 3.3$  V. (c) All made in 0.5- $\mu$ m CMOS, operated at various supply voltages.

### Features

#### Chip matrix

| Name           | Exp                                                                                                                                                                                                                          | Det          | #ch | Shaper<br>(ns)                 | Noise                        | Range<br>(fC) | Pol. | ADC  | f<br>(MHz)    | P/ch.<br>(mW)  | Feat.         | Tech              | Rad<br>hard |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------------------------|------------------------------|---------------|------|------|---------------|----------------|---------------|-------------------|-------------|

| APV25          | CMS                                                                                                                                                                                                                          | Si strip     | 128 | 50                             | 270+38e/pF                   | 20            | both | A    | 40            | 2.7            | PD, PR        | 0.25<br>CMOS      | 10          |

| AFTER          | T2K                                                                                                                                                                                                                          | TPC          | 72  | 100-2000<br>s-gauss            | (350-1800) +<br>(22-1.8)e/pF | 19            | both | А    | 1-50<br>(100) | 7.5            | VG,VS         | 0.35<br>CMOS      | no          |

| MSGCROC        | DETNI                                                                                                                                                                                                                        | Gas<br>strip | 32  | T: 25<br>E: 85                 | 2000e @<br>40pF              | 800           | both | A,1  | 2ns<br>TDC    |                | VG, ZS        | 0.35<br>CMOS      | no          |

| Beetle         | LHCb                                                                                                                                                                                                                         |              | 128 | 25                             | 500+50e/pF                   | 17.5          | both | A/1  | 40            | 5.2            | F-OR          | 0.25<br>CMOS      | 40          |

| VFAT           | тотем                                                                                                                                                                                                                        |              | 128 | 22                             | 650+50e/pF                   | 18.5<br>(cal) | both | 1    | 40            | 4.47           | F-OR          | 0.25<br>CMOS      | 50          |

| NINO           | ALICE                                                                                                                                                                                                                        | TPC          | 8   | 1                              | 1900+165/pF                  | 2000          | both | 1    | async         | 30             | BR            | 0.25<br>CMOS      | no          |

| CARIOCA        | LHCb                                                                                                                                                                                                                         | MWPC         | 8   | <15 @<br>220pF                 | 2000+40e/pF                  | 250           | both | 1    | async         | 46             | BR            | 0.25<br>CMOS      | 20          |

| PASA+<br>ALTRO | ALICE<br>TPC                                                                                                                                                                                                                 | TPC          | 16  | 190 <sub>fwhm</sub><br>s-gauss | 570e @20 pF                  | 160           | both | 10   | 20            | < 40           | BC, TC,<br>ZS | 0.35,0.25<br>CMOS |             |

| SVX4           | CDF,<br>D0                                                                                                                                                                                                                   | Si strip     | 128 | 100-360                        | 410+45e/pF                   | 60fC          | neg  | 8    | 106<br>(212)  | 2              | ZS            | 0.25<br>CMOS      | 20          |

| SPIROC         | ILC,<br>T2K                                                                                                                                                                                                                  | SiPM         | 36  | A:25-175<br>T: 10              | A: 1/11pe;<br>T:1/24pe       | 2000<br>pe    | neg  | 8-12 | 100ps<br>TDC  | 0.025<br>pulse |               | 0.35 <u>SiGe</u>  | no          |

| Legend:        | PD = peak detection, PR = pile-up rejection, VG = variable gain, VS = variable shaping, F-OR = fast-OR, BR = baseline restorer, BC = baseline correction, TC = tail correction, DC = data compression, ZS = zero suppression |              |     |                                |                              |               |      |      |               |                |               | R =               |             |

- ✓ fast-OR,

- ✓ variable gain,

- ✓ variable shaping,

- ✓ peak detection

- ✓ pile-up rejection,

- ✓ baseline restorer,

- ✓ baseline correction,

- ✓ tail correction,

- ✓ data compression,

- ✓ zero suppression

# From Chip Matrix to the Ideal Chip

| Name           | Ехр                                                                                                                                                                                                                          | Det          | #ch | Shaper<br>(ns)                 | Noise                        | Range<br>(fC)  | Pol. | ADC  | f<br>(MHz)    | P/ch.<br>(mW)  | Feat.         | Tech              | Rad<br>hard |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------------------------|------------------------------|----------------|------|------|---------------|----------------|---------------|-------------------|-------------|

| APV25          | CMS                                                                                                                                                                                                                          | Si strip     | 128 | 50                             | 270+38e/pF                   | 20             | both | A    | 40            | 2.7            | PD, PR        | 0.25<br>CMOS      | 10          |

| AFTER          | T2K                                                                                                                                                                                                                          | TPC          | 72  |                                | (350-1800) +<br>(22-1.8)e/pF | 19             | both | A    | 1-50<br>(100) | 7.5            | VG,VS         | 0.35<br>CMOS      | no          |

| MSGCROC        | DETNI                                                                                                                                                                                                                        | Gas<br>strip | 32  | T: 25<br>E: 85                 | 2000e @<br>40pF              | 800            | both | A,1  | 2ns<br>TDC    |                | VG, ZS        | 0.35<br>CMOS      | no          |

| Beetle         | <u> LНСЬ</u>                                                                                                                                                                                                                 |              | 128 | 25                             | 500+50e/pF                   | 17.5           | both | A/1  | 40            | 5.2            | F-OR          | 0.25<br>CMOS      | 40          |

| VFAT           | тотем                                                                                                                                                                                                                        |              | 128 | 22                             | 650+50e/pF                   | 18.5<br>(cal)  | both | 1    | 40            | 4.47           | F-OR          | 0.25<br>CMOS      | 50          |

| NINO           | ALICE                                                                                                                                                                                                                        | TPC          | 8   | 1                              | 1900+165/pF                  | 2000<br>th<100 | both | 1    | async         | 30             | BR            | 0.25<br>CMOS      | no          |

| CARIOCA        | LHCb                                                                                                                                                                                                                         | MWPC         | 8   | <15 @<br>220pF                 | 2000+40e/pF                  | 250            | both | 1    | async         | 46             | BR            | 0.25<br>CMOS      | 20          |

| PASA+<br>ALTRO | ALICE<br>TPC                                                                                                                                                                                                                 | TPC          | 16  | 190 <sub>fwhm</sub><br>s-gauss | 570e @20 pF                  | 160            | both | 10   | 20            | < 40           | BC, TC,<br>ZS | 0.35,0.25<br>CMOS |             |

| SVX4           | CDF,<br>D0                                                                                                                                                                                                                   | Si strip     | 128 | 100-360                        | 410+45e/pF                   | 60fC           | neg  | 8    | 106<br>(212)  | 2              | ZS            | 0.25<br>CMOS      | 20          |

| SPIROC         | ILC,<br>T2K                                                                                                                                                                                                                  | SiPM         | 36  | A:25-175<br>T: 10              | A: 1/11pe;<br>T:1/24pe       | 2000<br>pe     | neg  | 8-12 | 100ps<br>TDC  | 0.025<br>pulse | dual-<br>gain | 0.35 <u>SiGe</u>  | no          |

| Legend:        | PD = peak detection, PR = pile-up rejection, VG = variable gain, VS = variable shaping, F-OR = fast-OR, BR = baseline restorer, BC = baseline correction, TC = tail correction, DC = data compression, ZS = zero suppression |              |     |                                |                              |                |      |      |               |                |               |                   |             |

- shaping time: 5ns .. 1us

- dynamic range: <100fC

- power: < 10 mW/ch (?)

- ADC accuracy: 10 bits (?)

- TDC accuracy: 1ns

•••

We need an **APV25** chip with <u>variable gain and shaping time</u> like the **AFTER** chip, <u>dynamic range</u> like **MSGCROC**, integrated <u>fast-OR</u> like **Beetle**, <u>integrated ADC</u> like **SVX4**, <u>digital signal processor</u> like **ALTRO**