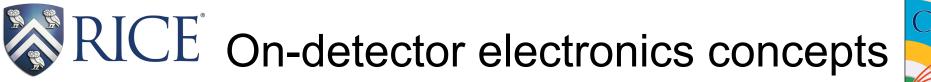

## IpGBT modules (aka Port Cards)

#### Ted Nussbaum, Karl Ecklund (Rice)

Mechanical design from Yadira's recent design models (~mid-May) Some connected thoughts on e-link cables from port card perspective (past year)

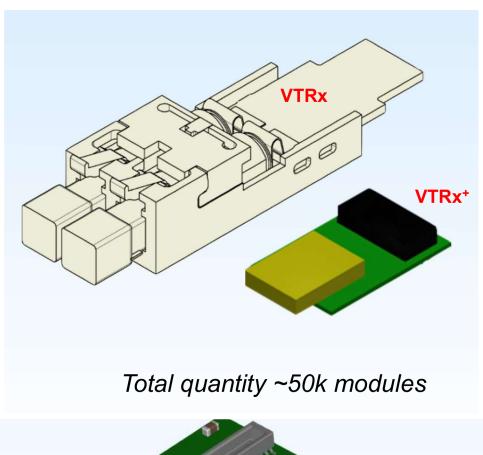

# RICE Electrical & Optical components

- Jointly developed for ATLAS & CMS

- CERN, FNAL, Oxford, SMU

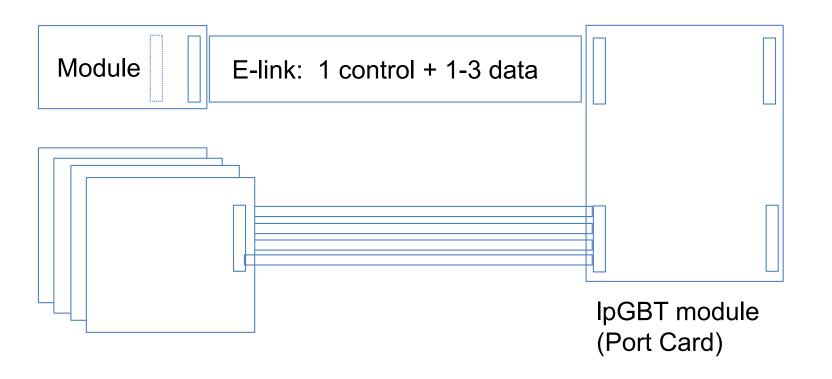

- Versatile Link+ System

- Optical components for front end and back end electronics

- VTRx+ Optical Module

- 1 Rx (2.5 Gbps) up to 4 Tx (5/10 Gbps)

- Low profile packaging

- Plugable Electrical connection

- Fiber connector or pigtails

- Radiation qualified

- TID: 1 MGy (explore up to 2 MGy)

- $\circ$  Fluence: 1E15 n /cm<sup>2</sup>

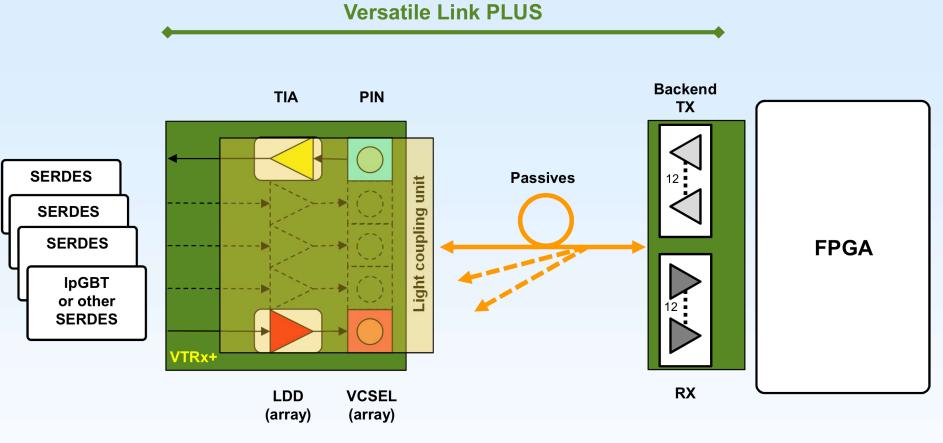

- IpGBT Low power GigaBit Transceiver

- ASIC for electrical / optical

- 5.12/10.24 Gbps data links & 2.56 Gbps control link

- E-port concept: 7 \* 1.28 Gbps uplinks; 8 \* 160 Mbps downlinks

- o Other configurations possible (e.g. lower speeds, more links)

- E-links might be flex cables (baseline) or possibly twisted pairs

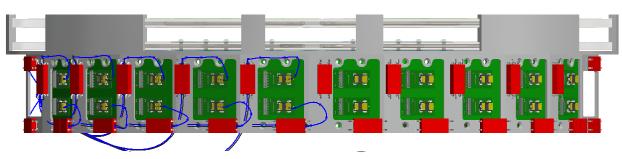

- IpGBT module (Port Card) has two IpGBT & VTRx+ as baseline (other variants might be considered) and is DC-DC powered

- IpGBT modules are mounted on a frame at outer radius of service cylinder

- TFPX (& maybe TEPX) can be integral component of Dee + portcard frame = cartridge

- TBPX has similar port card frames mounted between downstream disks

- Requires longer e-links from ladder to port card locations

### Versatile Link

On-Detector Custom Electronics & Packaging Radiation Hard Up to 4Tx plus 1Rx *Off-Detector* Commercial Off-The-Shelf (COTS) on-board 12Tx, 12Rx module

- Downlink 2.5 Gbps & Uplink 10 Gbps

- E-ports : multiplexed Tx channels 7 @ 1.28 Gbps; 8 @ 160 Mbps (+ other speeds)

- Phases all adjustable (no Delay25 equivalent needed)

- Link protocol includes Forward Error Correction (FEC5, FEC12)

- Radiation tolerant 200 MRad

- For data links electrical receiver has optional 100 ohm termination built in

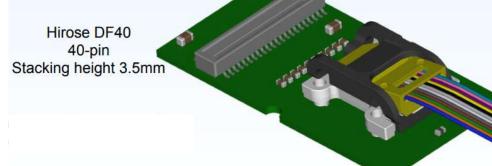

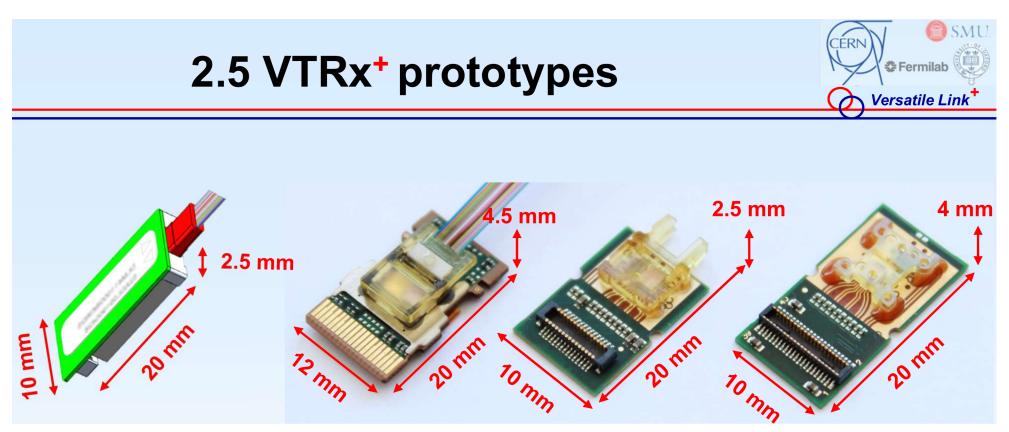

## VTRx+ Optical Module

- Evolution of VTRx based on SFP duplex fiber TRx package

- Developed for phase 1 upgrades

- VTRx+ has a smaller form factor

- (Also higher speed)

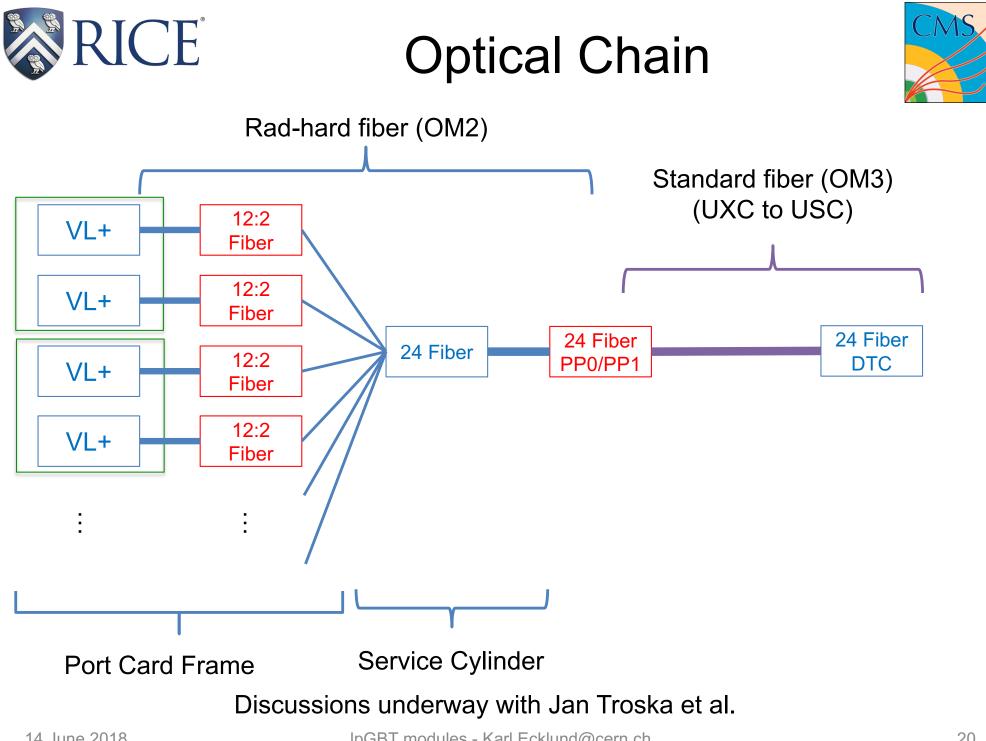

- Note use of 12 fiber ribbon connection, either low profile connector or pigtail

- Compact, lower mass

- Prototypes developed & tested

- Expect to be available for user evaluation & development end of 2018

- IpGBT on a similar timescale

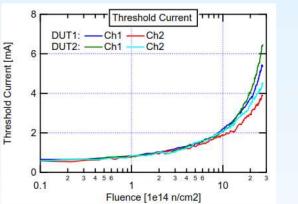

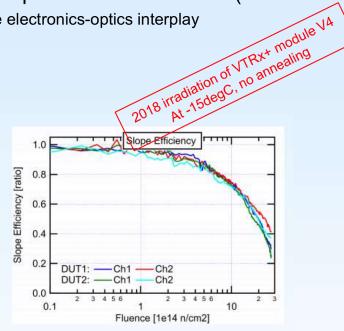

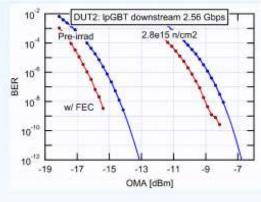

### 2.6 The VTRx<sup>+</sup> performance challenge

Maintaining performance over Temperature and Lifetime (i.e. radiation) is challenging

- requires in-depth understanding of the electronics-optics interplay

- Optimization on-going to gain margin

- full module results shown below

- Tx (-15degC)

CERN

Fermilab

Versatile Link

• Rx (-15degC, GaAs PIN)

14 June 2018

lpGBT modules - Karl.Ecklund@cern.ch

8

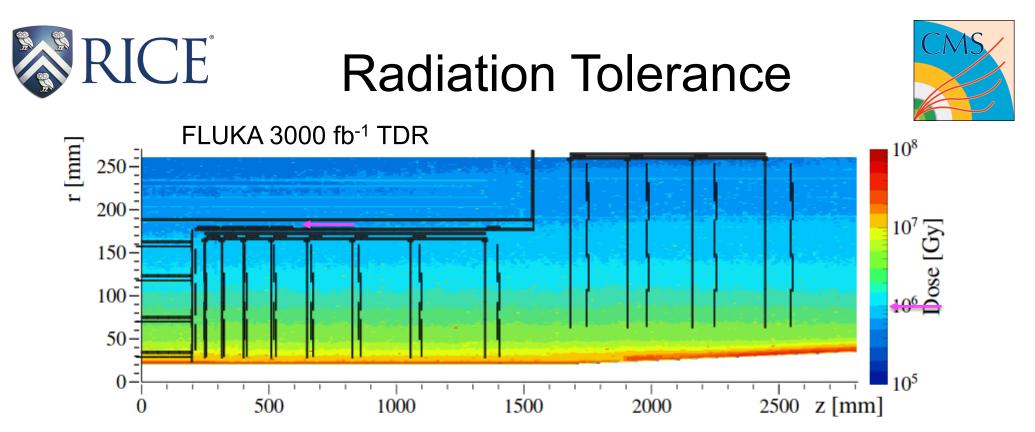

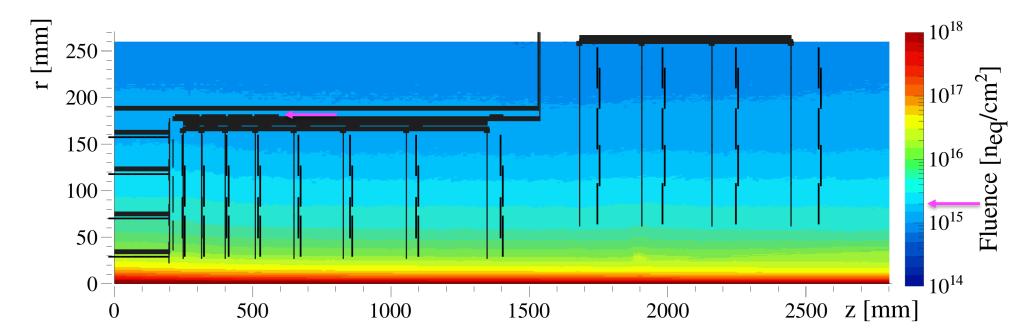

- Up to 1E15 n/cm<sup>2</sup> fluence and 1 MGy (100 MRad)

- The laser transmitters VCSELs are sensitive

- Drove thinking about placing opto-hybrids at outer radius of TFPX disks in TDR and subsequent design work; highest radius available

- Note TBPX links can be put in the same location

- Dose expected at 16 cm : ~1 MGy

- Fluence at 16 cm : ~2E15

- VTRx optical modules need to be replaceable during YETS

- Does will be lower for TEPX safely(?) below 1 MGy

### **Fluence Prediction**

#### FLUKA 3000 fb<sup>-1</sup> TDR

- For each IpGBT ASIC / VL+ optical link we aim to use

- Up to 7\*1.28 Gbps electrical data links from modules

- Up to 7 electrical control/command links

- Each Module uses 1 down link and 1–6 data links

- Data link counting relies on data "compression" in ROC

- Compression can be clustering & local address scheme (studies ongoing)

- In TDR studies a factor ~2 would be needed over RD53A protocol

- Mount IpGBT PCBs in half ring frames inside service cylinder

- Two IpGBT ASICs VL+ optoTRx per IpGBT module / port card

- E-link cables between modules and IpGBT module can have up to 6 uplinks and as many as 4 down links (serving <=4 modules)</li>

- L1 1x2 module has 6 up links and one control link

- TEPX modules have 1 up link/1 control link up to 7 per lpGBT

- Looks possible to use same module connector and e-link pin definition for all modules / IpGBT modules

- Up to 6 data links and 4 control links on a e-link cable ; unused pairs at IpGBT module can be left unconnected

# RICE IPGBT Module / Port Card

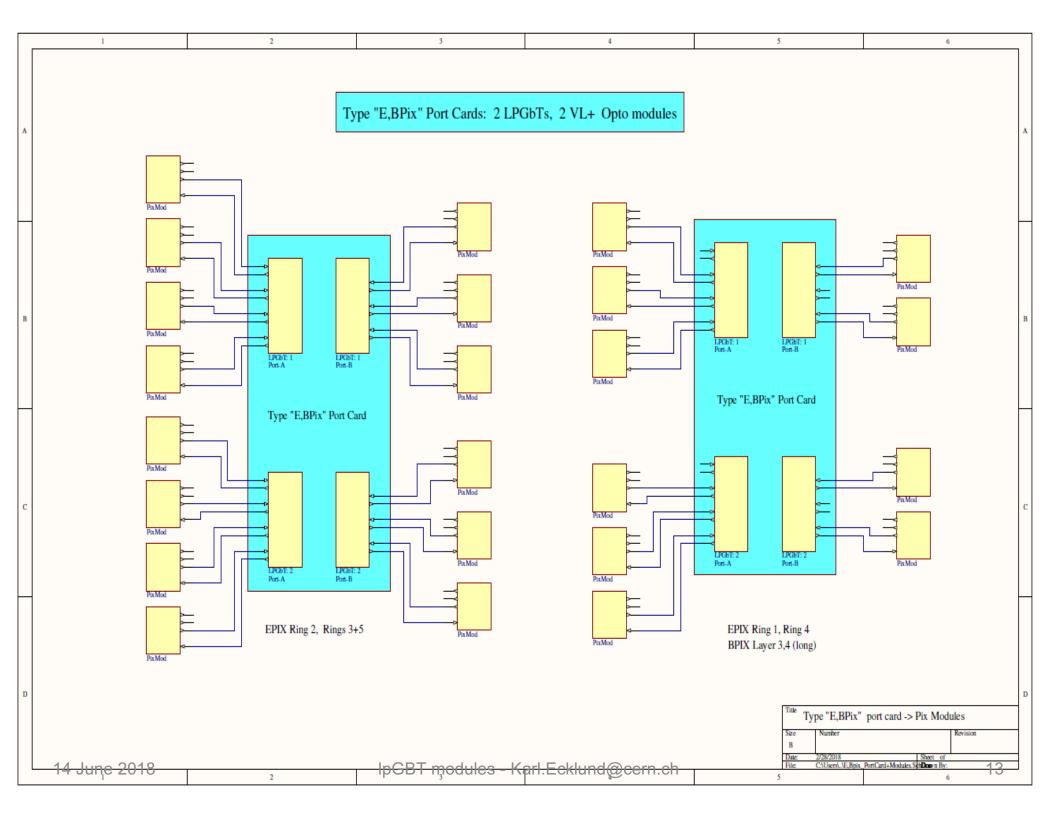

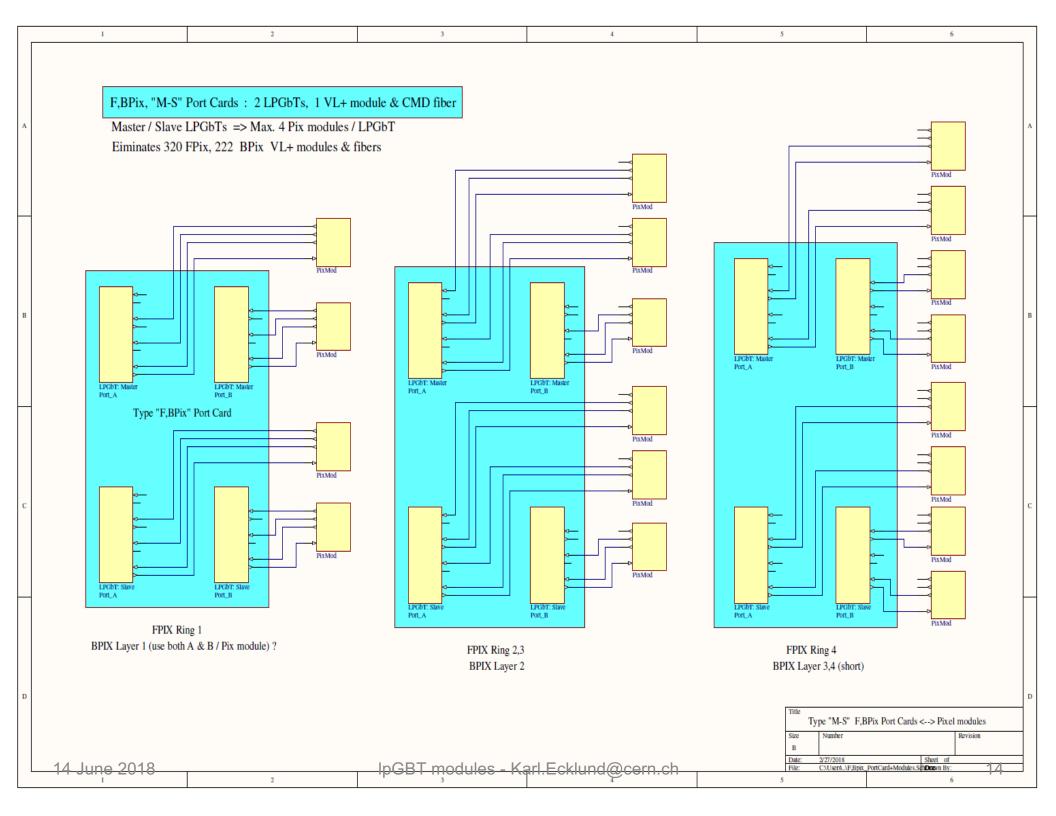

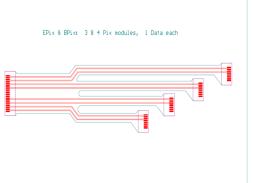

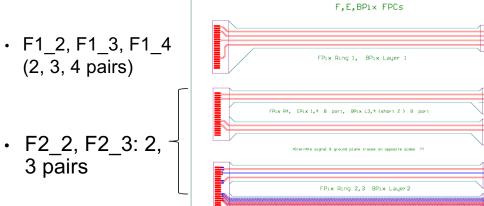

#### F,E,BPix FPCs

#### EPix & BPix: 3 & 4 Pix modules, 1 Data each

| KU<br>THE UNIVERSITY OF<br>KANSAS                             | TFPX FPC C<br>6x2 lengths = 12                               | Des      | sig     | n F  | -la           | VO       | rs         |

|---------------------------------------------------------------|--------------------------------------------------------------|----------|---------|------|---------------|----------|------------|

|                                                               | F,E,BPi× FPCs                                                | TFPX     |         |      |               |          |            |

| • F1_2, F1_3, F1_4                                            | 5100                                                         |          | Uplinks | \$   |               |          |            |

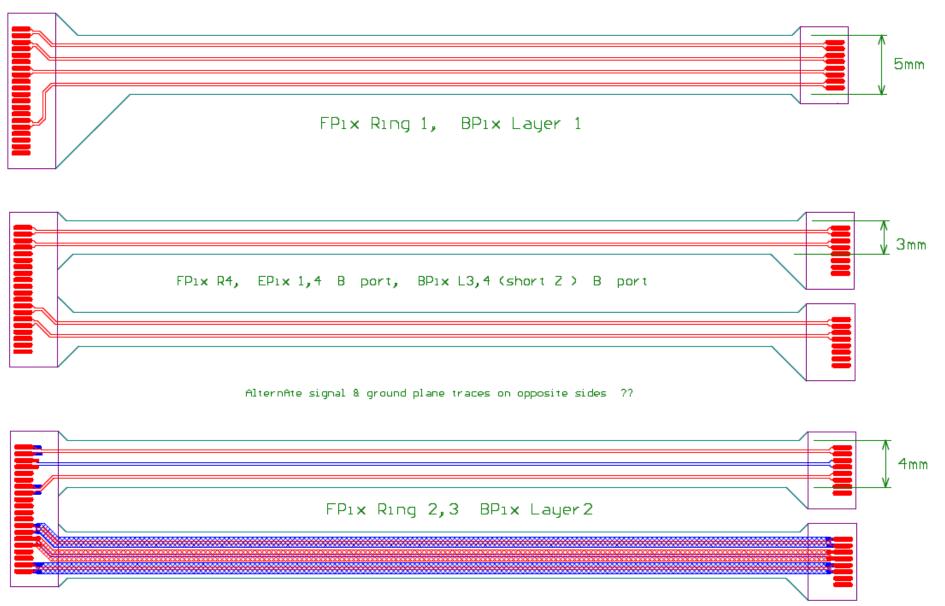

| (2, 3, 4 pairs)                                               | FPix Ring 1, BPix Layer 1                                    | Portcard | Ring    | #mod | links/m<br>od | tot link | Flav.      |

|                                                               | FPix R4, EPix 1,4 B port, BPix L3,4 (short Z ) B port        |          | R1      | 2    | 3             | 6        | F1_4       |

| • F2_2, F2_3: 2,<br>3 pairs                                   |                                                              |          | R1      | 2    | 3             | 6        | F1_4       |

|                                                               | riternitie signal 8 ground plane traces on opposite sides 77 |          | R1      | 1    | 3             | 3        | F1_4       |

|                                                               | FPix Ring 2,3 BPix Layer2                                    |          | R3      | 3    | 2             | 6        | F2_3, F1_3 |

|                                                               |                                                              |          | R3      | 3    | 2             | 6        | F2_3, F1_3 |

|                                                               |                                                              | - 1      | R1      | 2    | 3             | 6        |            |

|                                                               | EPix 8 BPix: 3 8 4 Pix modules, 1 Data each                  |          | R1      | 2    | 3             | 6        |            |

|                                                               |                                                              |          | R1      | 1    | 3             | 3        |            |

|                                                               |                                                              |          | R3      | 3    | 2             | 6        |            |

| • F4_2: 2 pairs                                               |                                                              |          | R3      | 3    | 2             | 6        |            |

|                                                               |                                                              |          | R2      | 3    | 2             | 6        | F2_3, F1_3 |

|                                                               |                                                              |          | R2      | 3    | 2             | 6        | F2_3, F1_3 |

|                                                               |                                                              |          | R2      | 2    | 2             | 4        | F2_3       |

|                                                               |                                                              |          | R4      | 4    | 1             | 4        | F2_2       |

| Reminder:                                                     |                                                              |          | R4      | 4    | 1             | 4        | F2_2       |

|                                                               |                                                              |          | R2      | 3    | 2             | 6        |            |

| <ul> <li>Each port card has max of four connectors</li> </ul> |                                                              |          | R2      | 3    | 2             | 6        |            |

|                                                               |                                                              |          | R2      | 2    | 2             | 4        |            |

| <ul> <li>Each module reacher</li> </ul>                       | equires one downlink                                         |          | R4      | 4    | 1             | 4        |            |

| 14 June 2018                                                  | lpGBT modules - Karl.Ec                                      | klund@c  | en a.ch | 4    | 1             | 4        |            |

5mm

📒 🕽 3mm

• F4\_2: 2 pairs

| <ul> <li>F2_2, F2_3: 2,<br/>3 pairs         </li> </ul> | Filternfile signal & ground plane traces on opposite sides 77 |

|---------------------------------------------------------|---------------------------------------------------------------|

| ·                                                       | FPix Ring 2,3 BPix Layer2                                     |

|                                                         |                                                               |

|                                                         |                                                               |

|                                                         |                                                               |

| ТЕРХ         |         |      |               |             |                  |  |

|--------------|---------|------|---------------|-------------|------------------|--|

| Portcar<br>d | Uplinks |      |               |             |                  |  |

|              | Ring    | #mod | links/<br>mod | tot<br>link | Flav.            |  |

|              | R1      | 5    | 1             | 5           | F4_2, F1_2       |  |

|              | R1      | 5    | 1             | 5           | F4_2, F1_2       |  |

|              | R3+R5   | 7    | 1             | 7           | F4_2, F2_2, F1_2 |  |

|              | R3+R5   | 7    | 1             | 7           | F4_2, F2_2, F1_2 |  |

|              | R3+R5   | 7    | 1             | 7           | F4_2, F2_2, F1_2 |  |

|              | R1      | 5    | 1             | 5           |                  |  |

|              | R1      | 5    | 1             | 5           |                  |  |

|              | R3+R5   | 7    | 1             | 7           |                  |  |

|              | R3+R5   | 7    | 1             | 7           |                  |  |

|              | R3+R5   | 7    | 1             | 7           |                  |  |

|              | R2      | 7    | 1             | 7           | F4_2, F2_2, F1_2 |  |

|              | R2      | 7    | 1             | 7           |                  |  |

|              | R4      | 5    | 1             | 5           | F4_2, F1_2       |  |

|              | R4      | 5    | 1             | 5           |                  |  |

|              | R2      | 7    | 1             | 7           |                  |  |

|              | R2      | 7    | 1             | 7           |                  |  |

|              | R4      | 5    | 1             | 5           |                  |  |

|              | R4      | 5    | 1             | 5           |                  |  |

(2, 3, 4 pairs)

# **RICE** Links per sub-detector

| QUARTER OF IT |                      | Multiplicity<br>(#ladders,<br>#disks) | #modules per<br>ladder/ half ring | #Links<br>per<br>module | Total #Links<br>(short)       | Total #Links<br>(long) |  |

|---------------|----------------------|---------------------------------------|-----------------------------------|-------------------------|-------------------------------|------------------------|--|

| тврх          | L1                   | 6                                     | 4 (short)/ 5 (long)               | 6                       | 144                           | 180                    |  |

|               | L2                   | 14                                    | 4 (short)/ 5 (long)               | 2                       | 112                           | 140                    |  |

|               | L3                   | 12                                    | 4 (short)/ 5 (long)               | 1                       | 48                            | 60                     |  |

|               | L4                   | 16                                    | 4 (short)/ 5 (long)               | 1                       | 64                            | 80                     |  |

|               | SUM                  |                                       |                                   |                         | 368                           | 460                    |  |

|               |                      |                                       |                                   |                         | Total #Links for N*half disks |                        |  |

| TFPX          | R1                   | 8                                     | 10                                | 3                       | 240<br>256<br>192             |                        |  |

|               | R2                   | 8                                     | 16                                | 2                       |                               |                        |  |

|               | R3                   | 8                                     | 12                                | 2                       |                               |                        |  |

|               | R4                   | 8                                     | 16                                | 1                       | 128                           |                        |  |

|               | SUM                  |                                       |                                   |                         | 816                           |                        |  |

| ТЕРХ          | R1                   | 4                                     | 20                                | 1                       | 80                            |                        |  |

|               | R2                   | 4                                     | 28                                | 1                       | 112                           |                        |  |

|               | R3                   | 4                                     | 18                                | 1                       | 72                            |                        |  |

|               | R4                   | 4                                     | 20                                | 1                       | 80                            |                        |  |

|               | R5                   | 4                                     | 24                                | 1                       | 96                            |                        |  |

|               | SUM                  |                                       |                                   |                         | 440                           |                        |  |

|               | Quarter of TBPX+TFPX |                                       |                                   | 1184                    | 1276                          |                        |  |

|               | Quarter of TEPX      |                                       |                                   | 440                     |                               |                        |  |

| Quarter of IT |                      |                                       | 1624                              | 1716                    |                               |                        |  |

| One end of IT |                      |                                       |                                   | 3248                    | 3432                          |                        |  |

| Entire IT     |                      |                                       |                                   | 6680                    |                               |                        |  |

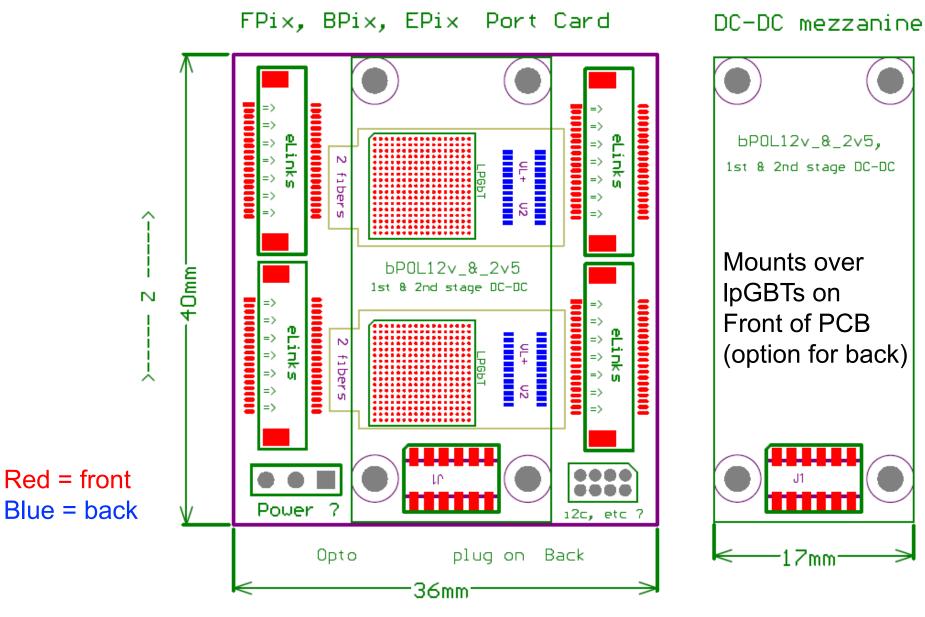

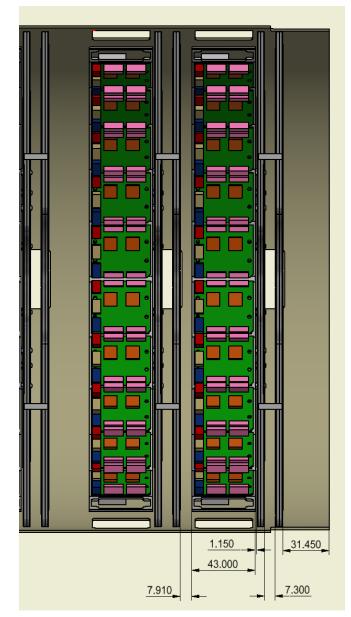

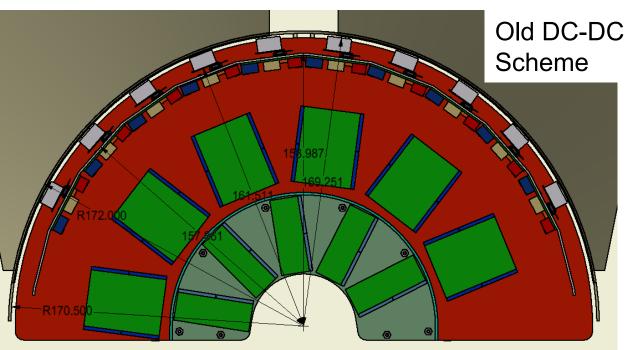

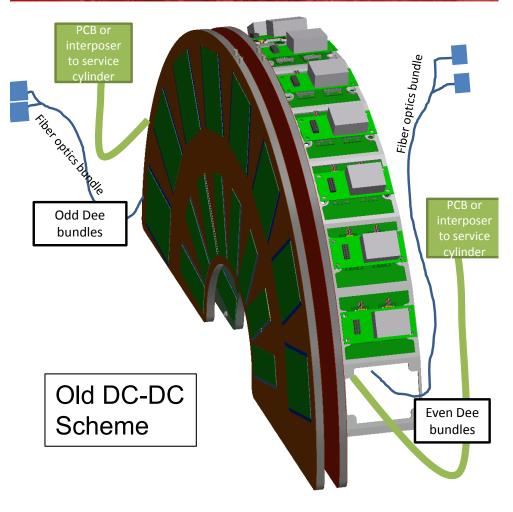

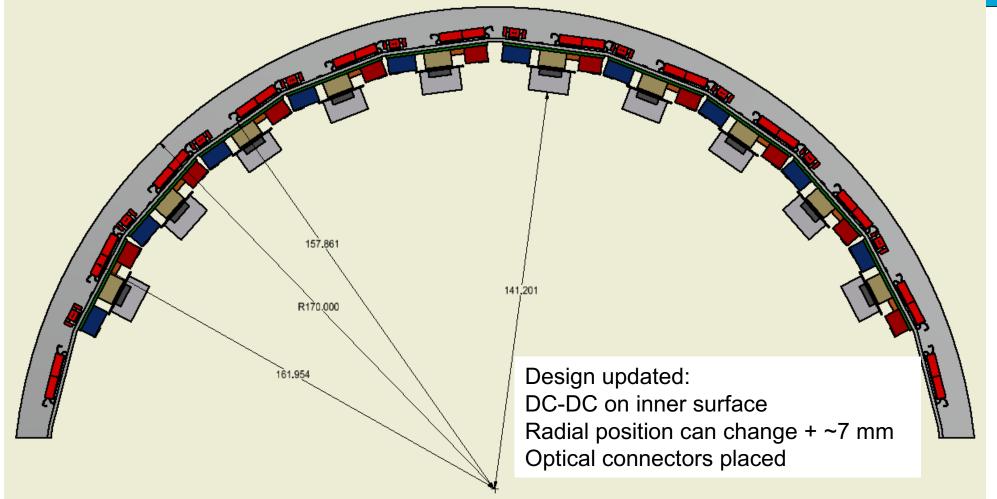

### **TFPX** Disks

- Dimensions of port card set by

- circumference and number required

- Space available between disks (Z)

- Size of VL+, IpGBT, DC-DC inductors

- Initial design 36 mm x 40 mm

- Puts DC-DC on mezzanine card

- Revisit when layout of card starts lpGBT modules - Karl.Ecklund@cern.ch

TFPX half disks and port cards mounted together

Power, cooling, fibers connect in two locations

Modular design

- Speeds assembly (& repairs)

- Factorizes testing

https://indico.cern.ch/event/709649/

### Cartridge system

Bordlemay Padilla

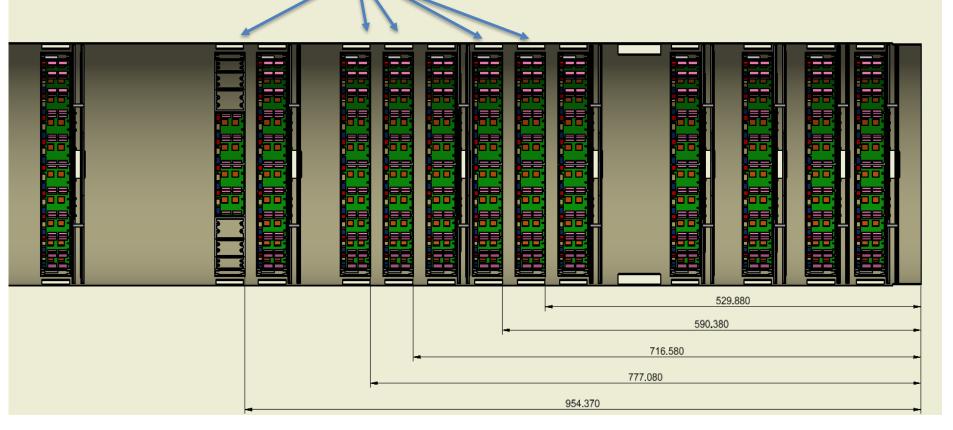

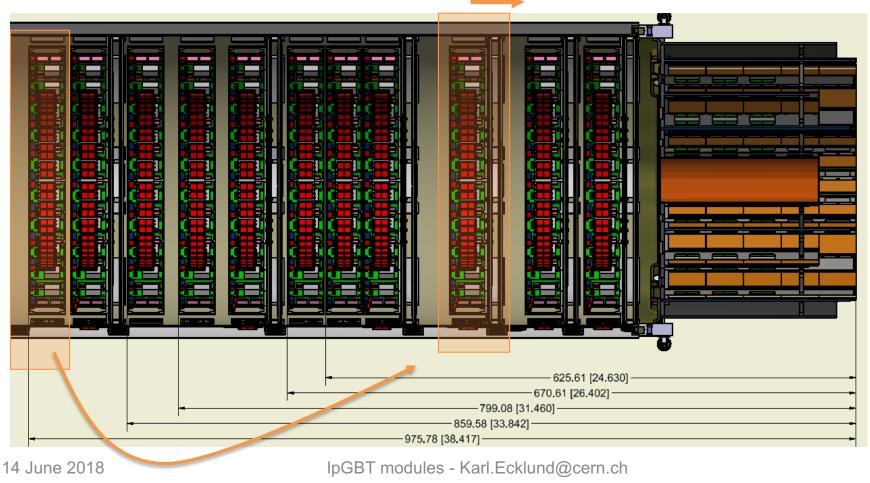

BPIX Port Cards can fit between disks in some locations

IP

There is enough room for Port Card Frames within 1 m of from of service cylinder Cables from barrel (right) would terminate on connector board on outer cylinder that routes to BPIX port cards (extra connection, but simple connection to frame) Recent work at Cornell to optimize location of TBPX port cards by nudging disks... 14 June 2018 IpGBT modules - Karl.Ecklund@cern.ch 23

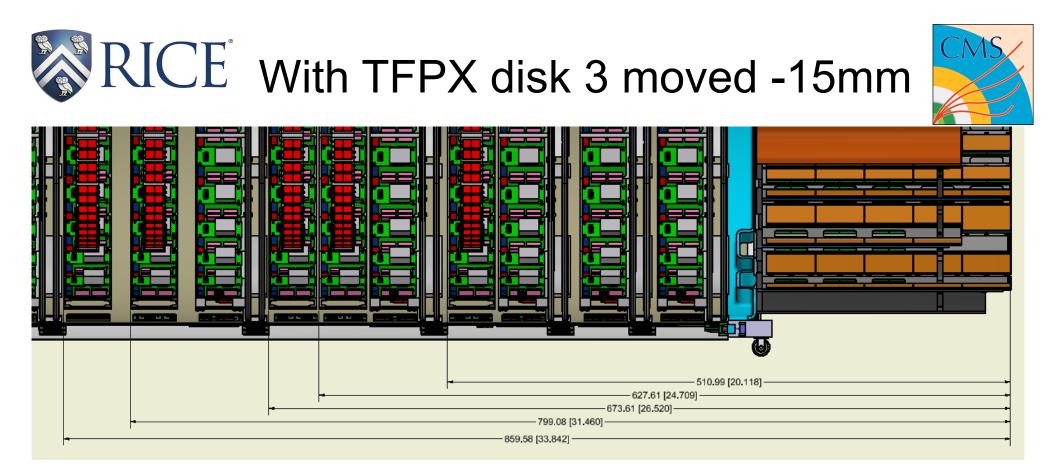

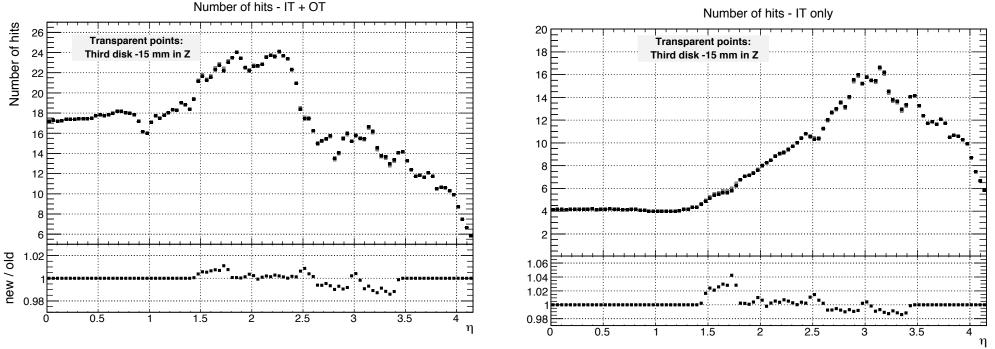

- Attempt to move last frame closer by nudging TFPX disk 3 by -15mm to make room

- Would reduce length of e-links for barrel

- Fully packed longest distance reduced by ~12cm

- Helpful for e-link length (1.5 cm shift for 12 cm)

- To be seen if there is enough clearance

- Mockup being made this summer

- Impact on physics studied and found minimal

- Number of hits vs  $\eta$  changes by few% wrt baseline

# RICE TFPX/TBPX Port Card Frame

Design :

DC-DC on inner surface Radial position may change +10 mm Optical connectors placed

E-link connectors on inner surface DC-DC on inner surface Opto modules and fiber connectors on outer surface (2 lit fibers per VL+ on 12 fiber ribbon) fan in to 24 fiber connector

# **RICE** Summary of Recent Updates

- Recent work is on integration

- Fiber connectors moved out to larger radius

- Keep VL+ optical TRx outward in r for radiation reasons

- DC-DC mezzanines mount inward in r

- BPIX port card locations & TPFX disk "nudging"

- Details also given by Yadira in the mechanics meeting May TK week

- For the IpGBT board itself

- IpGBT pinout now available, but warning of changes to come before chip submission: waiting on submission before pushing layout

- $\circ~$  (Meanwhile Ted is working on irradiation / test adapter boards for sensor irradiation)

- Settled on DC-DC mezzanine on inner radius side of port card

- Ted has started winding & testing inductors for DC-DC

- One sample bPol12V mounted on test board for tests

- Still looks possible to serve TEPX, TFPX, TBPX with the same lpGBT module / port card or modified versions with same electrical design to optimize layout for mechanical reasons

## To DC-DC or not?

- We might consider dropping the DC-DC and just bring enough power fort port cards directly.

- Baseline (TDR) plan had DC-DC to reduce ohmic losses on power cables

- Follows the OT module design where IpGBT is powered by DC-DC (with everything else)

- Two voltages

- $_{\circ}$  IpGBT is 65 nm and needs 1.2 V

- $_{\odot}$  VTRx+ needs 2.5 V for VCSEL

- Not that much power

- Estimate (to update) is a few Watts

- TDR says 1.2 kW for 1260 lpGBT (no DC-DC efficiency here?)

- lpGBT <750mW, VTRx+ <??? mW (10 mA laser bias ~25 mW)</li>

####

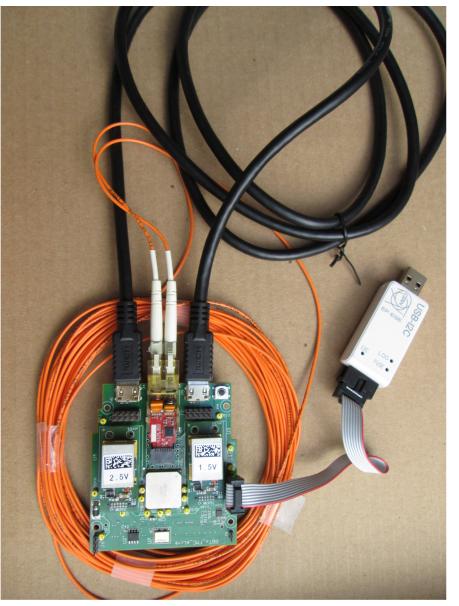

Ted made a test Board using GBT parts

(Spring/summer 2017)

Works with basic PRBS test mode Control via I2C Interface to GBT test Board (CERN)

Not much use in Further tests

- Lower speed

- Different protocols

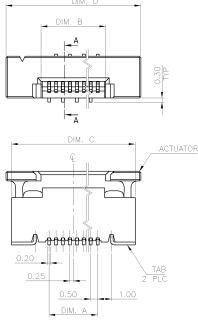

# Connectors

- Looking for glass filled thermoplastic materials

- <u>AMP : 2-1734742-0</u> •

- Locking rely solely on friction of the fingers inside the connector to hold the cable

- The bale mechanically locks the cable Hirose

- FH12-20S-0.5SVA(54)

• FH40-20S-0.5SV

- DF40HC(3.5)-40DS-0.4V(51) •

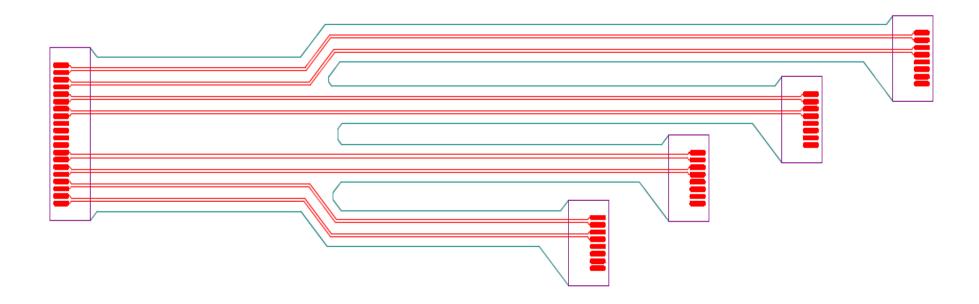

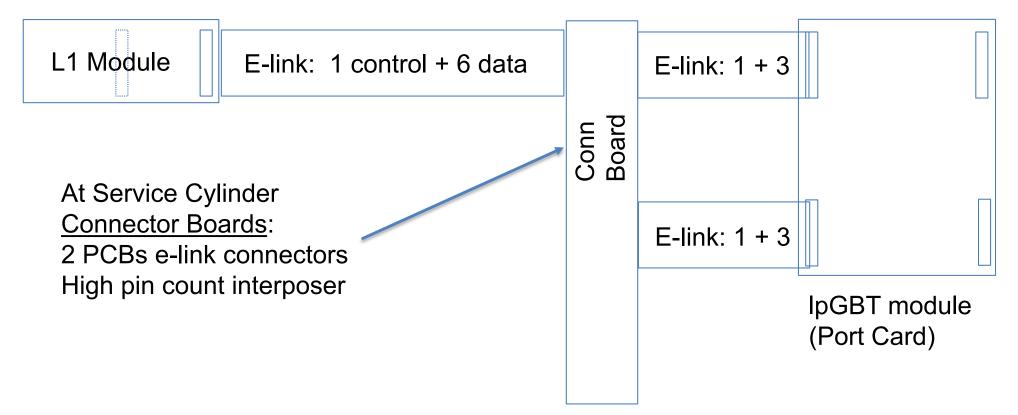

## Note on TBPX E-links

- Layer 1 modules have two ROCs and 6 data links

- May use two 3+1 cables (space?)

- But can also change from 6+1 to 2\*(3+1) at connector board

- Connector boards thin in r, outside of service cylinder

- Allows connections for BPIX e-links in two (?) places each port card frame

## Move of disk 3

- Andre Frankenthal (Cornell) studied in tkLayout

- <u>http://home.fnal.gov/~as2872/layoutsDefault/ThirdDoubleDiskZ\_Baseline</u>

- <u>http://home.fnal.gov/~as2872/layoutsDefault/ThirdDoubleDiskZ\_Moved</u>

- Impact on # hits at the few% level

- Resolutions are also affected at the few% level in the region of disk3

- Details at links above see also simulation meeting

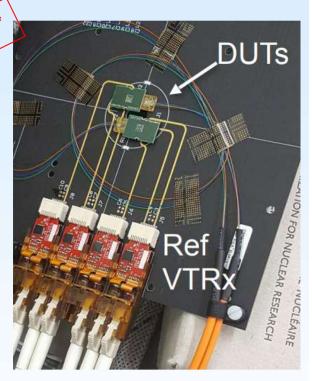

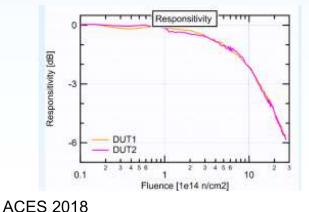

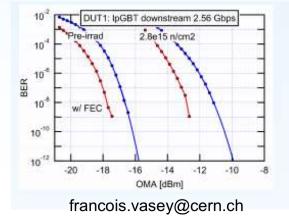

VersaLink+ Links

- OptoLinks (VL+, VTRx+ lpGBT) at ACES

2018 (Francois Vasey)

- <u>VL+ at TWEPP 2017</u> (Jan Troska)

- LpGBT e-space