PAUL SCHERRER INSTITUT

**Physik-Institut**

**EPIX** portcard

Lea Caminada

EPIX/FPIX Workshop 14 June 2018

## **EPIX Services**

- Geometry of EPIX services different than FPIX services

- phi segments vs half cylinder

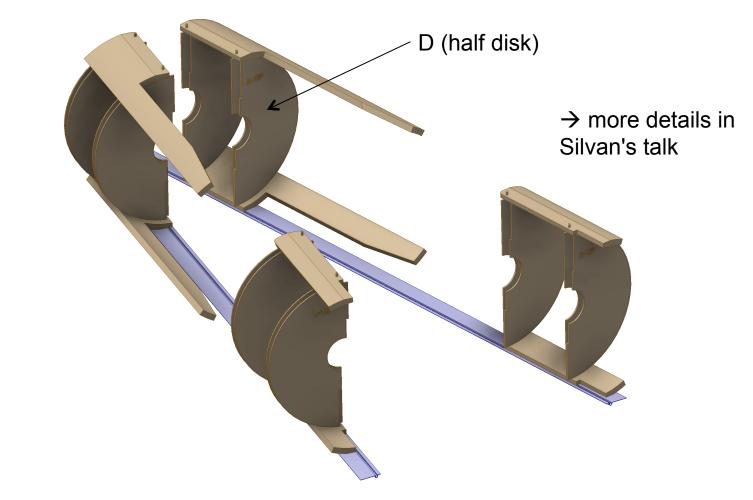

- EPIX consists of 8 mechanical units with 2 Ds (half-disks) each

- aim for common design of portcard for all Ds

# **EPIX Services per D**

- Based on module arrangement presented in Wolfram's talk

- Compared to TDR design

- Fewer numbers of modules (and therefore elinks)

- Same number of IpGBT (but less modules per IpGBT)

- Larger bandwith for innermost ring (1 elink for 1 chip instead of 2)

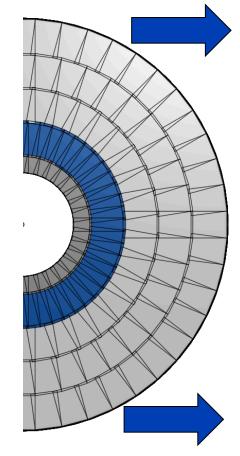

- Services for each D in two slots (top and bottom)

- 2 portcards per disk

|                    | Ring 1 | Ring 2 | Ring 3 | Ring 4 | Ring 5       | Total |

|--------------------|--------|--------|--------|--------|--------------|-------|

| #Modules           | 18     | 26     | 18     | 20     | 24           | 106   |

| #ROCs              | 18     | 52     | 72     | 80     | 96           | 318   |

| #elinks            | 18     | 26     | 18     | 20     | 24           | 106   |

| #lpGBT             | 4      | 4      | 6*     | 4      | *with Ring 3 | 18    |

| #modules/<br>lpGBT | 4.5    | 6.5    | 7      | 5      |              | 5.9   |

## **EPIX Services per D**

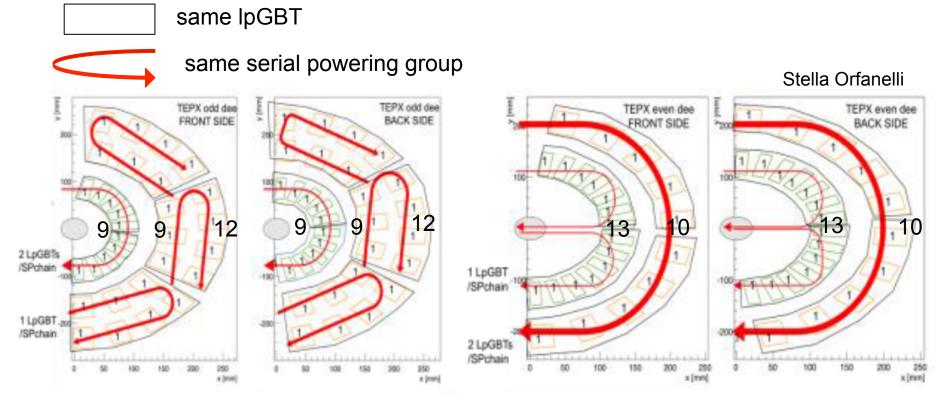

Connection scheme follows TDR layout

- 2 portcards per D:

- elink: 1 up/1 down link per module  $\rightarrow$  106 differential pairs per portcard

- elink length up to 30-40cm

- 9 IpGBT/VL per portcard

- 1 elink connector per IpGBT  $\rightarrow$  connecting to 4-7 modules

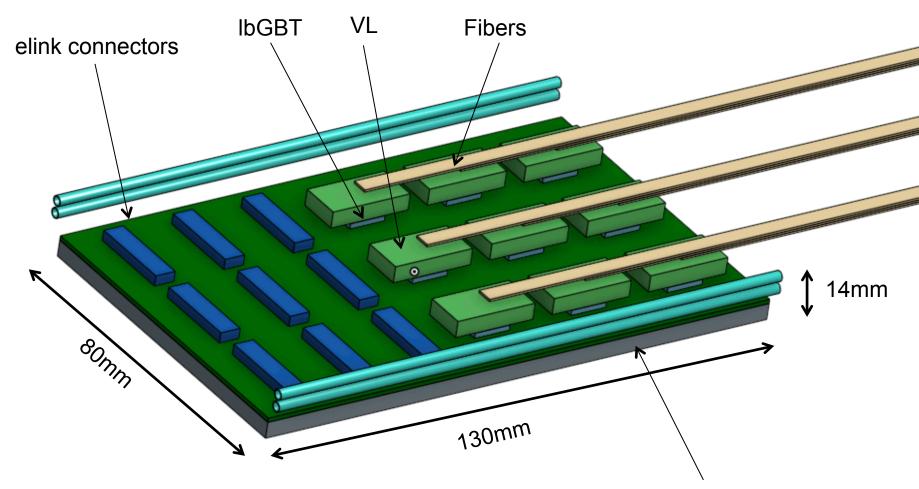

## How the portcard could look like

Next steps

Power lines

- Placement of module/lpGBT connectors: outside/inside?

- Placement of power lines, connectors?

- Elink design?

## **Powering of portcard**

- TDR scheme based on 2 DCDC converters  $(11V \rightarrow 2.55V \rightarrow 1.25V)$

- Is direct powering an option?

- Assuming one cable per portcard (powering 9 lpGBT/VL)

|       |         | Length<br>[m] | xsec<br>[mm²] | I[A] | Vin[V] | Vout[V] | Power<br>loss<br>[W] |

|-------|---------|---------------|---------------|------|--------|---------|----------------------|

| IpGBT | PS-PP1  | 85            | 3.5           | 5.4  | 8      | 3.6     | 24                   |

|       | PP1-PP0 | 6             | 0.7           | 5.4  | 3.6    | 2.0     | 8                    |

| VL    | PS-PP1  | 85            | 1.4           | 1.1  | 6      | 3.8     | 2.4                  |

|       | PP1-PP0 | 6             | 0.7           | 1.1  | 3.8    | 3.5     | 0.3                  |

- Power loss for one EPIX quadrant: 280 W (compared to 740W for detector power)

- Cable cross section for one EPIX quadrant:

- 80mm<sup>2</sup> (compared to 670mm<sup>2</sup>) for PS-PP1

- 23mm<sup>2</sup> (compared to 280mm<sup>2</sup>) for PP1-PP0

- Is there an option that fits within service constraints?

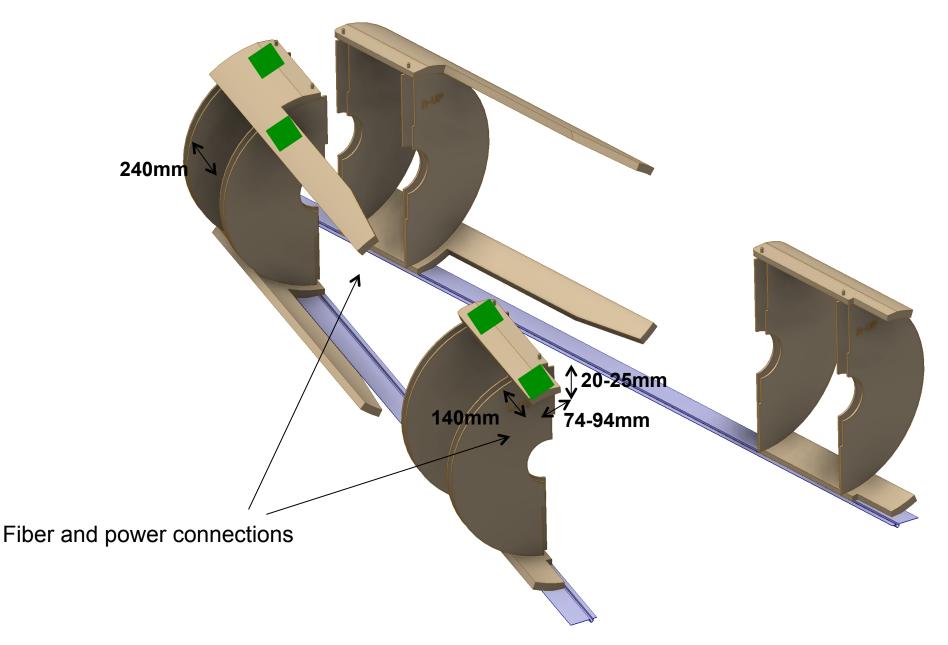

## Where the portcard could be placed

## Backup

## 1x1

#### Advantages

- Smaller number of modules/ROCs per disk

- Reduced number of elinks per disk

- Increased elink bandwidth for innermost ring

- (Fewer number of modules per IpGBT)

- Increased minimal distance between modules on same disk → space for wirebonding

### At the cost of

Additional module type (Note however that 1x1 modules are already in the planning for sensor/module R&D)

|--|

**EPIX** CHIP MODULE RO rate RO Elink #chips Modul RO 1.28 Elink Occupancy per 1.28 in Mbps Occup е Gbps Links module per for Gbps ancy modul Rate per module 750KHz Links e Mbps per per chip chip 0.5 R1 lowCol 348 54% 1 881 1 69% R1\_highCol 83% 533 0.5 1 0.5 32% 1 475 1 37% R2 lowCol 206 R2\_highCol 269 0.5 42% 1 167 0.25 52% 2 688 R3 lowCol 1 54% R3 highCol 177 0.25 55% 2 1 R4 lowCol 121 0.25 38% 2 518 40% R4 highCol 138 0.25 43% 2 R5 lowCol 102 0.25 32% 2 442 1 119 0.25 37% R5\_highCol 2

from IT service document