### Inner Tracker DTC requirements & specifications

Tulika Bose, Eric Hazen, **Deborah Pinna** (Boston University)

> Zeynep Demiragli (MIT)

EPIX/FPIX workshop

UZH/PSI, 14-15 June 2018 16 March 2018

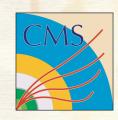

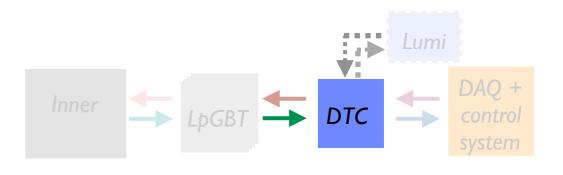

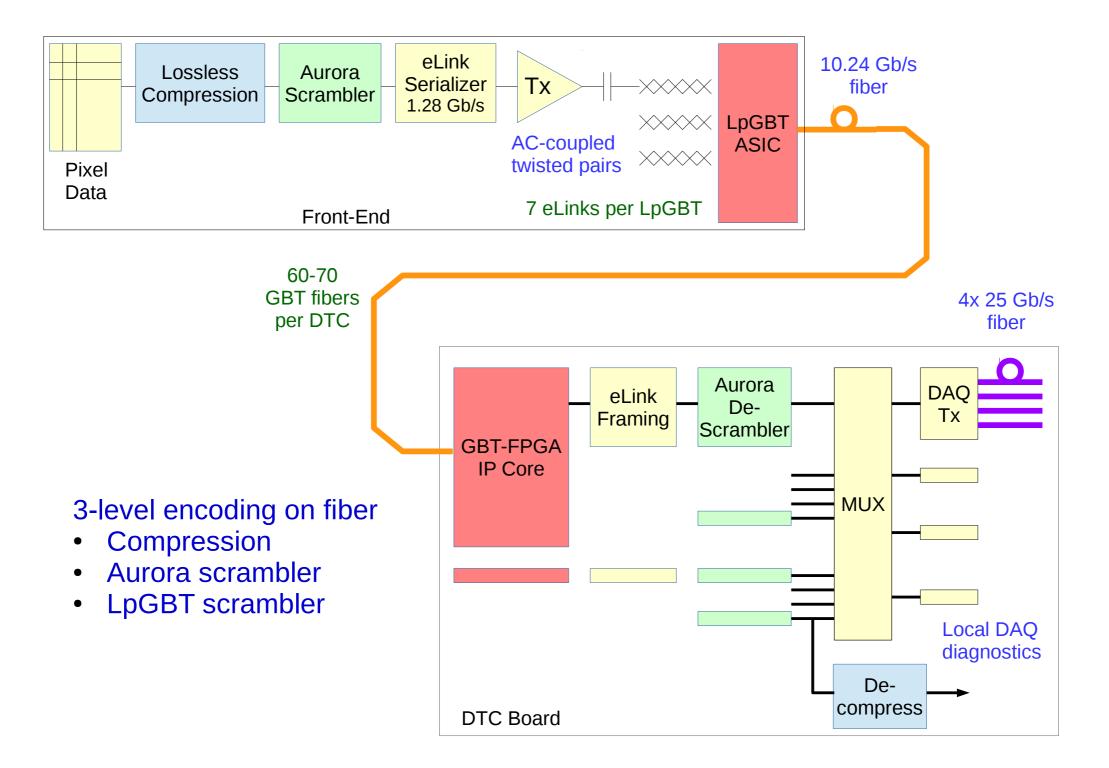

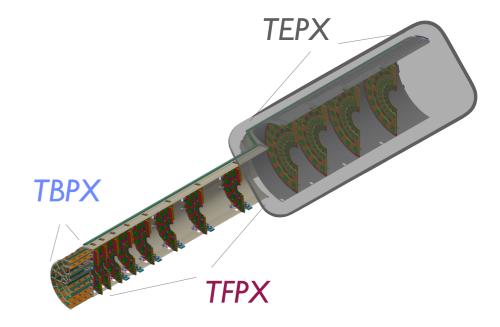

- Inner tracker off-detector electronics consists of DAQ interface modules and power supplies for the on-detector electronics

- DAQ interface: Data Trigger Control (DTC) board

- only data from Level-1 triggered events are transmitted to the back-end system

- communicates with on-detector electronics via low-power Gigabit Transceiver (LpGBT) optical links

- optical down-links at 2.5 Gb/s used for clock, trigger, commands, and configuration data to the pixel modules

- optical up-links at 10 Gb/s will carry readout data from L1 accept and monitoring info to the DAQ and control system

- Data accepted by L1 trigger are collected by the end of column of the pixel chip

- Pixel data array are compressed by lossless algorithm within the chip

- up to a factor of 2 compression can be achieved (in simulation) <u>Y. Cheng talk</u>

- Data are sent through differential electrical links (eLinks) at 1.28 Gb/s to LpGBT ASICs for optical transmission

- Each readout chip can transmit on 3 eLinks but actual number used depends on occupancy

#### ELinks readout counting for full Pixel detector

**TBPX** (108 mod L1x6 eLinks) + (252 mod L2x2 eLinks) + (504 mod L3/L4x1 eLinks) = 1656 eLinks

- **TFPX** (20 mod R1 x 3 eLinks) + (56 mod R2/R3 x 2 eLinks) + (32 mod R4 x 1 eLinks) = 204 eLinks / double-disk \* 16 double-disks = 3264 eLinks

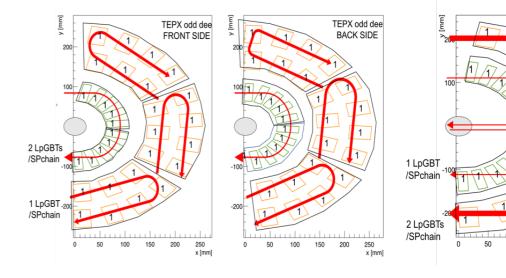

- **TEPX** 1760 mod x 1 eLinks = **1760** eLinks

- Constraints for combining eLinks into optical links:

- Each LpGBT has 7 eLink inputs

- All links from a module connects to the same LpGBT

- Modules can connect to same LpGBT only if they belong to the same power chain

#### Proposed mapping of eLinks into optical fibers from TDR

|                             | TBPX | TFPX    | TEPX | Total               |

|-----------------------------|------|---------|------|---------------------|

| E-links (readout)           | 1656 | 3 2 6 4 | 1760 | 6 6 8 0             |

| E-links (control)           | 864  | 1728    | 1760 | 4352                |

| Optical links (IpGBT links) | 332  | 640     | 288  | 1 260 <sup>10</sup> |

| Power chains                | 96   | 256     | 224  | 576                 |

| Front-end power [kW]        | 8    | 16      | 16   | 40                  |

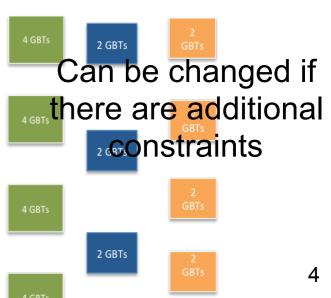

#### Currently some mapping have been proposed based on structure and service constraints:

#### From DAQ TDR:

- 1/4 pixel detector can be readout with 6 DTC (1 crate)

- assumed a DAQ bandwidth / DTC of ~360 Gbs

#### From IT Services document:

- requirement that TEPX services are completely separated

- ▶ requirement of mixing fibers from the TBPX and TFPX to reduces effect of DTC failures

| Slot # | <b>Board description</b>              | RX #                   |  |  |

|--------|---------------------------------------|------------------------|--|--|

| 8      | DTC (TEPX 4 half-disks)               | 72                     |  |  |

| 7      | DTC (half BPIX L1 + 1 TFPX half-disk) | 24 (30) + 20 = 44 (50) |  |  |

| 6      | DTC (half BPIX L2 + 1 TFPX half-disk) | 28 + 20 = <b>4</b> 8   |  |  |

| 5      | DTC (half BPIX L3 + 2 TFPX half-disk) | 12 + 40 = 52           |  |  |

| 4      | DTC (half BPIX L4 + 2 TFPX half-disk) | 16 + 40 = 56           |  |  |

| 3      | DTC (2 TFPX half-disk)                | 40                     |  |  |

| 2      | DTH 1                                 | -                      |  |  |

| 1      | DTH 2                                 | -                      |  |  |

- mapping proposal for the various subsystems in 1/4 of the Inner Tracker

- to readout 1/4 of Inner Tracker with 6 DTC, 72 fibers RX / DTC maximum are needed

- Proposal to increase the total number of TEPX DTC from 4 to 8

- DAQ interface for Inner Tracker: Data Trigger Control (DTC) board

- data from Level-1 triggered events are transmitted to the back-end system

- communicates with on-detector electronics via low-power Gigabit Transceiver (LpGBT) optical links

- Inner tracker layout and fiber counting

- fiber mapping designs need to consider limitation coming from power chain and services of the detector

- one of current proposal consists in 24 DTC boards to cover the entire Inner Tracker (based on 72 RO fibers / DTC)

- ▶ final number of RO fibers per DTC needs to be decided

- Proposal for lumi data processing (DTC requirements from Lumi in backup)

- have a separate lumi processor (perhaps a DTH board), to which the DTC would send the data over ~4x25Gb/s links

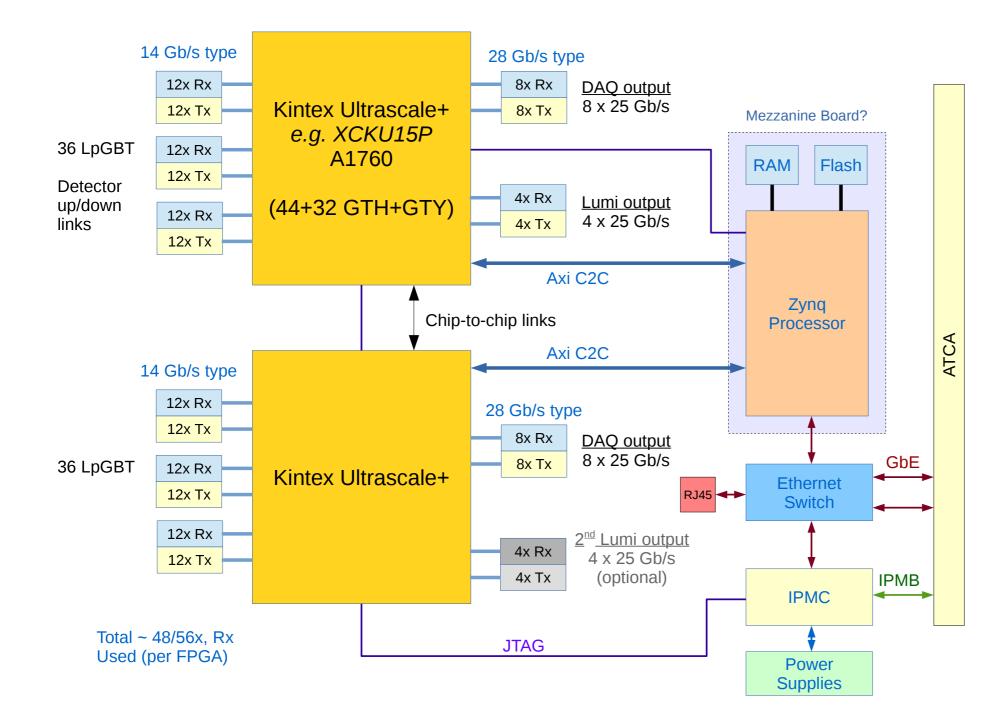

# **DTC: preliminary design**

and a set and a share

#### ▶ option with 25 Gb/s DAQ links

- Follow OT/CMS (not identical hardware)

- Xilinx Zynq CPU

- CERN standard IPMC

- Ethernet: Front panel and ATCA

- Design decisions:

- Unified blade or carrier/mezzanine?

- What FPGA/family?

#### ▶ **Proposed carrier block diagram:** option with 25 Gb/s DAQ links

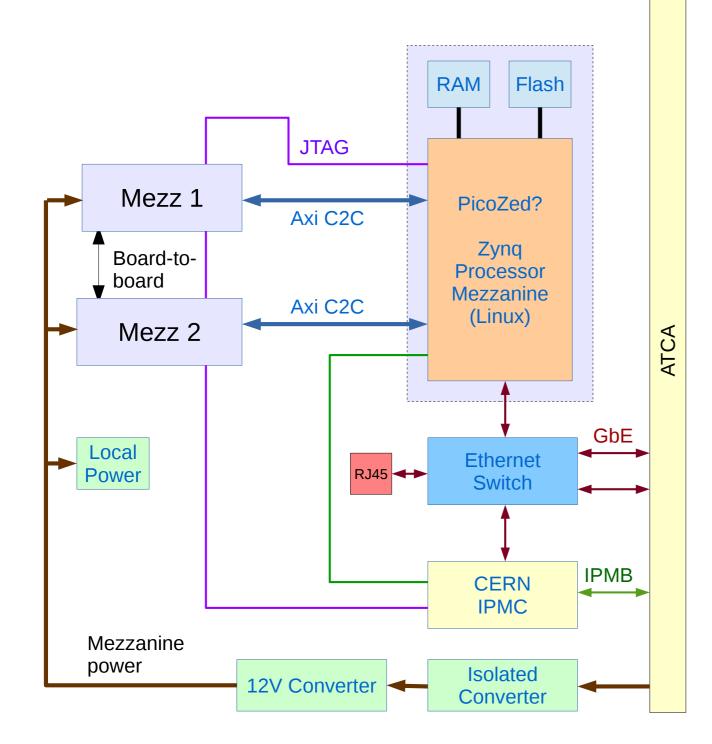

#### Preliminary plan:

simple/universal carrier blade design not tied to any particular FPGA/family

- Accommodates 2 smaller mezzanines or one large one

- Supplies JTAG, AXI chip-to-chip and 12V power

- Uses CERN IPMC, off-the-shelf Zynq board to save engineering

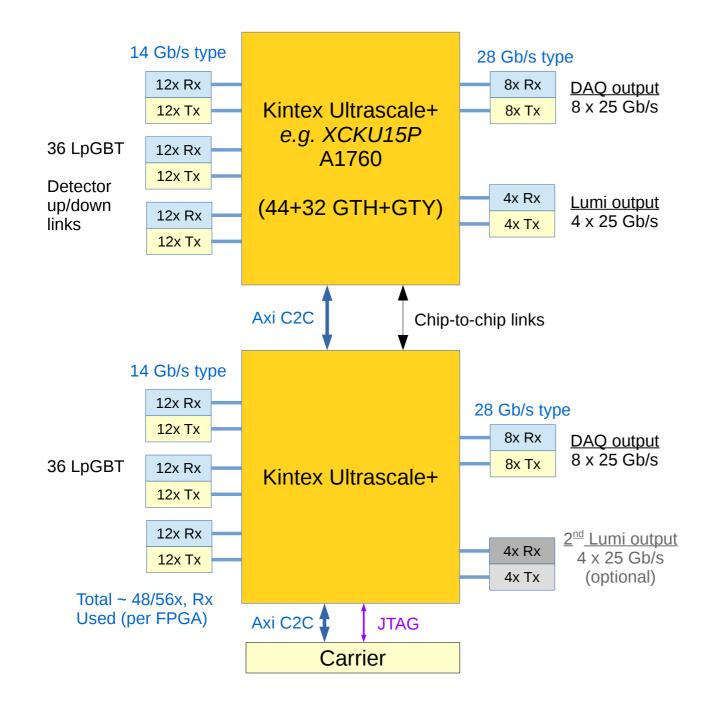

#### ▶ **Proposed mezzanine card:** option with 25 Gb/s DAQ links

#### Preliminary plan:

incorporate voltage regulators on mezzanine card allowing standalone tests

- FPGAs, Optics, Power on mezzanine

- Test connectors for operation sans blade

- Proposed mezzanine card: option with 25 Gb/s DAQ links

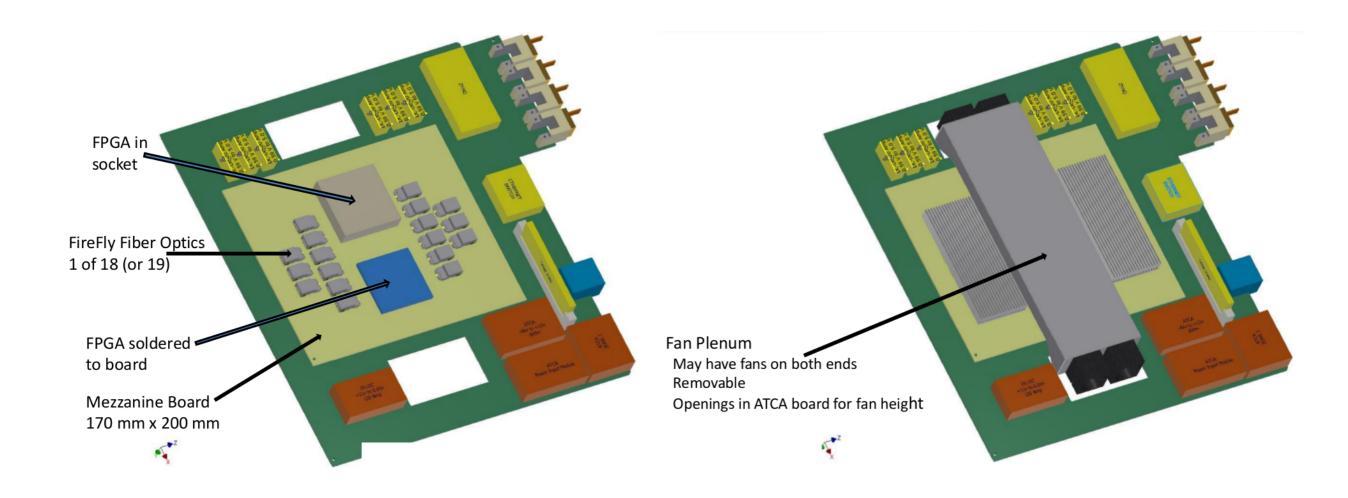

- ▶ foreseen cooling scheme for FPGA and fiber optics

- Preliminary eLinks and IpGBT links calculation for DTC counting

- constraints from power chain and services in connecting modules to DTC for RO

- assumed a data compression up to a factor of 2

- DTC considerations from Lumi

- maintain close contacts with Lumi group to understand better the DTC needs for lumi measurements

- DTC could send data to lumi processor over 4x25 Gb/s (or 10x10Gb/s) links

#### Next steps

- define DTC specifications in the next months (collaboration with Cornell)

- ▶ prototype to be manufactured early 2019

- discussions ongoing with DAQ, FE groups to take into account all needs for board design

many a user or own spens

gul a set entered digen for me

signe a my at exercise of proved

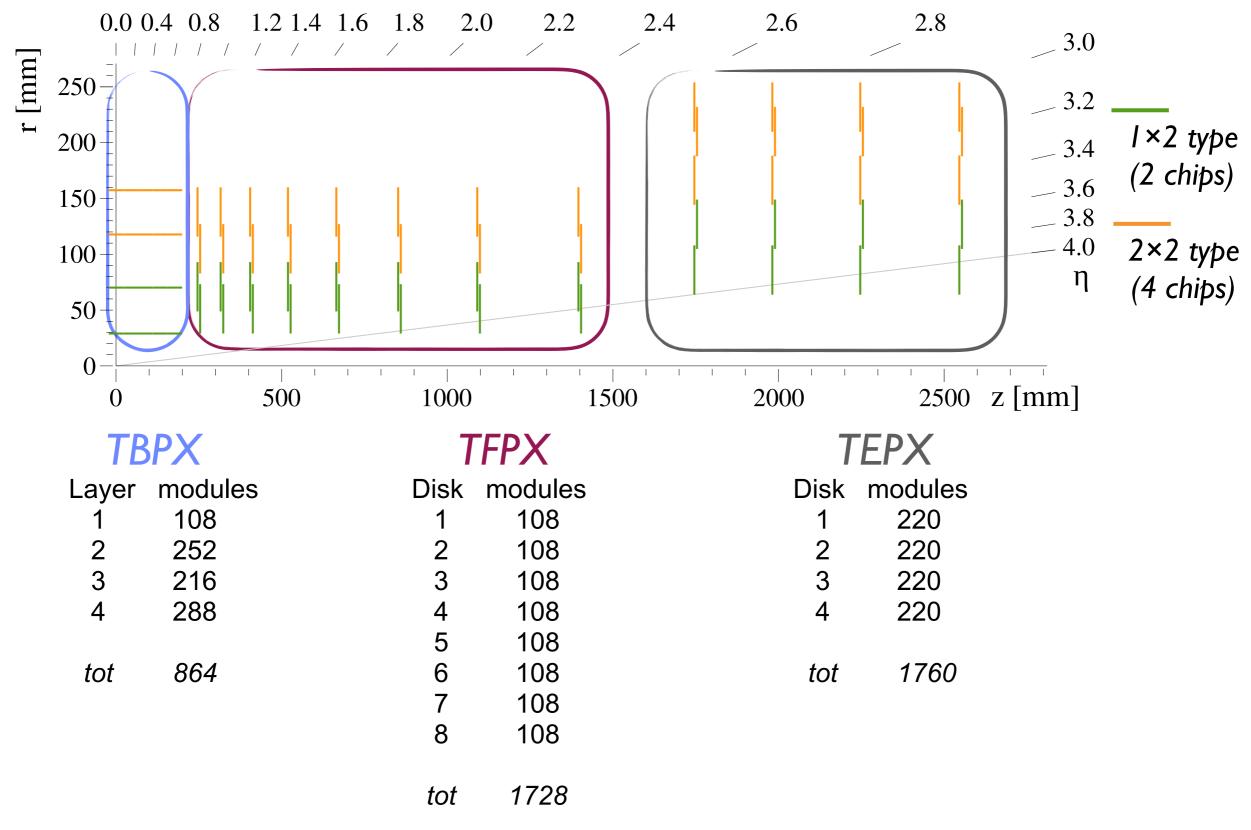

### Pixel layout from TDR

| TBPX                           |        |             |             |             |                   |            |        |        |                   |

|--------------------------------|--------|-------------|-------------|-------------|-------------------|------------|--------|--------|-------------------|

| Layer                          | 1      | 2           | 3           | 4           |                   |            |        |        |                   |

| Average radius [mm]            | 29.0   | 70.1        | 117.8       | 157.4       |                   |            |        |        |                   |

| z coverage [mm]                | ±199.7 | $\pm 199.7$ | $\pm 199.7$ | $\pm 199.7$ |                   |            |        |        |                   |

| $N_{ m ladders}$               | 12     | 28          | 24          | 32          | Total: 96         |            |        |        |                   |

| $N_{ m modules}$               | 108    | 252         | 216         | 288         | <b>Total: 864</b> |            |        |        |                   |

| <b>TFPX</b> (one side)         |        |             |             |             |                   |            |        |        |                   |

| Double-disc                    | 1      | 2           | 3           | 4           | 5                 | 6          | 7      | 8      |                   |

| Average <i>z</i> position [mm] | 250.0  | 319.8       | 409.0       | 523.1       | 669.1             | 855.8      | 1094.6 | 1400.0 |                   |

| N <sub>rings</sub>             | 4      | 4           | 4           | 4           | 4                 | 4          | 4      | 4      |                   |

| $N_{ m modules}$               | 108    | 108         | 108         | 108         | 108               | 108        | 108    | 108    | <b>Total: 864</b> |

| Per TFPX double-disc           |        |             |             |             |                   |            |        |        |                   |

| Ring                           | 1      | 2           | 3           | 4           |                   |            |        |        |                   |

| Inner radius [mm]              | 30.1   | 49.5        | 84.4        | 117.0       |                   |            |        |        |                   |

| Outer radius [mm]              | 73.2   | 93.0        | 127.0       | 160.0       |                   |            |        |        |                   |

| $N_{ m modules}$               | 20     | 32          | 24          | 32          | Total: 108        |            |        |        |                   |

| TEPX (one side)                |        |             |             |             |                   |            |        |        |                   |

| Double-disc                    | 1      | 2           | 3           | 4           |                   |            |        |        |                   |

| Average <i>z</i> position      | 1750.0 | 1985.4      | 2250.8      | 2550.0      |                   |            |        |        |                   |

| N <sub>rings</sub>             | 5      | 5           | 5           | 5           |                   |            |        |        |                   |

| $N_{\rm modules}$              | 220    | 220         | 220         | 220         | Total: 880        |            |        |        |                   |

| Per TEPX double-disc           |        |             |             |             |                   |            |        |        |                   |

| Ring                           | 1      | 2           | 3           | 4           | 5                 |            |        |        |                   |

| Inner radius [mm]              | 64.3   | 105.1       | 145.2       | 188.5       | 210.4             |            |        |        |                   |

| Outer radius [mm]              | 108.0  | 149.0       | 188.5       | 232.0       | 254.0             |            |        |        |                   |

| $N_{ m modules}$               | 40     | 56          | 36          | 40          | 48                | Total: 220 |        |        |                   |

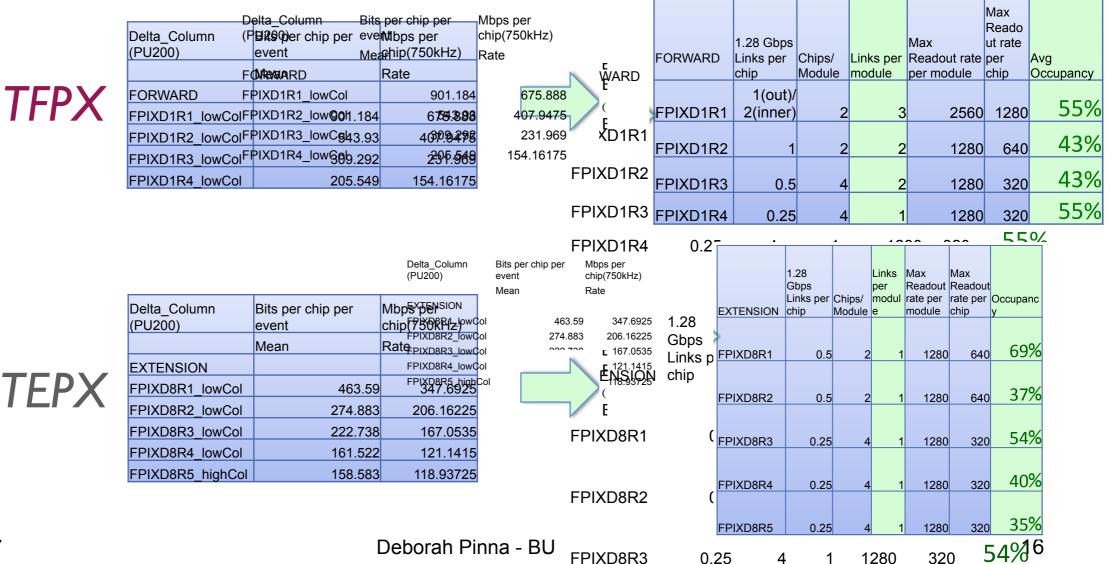

### Pixel rates after compression and eLinks

#### From S. Orfanelli based on rates from Y. Cheng

|       | Delta_Column  | Bits per chipeberColur         |                | ip per Mbps per chip             |

|-------|---------------|--------------------------------|----------------|----------------------------------|

|       | (PU200)       | event <sup>(PÚ200)</sup>       | (750kHᢓyent    | (750kHz)                         |

| Cheng |               | Mean                           | Rate Mean      | Rate                             |

|       | BARREL        | BARREL<br>BPIXL1 (PR2          | 2x2            | 3173.6 2380.2                    |

| TBPX  | BPIXL1(PR2x2) | вріха 17, <b>3</b> нб          | · ·            |                                  |

| ΙΟΓΛ  | BPIXL1(PR1x4) | BP <b>2/9</b> _11Q.1 <b>85</b> | 4x1) 2183.1375 | 3529.3 <mark>9 2647.04</mark> 25 |

|       | BPIXL1(PR4x1) | BP3529.39                      | 2647.0425      | 695.036 521.277                  |

|       | BPIXL2        | BPIXL3<br>695.036              | 521.277        |                                  |

|       | BPIXL3        | BPIXL4<br>308.774              | 231.5805       | 202.568 151.926                  |

|       | BPIXL4        | 202.568                        | 151.926        |                                  |

|       |               |                                |                |                                  |

|   | BARREL            | 1.28<br>Gbps<br>Links<br>per chip | Chips/<br>Module | Links<br>per<br>module | Max<br>Readou<br>t rate<br>per<br>module | Max<br>Reado<br>ut rate<br>per<br>chip | Occupan<br>cy |

|---|-------------------|-----------------------------------|------------------|------------------------|------------------------------------------|----------------------------------------|---------------|

|   | (PR2x2)           | 3                                 | 2                | 6                      | 7680                                     | 3840                                   | 62%           |

|   | BPIXL1<br>(PR1x4) | 3                                 | 2                | 6                      | 7680                                     | 3840                                   | 57%           |

| ł | BPIXL1<br>(PR4x1) | 3                                 | 2                |                        |                                          |                                        | C00/          |

|   | BPIXL2            | 1                                 | 2                |                        |                                          |                                        | 410/          |

|   | BPIXL3            | 1                                 | 4                | 1                      | 1280                                     | 320                                    | 72%           |

|   | BPIXL4            | 1                                 | 4                | . 1                    | 1280                                     | 320                                    | 47%           |

Deborah Pinna - BU FPIXD8R3

0.25 Δ 320

1280

1

Pixel Readout: Logic chain showing encoding

## The DTC understanding of Lumi

and a set and and a starten

Phase II: 3 luminosity measurement systems considered

- Calorimetric-type

- Minimum Ionizing Particle counting

- Low occupancy pixel based measurement using the data collected from TEPX

#### General plan

- Have a separate lumi processor board, to which the DTC would send the data over ~4x 25Gb/s links

- ▶ eg. lumi board could be a mezzanine card or a board on DTH

- Lumi measurement

- lumi measurements consists in *counting number of hits per unit of time* and fill in an histogram with this information / BX / geometric region

- must run whenever there is beam in the machine, independent of state of global DAQ (TCDS must be running as lumi-nibble counter updates are sent)

- data loss due to e.g. slow control intervention should be known by back-end board and passed on to lumi (orbit by orbit, pref.)

- might need info of previous and later BXs

- may want disk-to-disk coincidences where there is overlap

- coincidence could be done among front and back half disks

- back-pressure from DAQ should not affect lumi board

#### Lumi trigger

- process events marked with ~75kHz lumi triggers separately from main DAQ stream and pass to lumi DAQ. Bandwidth would be ~10% of 360Gb/s or 36Gb/s

- during "unstable beams" no L1 triggers only lumi triggers

- lumi trigger rate may be >> 75kHz but bandwidth similar to beam operation

- bandwidth similar to beam operation employing only outer TEPX disks

- Compression

- compression performed on pixel chip using arbitrary regions that are not mapped to real clusters

- data must be de-compressed and re-clustered for luminosity measurements

- ▶ the DTCs will send the compressed data to the lumi board (to limit bandwidth)

- decompression will still be performed on the DTC (maybe only on a subset of events) for monitoring reasons