# LLRF Controller for High Current Cyclotron Based BNCT System

X.L. Fu<sup>1,2</sup>, Z.G. Yin<sup>1</sup>, K. Fong<sup>2</sup>, T.J Zhang<sup>1</sup>, J.Y Wei<sup>1</sup>, B. Ji<sup>1</sup>, F.P. Guan<sup>1</sup>, X.T. Lu<sup>1</sup>, Y. Wang<sup>1</sup>

1. China Institute of Atomic Energy, P.O.BOX275-3, Beijing 102413, China

2. TIRUMF, VANCOUVER V6T 2A3, Canada

## Abstract

CIAE is building a high current cyclotron based BNCT system. The designed beam loading of this cyclotron is 1 mA. The RF system of the cyclotron consists of two separate cavities, two 20 kW amplifiers, a 300 W amplifier for the buncher, and a LLRF system. A digital LLRF system was developed for the BNCT LLRF system. In which, the amplitude and phase of the two separate Dees as well as the buncher for beam injection will be regulated by a single FPGA. The design shows a promising future, both from real-time response and flexibility point of view. The design ideas, technique feature, system structure, hardware and software development, and the desktop test will be presented.

#### Introductions

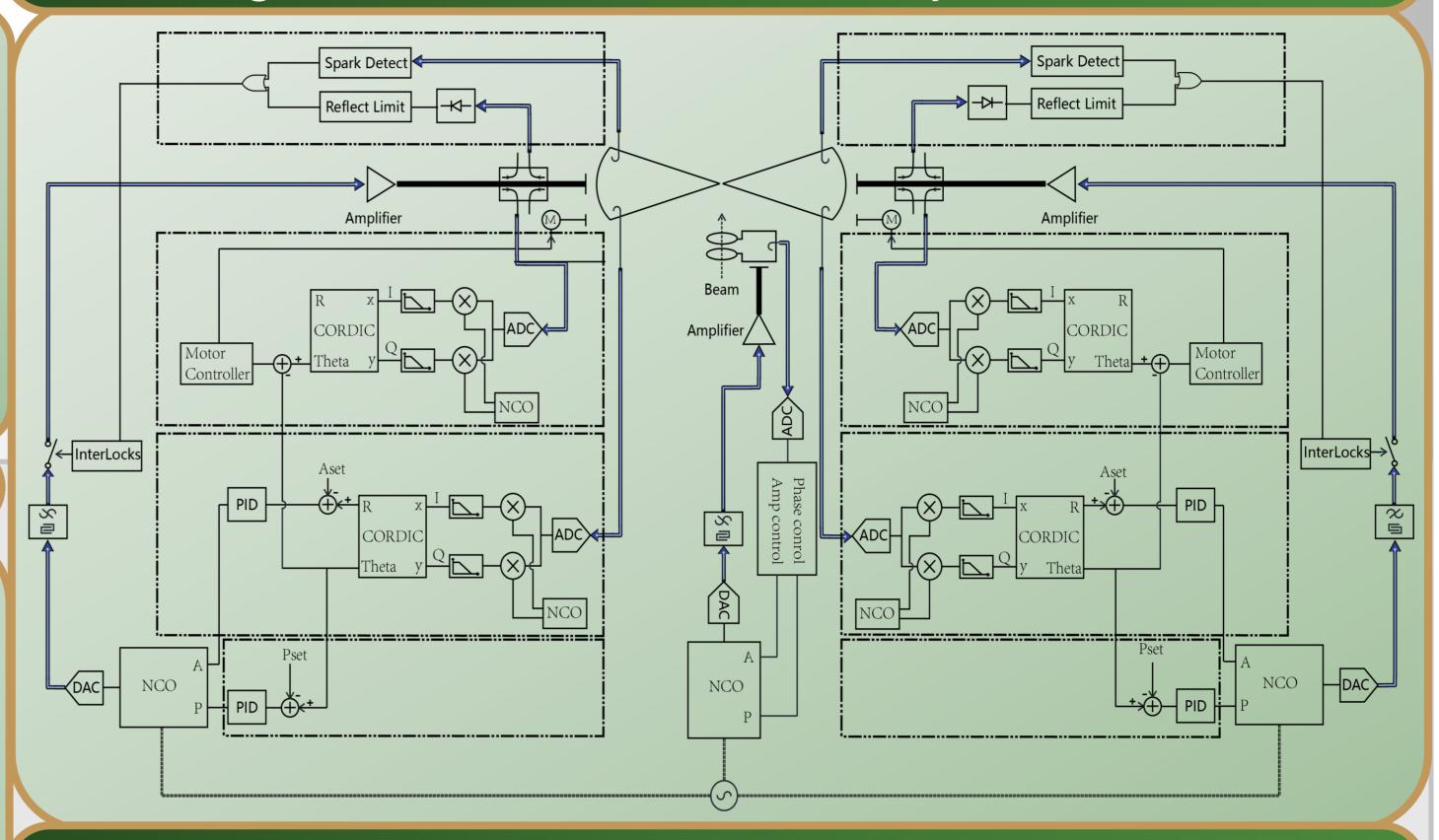

A digital LLRF system from TRIUMF is extended and utilized for the BNCT LLRF system. The RF system of the BNCT cyclotron consist of two independent cavities, two amplifiers and a digital LLRF system. The single FPGA board controls the amplitude and phase of the three channels of RF signals, the tuning of the two cavities, the spark detection, the reverse power detection, and the auto-start procedure.

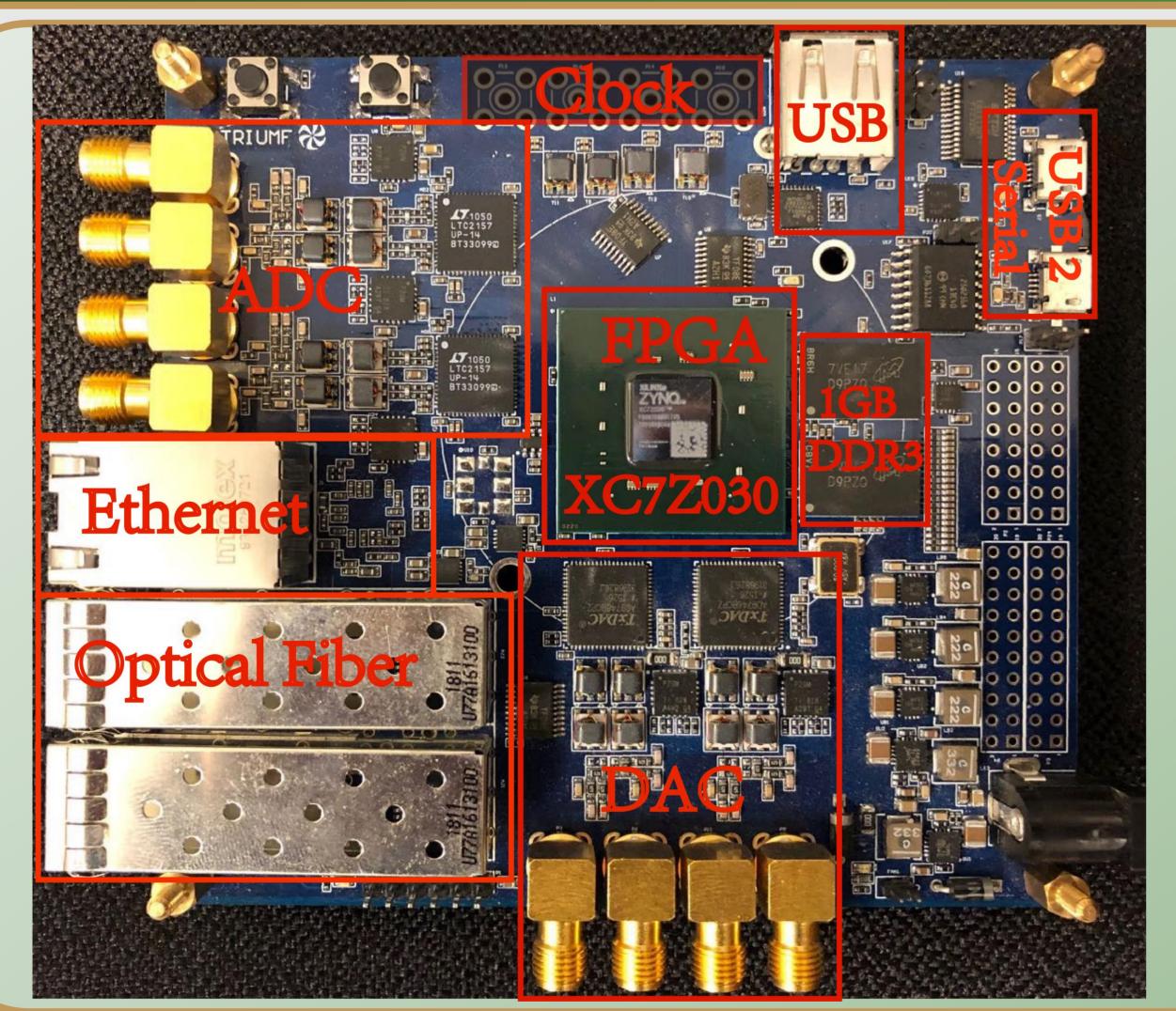

## Design of the hardware

- Four channels of ADC, 250 MSPS

- > Four channels of DAC, 250 MSPS

- Four digital clock I/Os, Single end/Differencial

- > ZYNQ FPGA, dual core ARM Cortex-A9, 800 MHz

- > 1GB DDR3, 32MB QSPI FLASH, 2Mb SPI FLASH

- > USB 2.0

- > Two channels of USB to serial port

- > 1000 Mbps Ethernet

- > Two channels of 6.5 Gbps Optical Fiber interface

- > 52 User GPIOs

- > 11cm\*11cm

- > 14 layers PCB

- > 12 V DC Single Power Supply

#### PCB Board

## The diagram of the LLRF control system

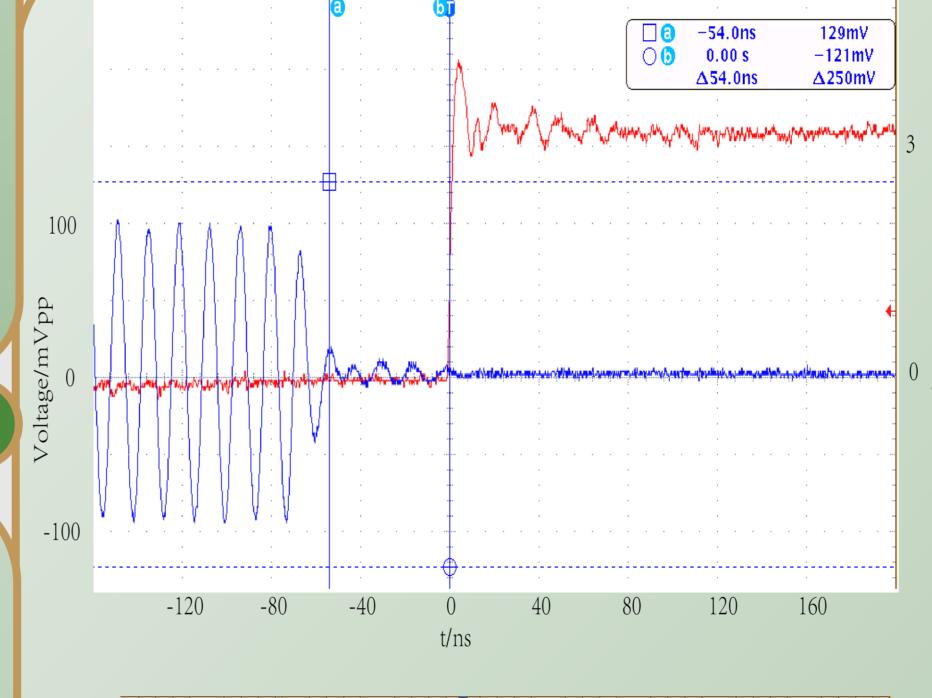

#### Desktop Test of the Real Time Protection

The spark detection is tested with 73 MHz signal. The latency of the circuit is less than 60 ns. With a higher frequency, the latency would be smaller.

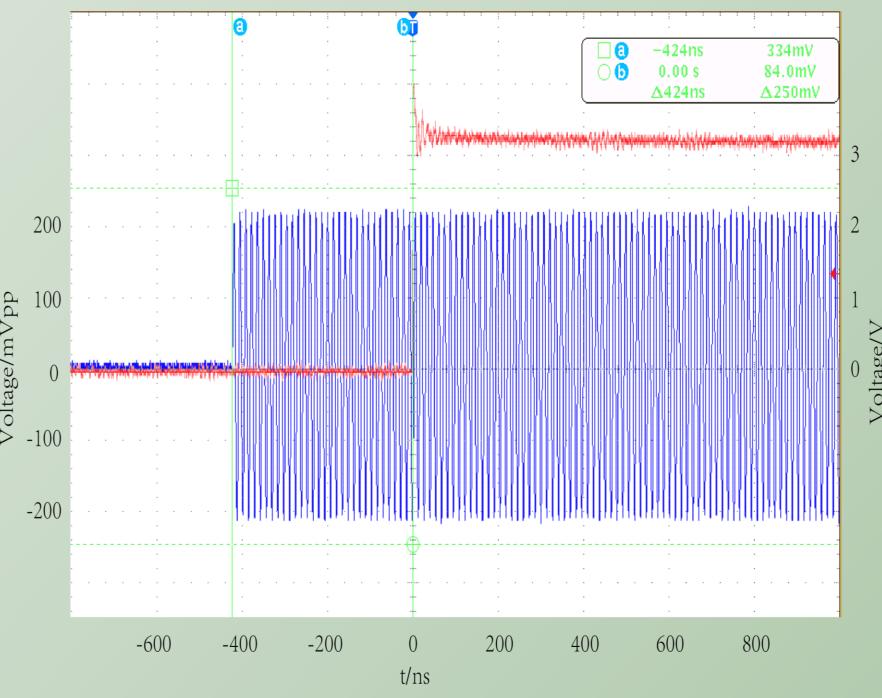

The reverse power detection is tested with step signal. The circuit work at 250 MHz frequency. The latency of the circuit irrelevant to the frequency of the signal.

# Summary

A digital LLRF hardware and firmware is designed for CYCIAE-14B. The LLRF system controls the amplitude and phase and the tuning of the two cavities, the amplitude and phase of the buncher system and implements the spark detection and reverse power detection. The desktop test indicates that the system meets the design requirements. In particular, the real time protection is tested, and the results show that the spark detection can be done in 60 ns and the reverse power detection can be done in 500 ns.