# Activities of WIB/FELIX Readout for ProtoDUNE-SP @ BNL

H.Chen, K.Chen, J.Fried, D.Gastler, S.Gao, J.Hugon, <u>J.Zhang</u>

July 4, 2018

6/12/2018

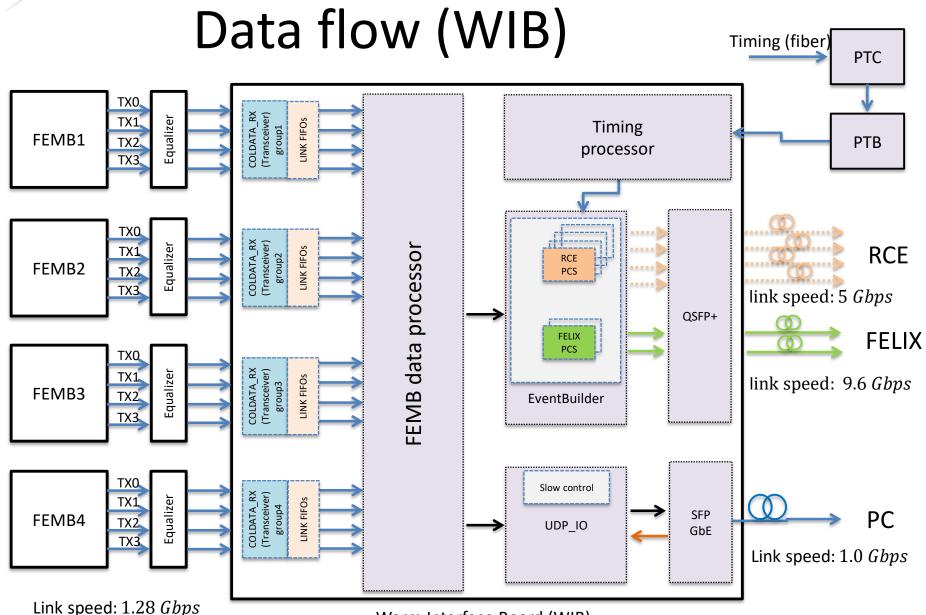

Warm Interface Board (WIB)

J. Zhang - 21st IEEE RT

#### BU firmware 18030101

- Zeros in cold data blocks (corrupted data) we have observed at one link when taking real data (FEMB data).

- Haven't seen this issue when taking fake data.

- One link is less stable than the other when using fdaq to take data.

- Sometimes, it stops sending data to FELIX

- Local diagnostic UDP port is not able to collect FEMB data continuously.

- The output data has crc error.

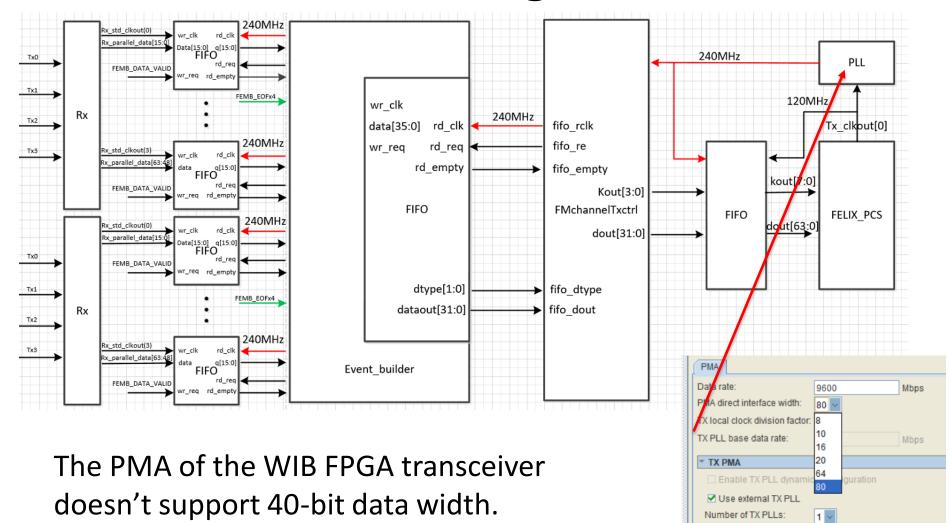

#### WIB firmware modification

- Revision based on BU firmware

- Counter mode is functioning well.

- Zeros in cold data blocks are also observed at one link when taking FEMB data.

- Revision based on BNL firmware

- Have Integrated FELIX stuff into it.

Main TX PLL logical index: 0

TX PLL 0

#### Block diagram

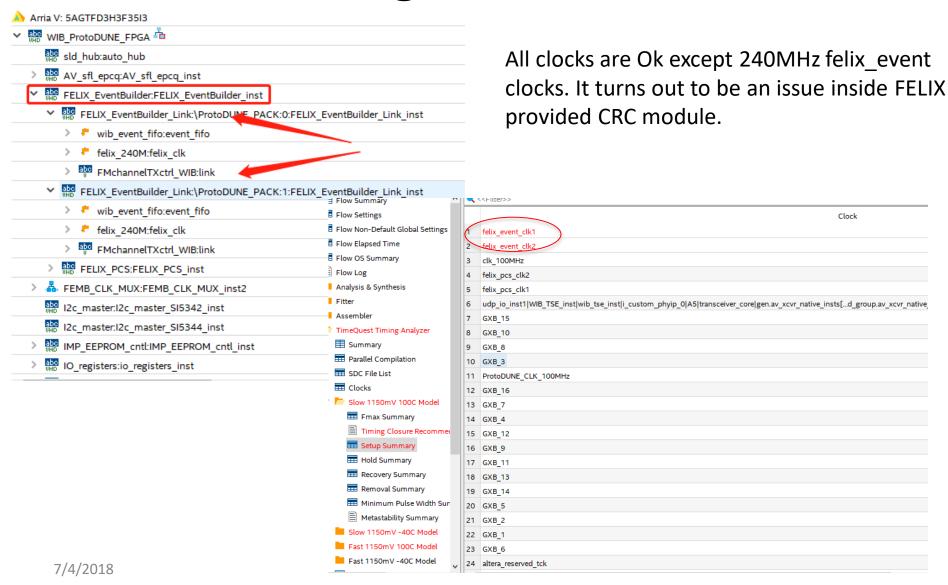

#### Timing constraints

#### FELIX CRC module

#### FELIX provided CRC module

```

rising_Edge(Clk) then

if Reset = '1' then

for k In 0 to Nbits loop

if(k = 0) then

Reg := (InDirectInitVal); --(CRC_Width-1 downto 0)&dinP(k))xor ('0'&Poly);

Reg := (Reg(CRC_Width-2 downto 0)&din(Nbits - k))xor (Poly);

Reg := Reg(CRC_Width-2 downto 0)&din(Nbits - k);

end if:

end loop;

else

Reg := InDirectInitVal;

end if:

else

for k In 1 to Nbits loop

if Reg(CRC_Width-1) = '1' then

Reg := (Reg(CRC_Width-2 downto 0)&din(Nbits - k))xor (Poly);

Reg := Reg(CRC_Width-2 downto 0)&din(Nbits - k);

end if;

end loop:

Reg := Reg;

```

Not a good idea to write HDL code like this although no timing issues found in Xilinx FPGA. It will cause a large delay in data path due to the large combinational logic.

https://its.cern.ch/jira/browse/FLXUSERS-173

Replacing it with a pipelined crc module generated online, no timing issues reported.

http://outputlogic.com/?page id=

321

```

felix_event_clk1

felix event clk2

Timing closed

clk 100MHz

felix pcs clk2

felix pcs clk1

udp_io_inst1|WIB_TSE_inst|wib_tse_inst|i_custom_phyip_0|A5|transceiver_core|gen.av_xcvr_native_insts[...d_group.a

ProtoDUNE CLK 100MHz

GXB 1

10 GXB 12

11 GXB_7

12 GXB_13

13 GXB 16

14 GXB 3

15 GXB 14

16 GXB 8

17 GXB_10

18 GXB 4

19 GXB 15

20 GXB 5

21 GXB 11

22 GXB 9

23 GXB 6

```

### Debugging

A bug found and fixed.

```

when S_START_Of_FRAME =>

<= '0':

PKT_LATCH_i

<= '0'

<= '0'

FRAME_ERROR_i

CHKSUM_ERROR_i

HEADER ERROR i

FEMB_DATA_VALID

<= '0'; --bug here.

UDP_DATA_VALID

if((DATA_VALID = '1') and ( WORD_CNT <= (Frame_size-1))) then

WORD_CNT

<= WORD_CNT + 1;

UDP_DATA_VALID

<= '0':

if(WORD_CNT /= 0) then

CHECKSUM_i <= CHECKSUM_i + DATA_IN;

end if:

case WORD_CNT IS

when 0 =>

FEMB_DATA_VALID <= '1':

CHECKSUM_IN <= DATA_IN;

when 1 =>

FEMB_DATA_VALID <= '1'; --added here 0621

TIME_STAMP_IN <= DATA_IN;

when 2 =>

FEMB_DATA_VALID <= '1'; --added here

ADC_ERROR_IN <= DATA_IN;

when 3 =>

FEMB_DATA_VALID <= '1'; --added here

RESERVED_IN

<= DATA_IN;

FEMB_DATA_VALID <= '1'; --added here

HEADER_IN <= DATA_IN;

if(UDP_DISABLE_S = '0') then

UDP_DATA_VALID <= '1';</pre>

end if:

if(RESERVED_IN(0) = '0') then

UDP_DATA_I

<= x"FACE";

else

```

## Debugging

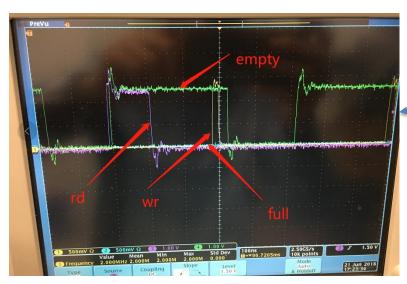

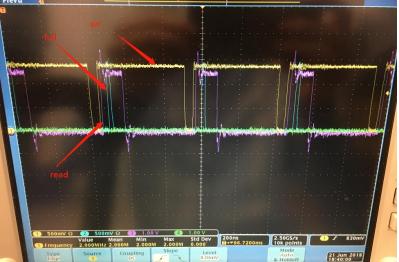

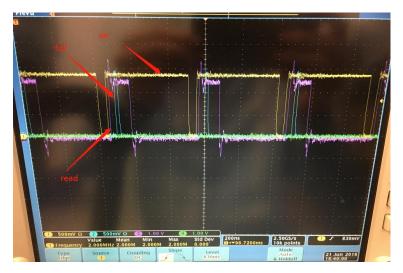

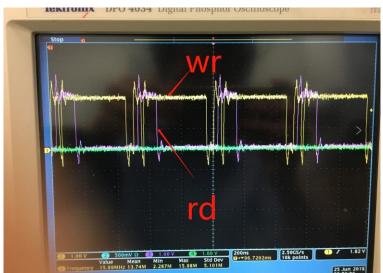

Now the fifo write enable signal becomes normal and we get the ADC data, but the full signal should not appear since read process is more faster than write process.

#### A bug found and fixed

The channel write 29 word into the fifo, but the eventbuilder only read out 28 words. The fifo will full sooner or later.

### Debugging

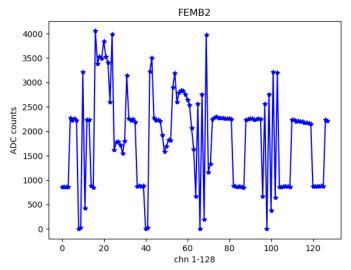

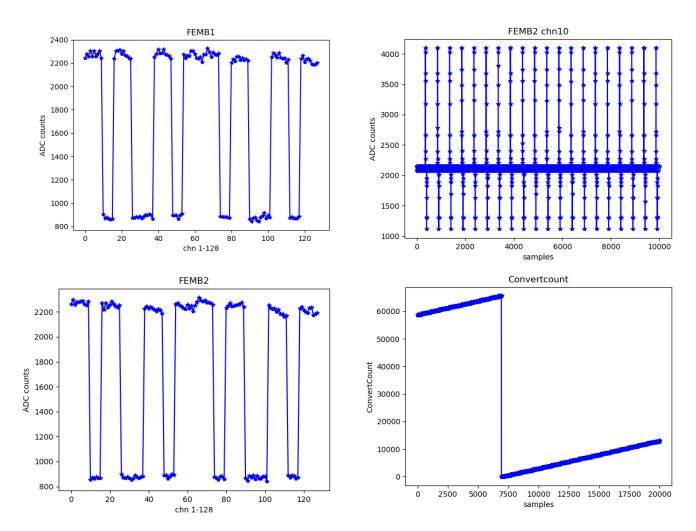

We met this issue before in BU firmware. Data are not aligned. It turns out to be the configuration issue.

A bug found and fixed. New python scripts developed for configuration. After configuring all 4 FEMBs, a fifo clear operation should be done. Such that, data from all channels are aligned.

#### Results

All plots are OK

#### Progress & Next steps

- Both 2 links are continuously taking good FEMB data without CRC error.

- The WIB is freely running for a week, the links are stable and data are good. We are setting up an automatic stability test for the WIB firmware.

- The local diagnostic udp port is working independently with real DAQ. It is able to collect data chip by chip at the same time.

- New python scripts developed for this firmware will be integrated into WIB-FELIX python framework (local diagnostic + FELIX).

- Planning to integrate the timing system into the firmware.