# Design of matrix 1 for RD50-ENGRUN1 - Analog sampling

O. Alonso, S. Moreno, N. Franch, J. Canals, V. Moro and A. Diéguez

SIC, Electronics and Biomedical Eng. Department, University of Barcelona, Spain

oalonso@el.ub.edu

| pads    | IO pads                                                                                                              | IO pads                                                                     | IO pads                                                         | IO pads                                                       |                                                         |         | pads    |

|---------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|---------|---------|

| OI      | Matrix 1 with an analog timing circuit to sample 3-5 points of the sensor rising time and extrapolate t <sub>0</sub> | Matrix 2 with a time-to- ligital converter ircuit to sample the sensor time | Matrix 3<br>with super-fast<br>pixel, ideally<br>within 1-2 BXs | Matrix 4 imaging matrix with different sensor cross- sections | Matrix 5 Type A                                         |         | d OI    |

| Test 1  |                                                                                                                      |                                                                             |                                                                 |                                                               | (reticle-<br>boundary<br>readout,<br>pre-<br>stitching) | IO pads | Test 4  |

| IO pads |                                                                                                                      |                                                                             |                                                                 |                                                               |                                                         |         | IO pads |

| Test 2  |                                                                                                                      |                                                                             |                                                                 |                                                               | Matrix 5 Type B                                         |         | Test 5  |

| IO pads |                                                                                                                      |                                                                             |                                                                 |                                                               | (reticle-<br>boundary<br>readout,                       | IO pads | IO pads |

| Test 3  | IO pads                                                                                                              | IO pads                                                                     | IO pads                                                         | IO pads                                                       | pre-<br>stitching)                                      |         | Test 6  |

| Test structure 1 | Simple CMOS capacitors to study oxide thickness          |

|------------------|----------------------------------------------------------|

| Test structure 2 | 10 x 10 matrix of very small pixels with passive readout |

| Test structure 3 | 10 x 10 matrix of very small pixels with 3T-like readout |

| Test structure 4 | Small matrix of pixels for TCT, e-TCT and TPA-TCT        |

|                  | measurements                                             |

| Test structure 5 | Single pixels for sensor capacitance measurements        |

|                  |                                                          |

#### **CERN/RD50** collaboration:

International project to develop radiation hard semiconductor devices for very high luminosity colliders

#### **Target of this submission:**

- Improve the timing resolution of HV-CMOS sensors with different solutions implemented at the readout circuit level

- Study new sensor cross-sections

- Study pre-stitching options (increase the device area beyond the reticle size limitation)

#### **Technology**:

- 150 nm HV-CMOS from LFoundry

#### **Design effort:**

- IFAE (R. Casanova)

- Uni. Barcelona (O. Alonso)

- Uni. Liverpool (S. Powell, E. Vilella and C. Zhang)

- FBK (N. Massari and M. Perenzoni)

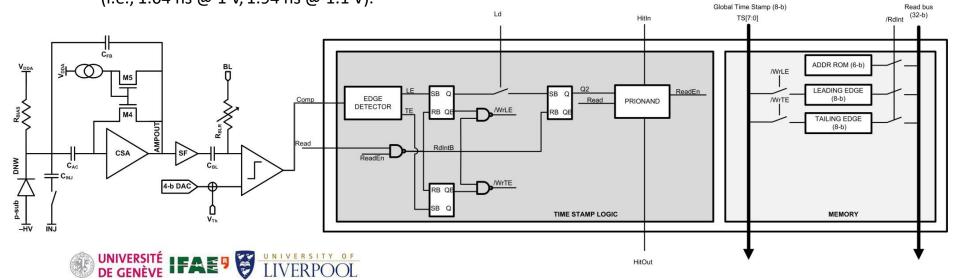

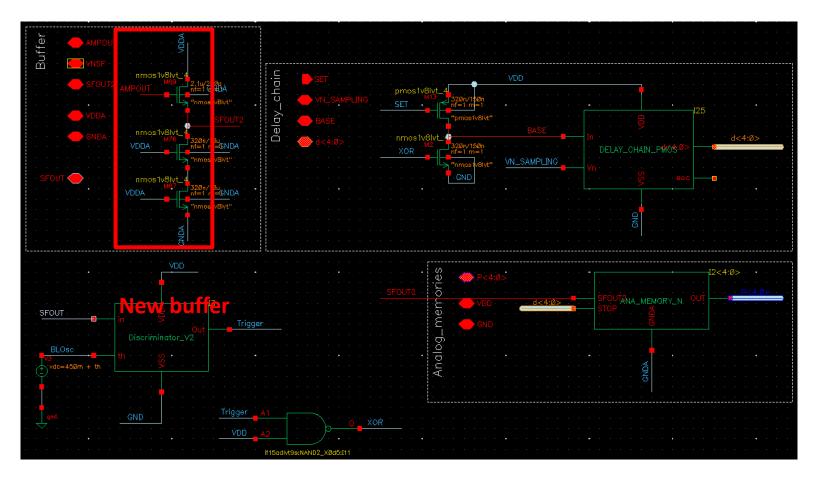

#### The pixel in Matrix 1 includes:

- Sensor  $\rightarrow$  50 µm x 50 µm (~200 fF parasitic capacitance)

- Analog readout electronics → CSA, shaper, filter and comparator.

- <u>Digital readout electronics</u> → Electronics that sense the leading edge of the comparator and store the corresponding time-stamp in an 8-bit memory. The electronics also store the pixel address in another 8-bit memory (this info is not needed for the analysis presented in these slides).

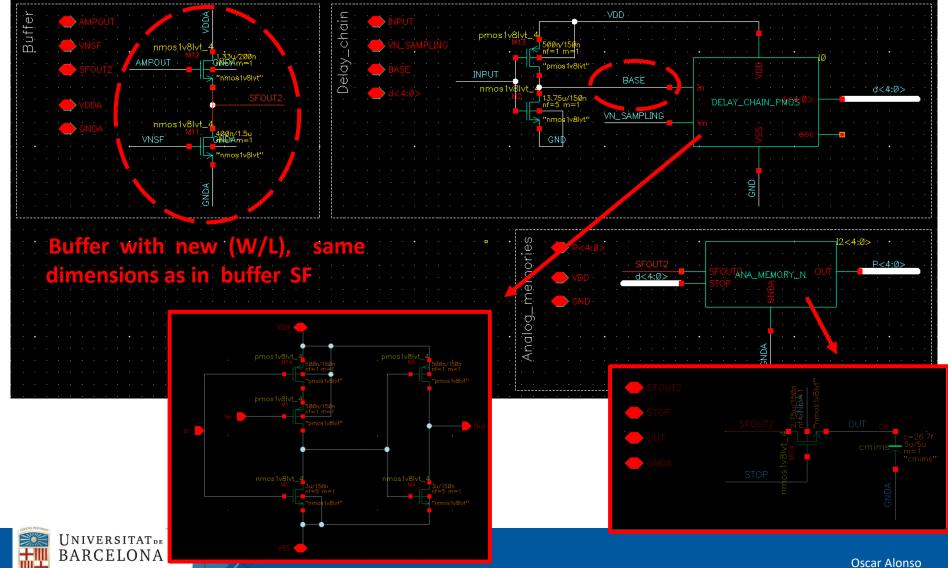

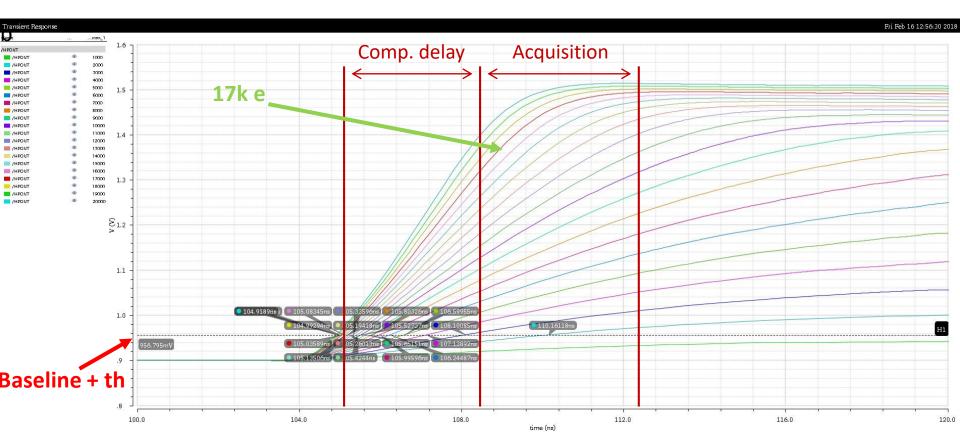

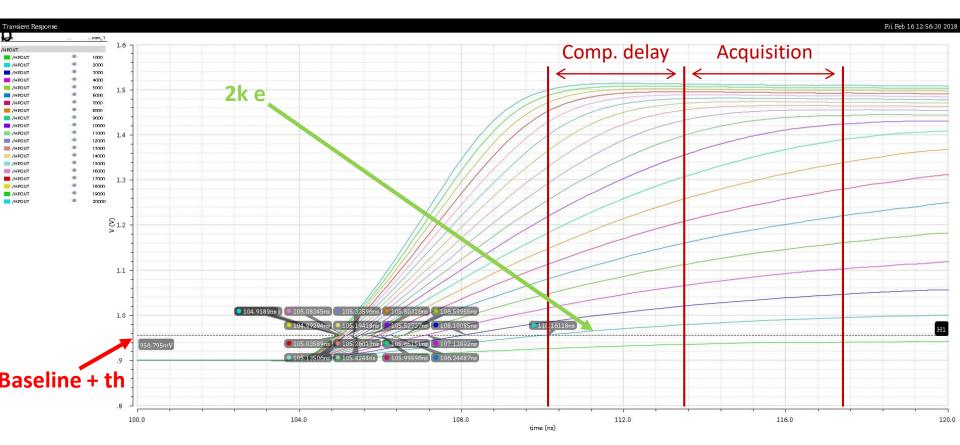

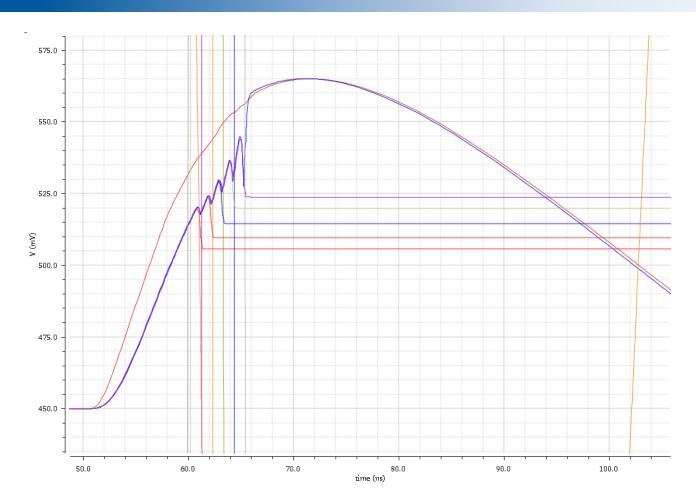

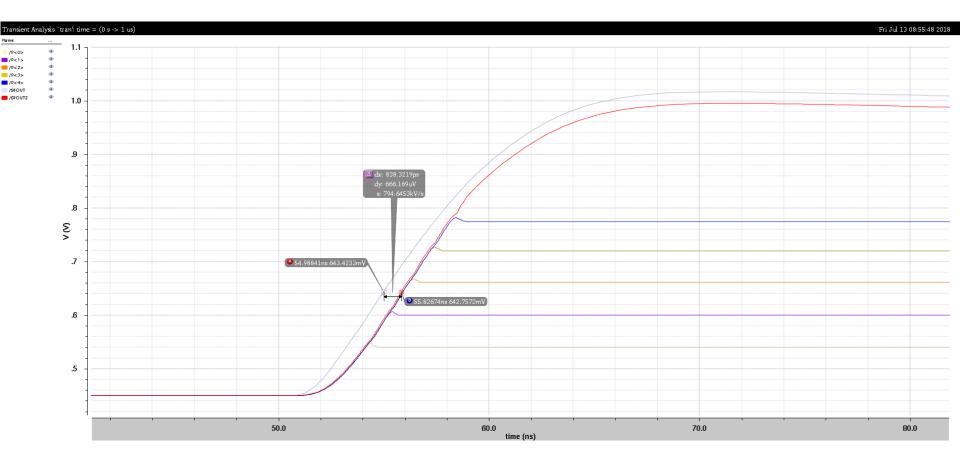

- Sampling electronics → Chain of delay elements and sample & holds to store 5 analog voltages. The sample & holds sample the output voltage of the shaper. The delay elements put the sample & hold in hold mode when there is an event in the pixel. We can tune the delay with an external voltage (i.e., 1.04 ns @ 1 V, 1.94 ns @ 1.1 V).

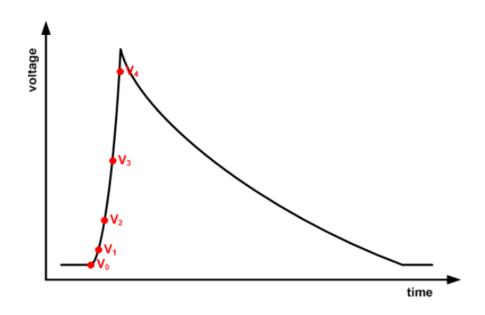

voltage Simplified schematic and functionality WR, time The main idea is to store up to 5 analog voltages.

Input charge 2k - Power consumption =  $25.72 \mu W$

# Input charge 9k - Power consumption $\sim 28 \,\mu W$

#### Conclusion

- The quality of the method depends on:

- Value of VN → How do we choose the appropriate value of VN?

- Comparator time response

- It also depends on the amount of input electrons

- Better time resolution at larger amounts of input electrons

- It also depends on the proximity of the real event time to the Cadence/chip time-stamp

- An event happening at 1.022  $\mu$ s gives a better time resolution than an event happening at 2.385  $\mu$ s, as 1.022  $\mu$ s is closer to the timestamp (1  $\mu$ s = 20 \* 50 ns) than 2.385  $\mu$ s (2.35  $\mu$ s = 47 \* 50 ns).

- Time-stamp period

- Power consumption of 28 uW per pixel with the possibility to reduce it to 22 uW

- Other solutions under study

#### **Conclusion**

Instead of defining time axis we define the voltage axis=> We are designing a TDC