#### Overview

# Bunch-by-Bunch position measurement for the CERN-PS: coping with RF-gymnastics

Jeroen Belleman

CERN

November 12, 2018

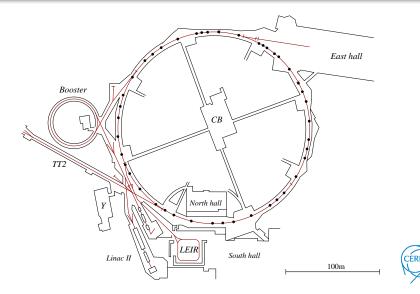

#### The PS Trajectory Measurement System uses 43 BPMs

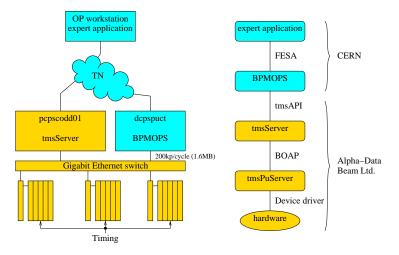

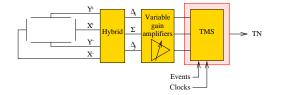

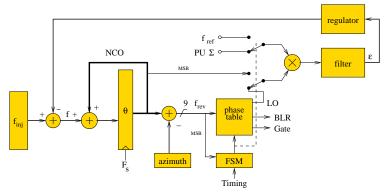

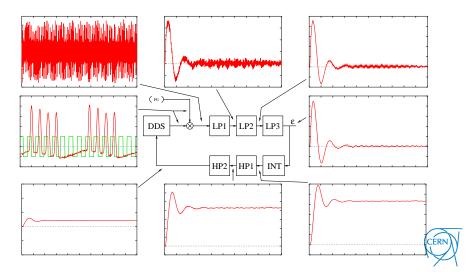

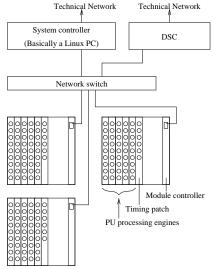

#### TMS architecture for one BPM station

#### Beam-synchronous signal generation

## Beam-synchronous signal generation

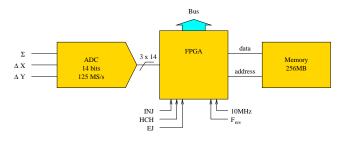

#### Direct Digital Synthesizer (DDS)

- NCO always runs at F<sub>rev</sub>

- Update rate 125 MHz

- Phase table generates LO and Gate

- Timing-driven programmable FSM selects one of several possible LO and Gate signals

- FSM also controls BPM and Fref signal routing

- Azimuth defines BPM position in ring

- $F_{inj}$  provides  $F_{rev}$  at beam injection

- Regulator provides frequency and phase tracking

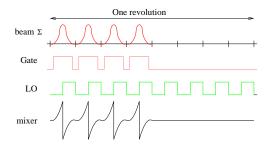

#### Beam-synchronous signals

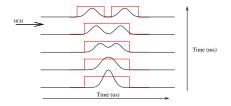

Goal: Measure position of the centre of charge of each bunch

For each of the signals ΔX, ΔY and Σ, integrate over bunch length

• Bunch position =

$$S \frac{\int \Delta}{\int \Sigma}$$

- Gate selects samples belonging to a bunch

- LO serves to derive a phase correction

- A mixer creates a phase error signal

- Can lock on (sub)harmonics

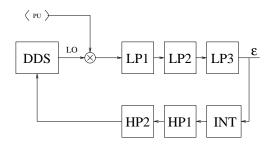

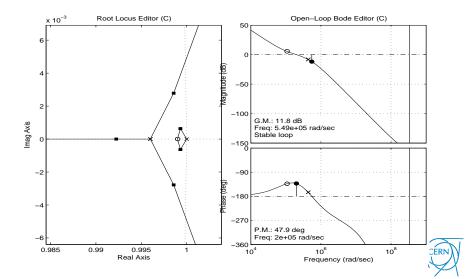

#### Phase loop dynamics

#### Discrete-time feedback loop

- In the locked steady state, LO and BPM signals are in quadrature

- The regulator design enforces a zero static phase error

- Beam intensity and number of bunches affect the loop gain

## Sequencing

#### Programmable Finite State Machine

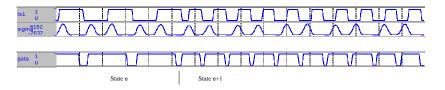

- Each state has associated Gate and LO signals and switch settings for the mixer inputs

- Sequence defined by a programmable transition table

- For each state and timing impulse, it specifies the next state

- Each state specifies a block of trajectory memory

- An event table records information about the location, size and structure of these blocks

- There is room for four of these tables, so we have time enough to read the interesting bits

## Splitting a bunch into 2

9/28

#### Splitting bunches into 2

Jeroen Belteman

10/28

## Splitting a bunch into 2

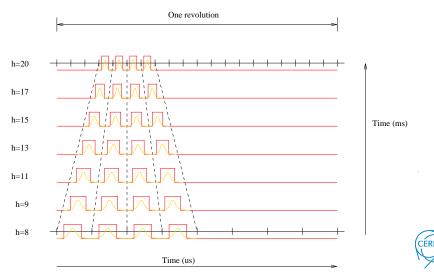

- A single Gate covers both bunchlets until splitting is nearly complete

- Even though splitting is gradual, the TMS switches instantly

- The switch is done on a turn boundary, starting from the injection BPM and propagating around the ring in synchronism with the beam

- A timing pulse derived from LLRF decides the appropriate instant

## Splitting bunches into 2

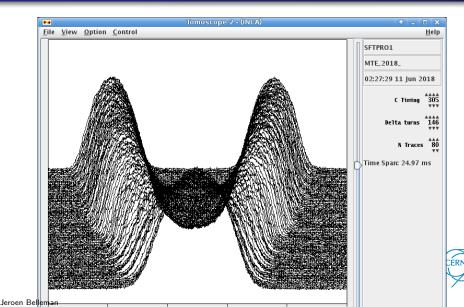

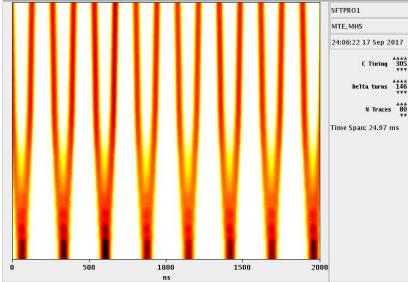

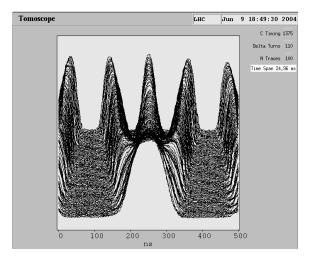

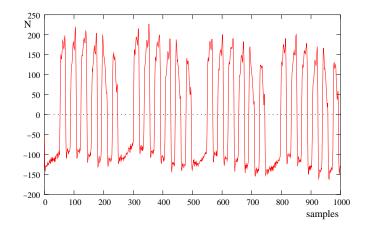

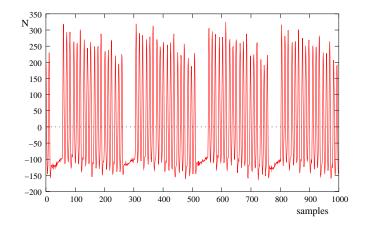

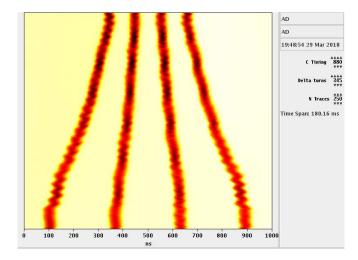

#### Measured on the live system

A timing signal advances the FSM to select the new harmonic when splitting is almost complete. LO and Gate signals assume their new waveforms.

#### Splitting bunches: Frequency domain view

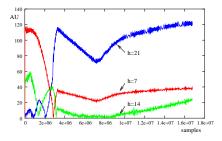

#### Amplitude of spectral lines over time during bunch splitting

- During the split, the magnitude at the original harmonic drops while the new one grows (This is a split into *three*!)

- Residual levels at the 'wrong' harmonic persist, but are unreliable

- Switching occurs at the cross-over of h=7 and h=21

## Splitting a bunch into 3

#### Beam on h=7

• Six bunches injected on h=7

## Beam on h=21

- Bunches are split into 3

- Eighteen bunches on h=21

## Splitting a bunch into 3

#### Acquired on the live system

Alignment gets better as splitting progresses.

Jeroen Belleman

17/28

Bunch-by-Bunch position measurement for the CERN-PS: coping with RF-gymnastics

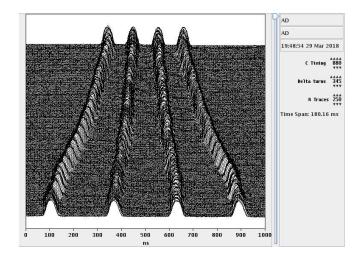

#### Batch compression on AD

Bunch-by-Bunch position measurement for the CERN-PS: coping with RF-gymnastics

#### Batch compression on AD

#### Batch compression

## Summary

- The TMS is very flexible

- Records both orbits and trajectories of all bunches over complete acceleration cycles

- Delivers multiple subsets of data to multiple independent users

- No settings under user control

- BPMs, pre-amplifiers, timing hardware made in-house

- TMS was built by British industry

- Only the ADC/FPGA modules are custom-made hardware

- Custom software and firmware

- Crates and computers are COTS

#### End

## Thank you

Jeroen Belleman

22/28

Bunch-by-Bunch position measurement for the CERN-PS: coping with RF-gymnastics

Spares

## Small signal transfer function

#### The open loop transfer function:

$$H_o = \frac{hz^{-1}}{A(1-z^{-1})} \cdot H_m \cdot \left(\frac{z^{-1}}{1-0.996z^{-1}}\right)^3 \cdot \frac{(1-0.999z^{-1})^2}{1-z^{-1}} \cdot z^{-n}.$$

(1)

#### The closed loop transfer function:

$$H_c = \frac{H_o}{1 + K_R H_o}.$$

(2)

System dynamics determined by the poles of  $H_c$

## Root locus of PLL

#### PLL loop frequency step response

#### Data block summaries

| 2302            | :     | SH8  | 3  |         |         |         |

|-----------------|-------|------|----|---------|---------|---------|

| period          | start | end  | h  | bunches | mask    | n       |

| 0               | 0     | 986  | 0  | 0       | 0x00000 | 3090574 |

| 1               | 5     | 95   | 8  | 1       | 0x00080 | 20968   |

| 2               | 171   | 986  | 8  | 8       | 0x000ff | 3069606 |

| []              |       |      |    |         |         |         |

| 2305: SH16-21LI |       |      |    |         |         |         |

| period          | start | end  | h  | bunches | mask    | n       |

| 0               | 0     | 1351 | 0  | 0       | 0x00000 | 1774291 |

| 1               | 5     | 95   | 8  | 1       | 0x00002 | 21671   |

| 2               | 236   | 376  | 16 | 2       | 0x00003 | 76780   |

| 4               | 376   | 396  | 14 | 2       | 0x00003 | 13444   |

| 5               | 396   | 441  | 12 | 2       | 0x00003 | 30248   |

| 6               | 441   | 466  | 24 | 4       | 0x0000f | 33608   |

| 7               | 466   | 1351 | 21 | 4       | 0x0000f | 1598540 |

#### Hardware setup

8-slot cPCI

CÈRI

#### Hardware and software organization