### **BIS 2v0 - Proposal**

I. Romera Ramírez on behalf of the BIS team

### Content

Motivation to upgrade the BIS

Proposed hardware/software upgrades

Planning

Conclusions

Obsolescence, new requirements and maintainability

### Obsolescence, new requirements and maintainability

Aging - limited spares, new installations and support up to the end of HL-LHC

Discontinuity of critical electronic components - Xilinx CPLD XC9500 and FPGA Spartan 3

Full occupancy of FPGA logic cells - no space for implementing new functionalities

Wiener VME crate with redundant power supplies not supported anymore

### Obsolescence, new requirements and maintainability

- User interface concentrator request to interface PCs in injectors, see talk from <u>B. Todd</u> and <u>D. Nisbet</u>

- Common interface between BIS and actuators request to remove complexity of having to decode the Beam Permit frequencies (BE-RF, TE-EPC...)

- Add FALSE frequency to Beam Permit signal request to mitigate glitches in DC operation (TE-ABT), see talk from R. Secondo

- Consider beam-beam effects in the way beam permit loops are linked, see talk from <u>C.</u>

<u>Wiesner</u> and <u>D. Wollmann</u>

### Obsolescence, new requirements and maintainability

- Increase number of user permit connections to the BIS

- Improve flexibility of user permit configurations maskable /unmaskable, single/both beams configurable on demand...

- Improve optical transmission power budget and diagnostics

- Consider timing events as user inputs e.g. timing destinations as user permits

- Encoding Beam Permit on packets? See next slide

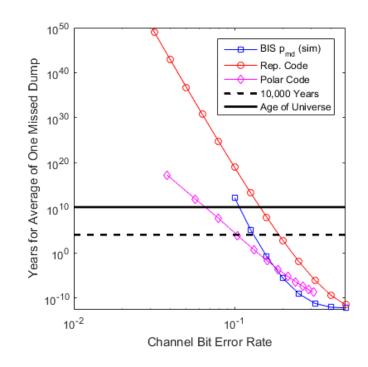

### Frequency vs packet-based solution

- Launched study to compare existing optical solution with some packet-based solutions

- Advantage is that additional information could be transmitted over the same fibres (monitoring, etc)

- Study compares frequency vs error-correction codes (n-repetition and polar codes)

- Existing solution uses signals of 32 edges within a window of 128 samples

- Repetition code that transmits 32 copies of an information bit within a window of 128 samples

- Polar code that transmits 32 encoded bits within a window of 128 samples

#### Conclusions:

- 1. Existing solution is more than adequate in terms of safety and availability

- 2. In principle, transmission of additional information cannot improve reliability

- 3. Packet-based solution requires packet-level synchronization and specialized signal processing algorithms

- 4. Good practice to separate the safety critical signals from diagnostics

Courtesy: A. Balatsoukas

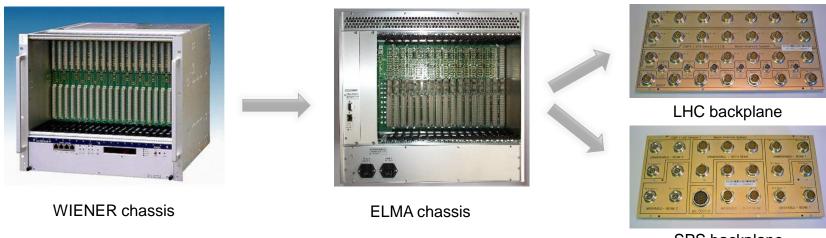

### HW upgrades – Platform

- BE-CO committed to support VMEbus for HL-LHC era (see <u>J. Serrano's contribution</u>)

- BE-CO advised not to move to other platforms such as PXI or uTCA

- VME64x fulfil requirements in terms of bandwidth and latency for BIS 2v0

- Assuming we keep VME => replacement of WIENER by ELMA chassis

- Side effects:

- Reduced number of available slots (17 in ELMA vs 21 in WIENER)

- New backplane design for both LHC and SPS (keep connectors compatibility?)

SPS backplane

## HW upgrades – CIBM/CIBX

Manager/Master boards combine user permits to derive two redundant beam permits

#### At present

- Physical separation for critical code and monitoring

- Obsolete electronic components and CPLD + FPGA at the limit of its capacity

#### For BIS 2v0

- New board to improve limitation on user inputs

- Increase number of inputs Trade-off between complexity and nb. of controllers

- Improve flexibility Configurable inputs (masking/unmasking, single/both beams)

- Integrate SFP transceivers Improved optical budget, diagnostics and maintainability

- Introduce FALSE frequency for beam permits

- Merge remote diagnostics from CIBT board

- Improve routing of timing destinations e.g. LINAC4

- Generator (CIBG) and Re-trigger (CIBDS) boards will be based on same HW design

CIBX

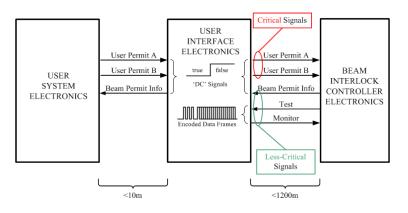

### HW upgrades – User interfaces

#### At present

- Unique hardware interface for all BIS users (CIBU + CIBF) => ~400 units in operation

- Safety critical implementation relies on current loops and analog electronics

- XILINX XC9500 CPLD is obsolete

#### For BIS 2v0

- Redesign hardware interfaces following backplane redesign? Cost, impact, backward compatibility...

- Need of concentrator to gather multiple user connections (e.g. PCs in LHC injectors)

- Investigate the need of radiation tolerant design (CPLD, optocoupler, power supplies, RS485 transceivers some of them installed close to the beam, e.g. RRs)

**CIBUS**

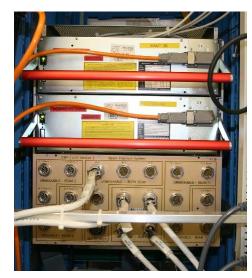

## **HW** upgrades – Optical transceivers

#### At present

- Two boards used for optical communications CIBO and CIBL

- CIBO (ELED) transceiver for beam permit frequencies limited power budget and lack of monitoring

- CIBL (LASER) transceiver for user permit signals over long distances (e.g. used in CIBF for both BIS and SMP) –

high power budget and enhanced diagnostics

#### For BIS 2v0

- New CIBSFP board to overcome the limitations of the present CIBO

- SFPs provide high power transmission and reception sensitivity, enhanced diagnostics and better maintainability

- Plans to replace CIBL by CIBSFP and maintain a single optical transceiver

**CIBSFP**

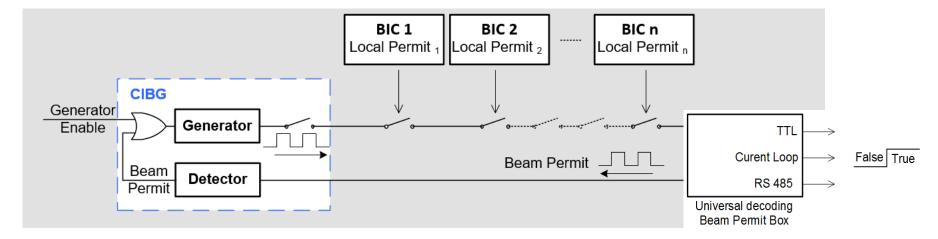

### HW upgrades – Interface to actuators

#### At present

- Beam Permit signals delivered through optical links

- Actuators are responsable for decoding a frequency (using a CIBO) to derive the Beam Permit e.g. TSU in LBDS

- Alternatively, Beam Permit signals can be delivered through a differential signal transmission and translated to TTL (using a CIBIR) - e.g. RF source in LINAC4

#### For BIS 2v0

- Due to the diversity of actuators (TE-ABT, BE-RF, TE-EPC...) -> develop a unique interface box in charge of

decoding the frequencies and delivering the Beam Permit in various standards (TTL, differential, current loop...)

- Standard interface to all

- Reliable decoding of Beam Permit frequencies

- Diagnostics available

## **HW upgrades - CISV**

#### At present

- Board used to decode SMP flags from GMT (e.g. Setup Beam, Beam Presence, Stable Beams...)

- LHC BICs receive the Setup Beam Flag with a CISV board

- CISV board is based on a CTRV with dedicated firmware maintained by MPE-MI

#### For BIS 2v0

- An option could be to port the CISV firmware to the new CTRVD (from BE-CO)

- Or develop a new board taking into account possible new flags (i.e. SMP 2v0)

**CISV**

**CTRVD**

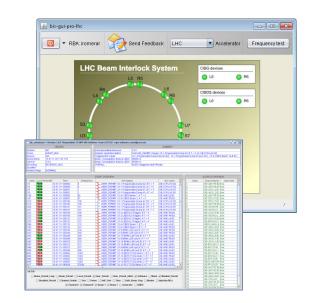

## Testbeds + Software upgrades

Upgraded hardware will require **new hardware/functional** test benches:

- CIBM/CIBX test bench

- CIBG/DS test bench

- CIBU test bench

- CIBIT & CIBIR test bench

- CIBSFP tester

- + python expert tools for hardware debugging

#### ... and controls:

- FESA classes required for CIBM/X/DS/G

- Configuration DB + API

- Supervision tools

- Pre-operational checks

- Post-Mortem tools (e.g. BIS-ISA and BIS-IPOC)

- Sequences (e.g. rearming, ACC\_TEST...)

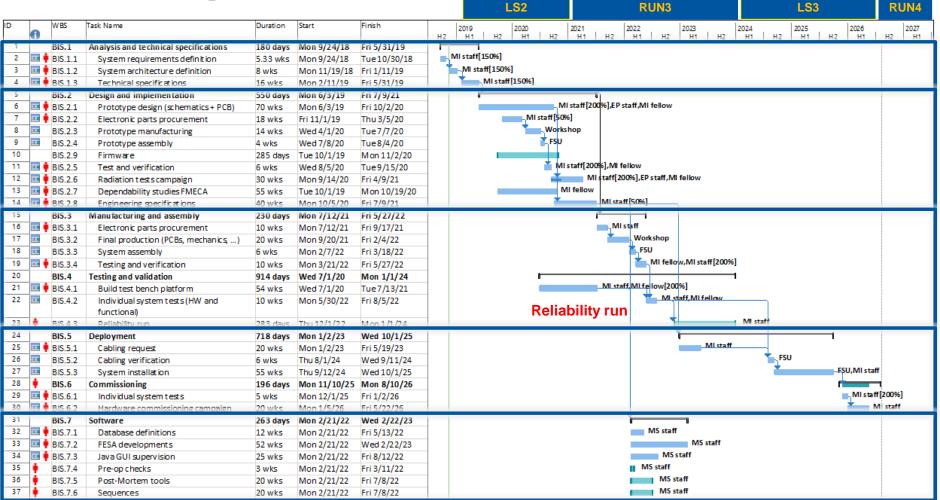

# **Planning**

Definition of requirements

Design and implementation

- HW prototypes

- Firmware

- Test and verification

Testing, validation and manufacturing

- Build testbeds

- Launch production

- Reliability run in 2023

Deployment & commissioning

- Cabling

- Installation

# **Summary**

Functional requirements for BIS 2v0 remain almost identical to the present system

System upgrade needed to address obsolescence, improvements and long-term maintainability to ensure smooth operation for the HL-LHC era

Synergies with SMP 2v0 and technical solutions may have an impact on the interfaces with users and actuators

BIS 2v0 must be ready for reliability run in 2023/24 and sitewide deployment during LS3 (2024/25)

# **Spare slides**

# **BIS** inventory

| Board name | Description                       | Operation | Spare |

|------------|-----------------------------------|-----------|-------|

| CIBM       | Manager board                     | 79        | 15    |

| CIBX       | Master board                      | 5         | 5     |

| CIBG       | Frequency generator board         | 10        | 1     |

| CIBDS      | Retrigger board                   | 2         | 4     |

| CIBV       | Post Mortem board                 | 1         | 2     |

| CIBWS      | Setup Beam board                  | 1         | 2     |

| CIBUS      | Single user interface             | 304       | 45    |

| CIBUD      | Double user interface             | 49        | 8     |

| CIBD       | DC power supply                   | 832       | 133   |

| CIBFU      | Laser user interface - User       | 36        | 5     |

| CIBFC      | Laser user interface - Controller | 36        | 5     |

| CIBO       | Optical transceiver               | 245       | 24    |

| CIBL       | Laser optical transceiver         | 89        | 45    |

| CIBIT      | Differential transmitter board    | 3         | 1     |

| CIBIR      | Differential receiver             | 6         | 25    |

| CIBPB      | Patch panel for diff. transmitter | 3         | 2     |

| CIBPT      | Patch panel for diff. receiver    | 6         | 14    |

| CIBT       | Test and Monitor board            | 68        | 7     |

| CIBMD      | Manager display                   | 79        | 15    |

| CIBTD      | Test and Monitor display          | 68        | 14    |

| CIBPS      | Patch panel for SPS               | 20        | 14    |

| CIBPL      | Patch panel for LHC               | 19        | 2     |

| CIBB       | Distribution bay                  | 30        | 0     |

| CIBEA      | Extension type-A                  | 156       | 20    |

| CIBEB      | Extension type-B                  | 78        | 17    |

Safety critical electronics

Safety critical electronics for interface with users

Optical transceivers

Safety critical electronics for interface with actuators

Monitor and diagnostics

Patch panels and interface boards

More than 2000 electronic boards currently in operation!

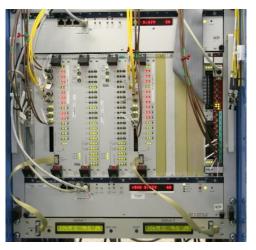

### **Present BIS hardware**

- Hardware based on VME-architecture

- Critical functionality is hardware only

- Physical separation for critical/monitor functions

- Remote update of monitor but not critical code

- Redundant critical path for high safety

- Redundant power supplies for high availability

- Modular design for flexibility

User interface (CIBU)

**BIC** front view

**BIC** rear view