# Status on TRAMOS (Trapping MOS) and DotPix (Quantum Dot Pixel) ongoing developments Nicolas T. Fourches, IRFU/CEA Saclay, 91191 GIF/YVETTE, France E-mail: <u>nicolas.fourches@cea.fr</u> Charles Renard (C2N) and G. Hallais, Francois Jomard (GEMAC), Francois

**Olivié and coworkers (LAAS), the EMIR network (Jannus/Saclay)**

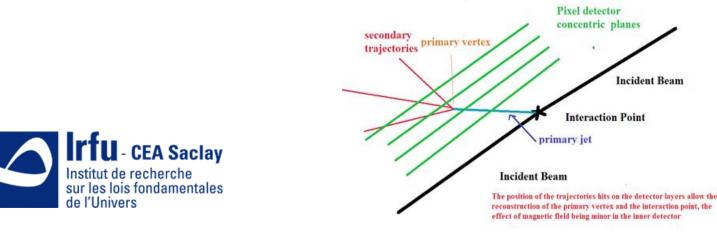

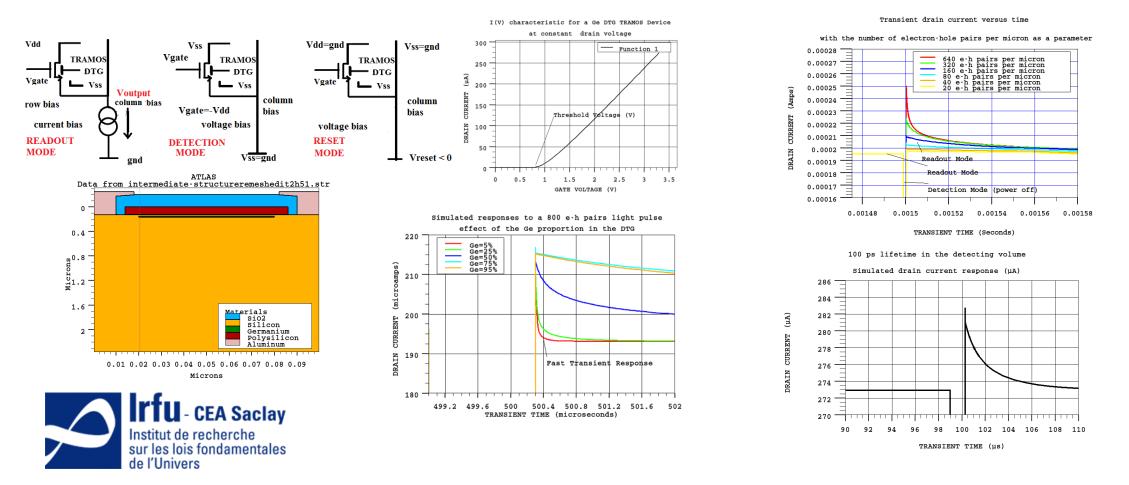

The purpose of the DotPix project is to design a new kind of pixel for inner vertex detectors arrays with enhanced point-to-point resolution. It is based on a single MOS device, which may allow a resolution below the micron making track reconstruction and vertex determination with an unprecedented accuracy. It comprises a buried gate, which acts as a charge-collecting electrode with memory effect and controls the current of a micron-size n-channel MOS transistor. The design of such a pixel requires the massive use of device simulations. Future e+e- colliders (FCC,ILC) will benefit from this development.

# I. Motivations for a new pixel design

**II.** How a buried gate can act as collecting electrode

III. How it can operate as a memory

IV. Designing and fabricating the buried gate

V. Simulation results

VI. Technological progress

VII.Summary and further work

E-mail: <u>nicolas.fourches@cea.fr</u>

# I. Motivations for a new pixel design

- Future trackers and vertex detectors need accurate track reconstruction and precise vertex determination down to the micrometer

- This is a prerequisite for the e+e- colliders in the future

- Fast response should be also sought for bunch identification, this means accessory detector

- High radiation hardness is still a challenge however less constraining with respect to hadron colliders

- This impose to reduce the area of each pixel, increase the number of pixel per unit area

- Low hit rate per pixel, in favor of reduced data flux by data compression, low multiple hit rate, limited single pixel area

- High pT events ( infinite < h < 0), h=-ln (tan( $\theta/2$ )) pseudorapidity, where  $\theta$  is the angle w.r.t. incident beam

# I. Motivations for a new pixel design

- Classic and modified CMOS pixels, in many cases too slow, need depleted area to be fast (three transistors at least) NIEL tolerance bad in many case due to diffusion the solution has been DMAPS (with highly resistive substrates)

- CCD could be reduced in size but not random addressable.

- DEPFET is single device, but should be improved in terms of size

- We need a monolithic depleted device with low power consumption, with downscaling possible

- Pixel need local readout and memory and a depleted diode, this means many transistors and pixel size > 1 micron squared

- We propose to combine every function in a single device pixel : one device + memory in a CMOS compatible process , with a target of 100 nm feature line, and 10 micrometer in depletion layer thickness

- Up to now no submicron pixel for charged particle detection has been operating, sizes above 10 x 10 micrometers, this could improve by CMOS downscaling but still need many transistors.

II. How a buried gate can act as collecting electrode

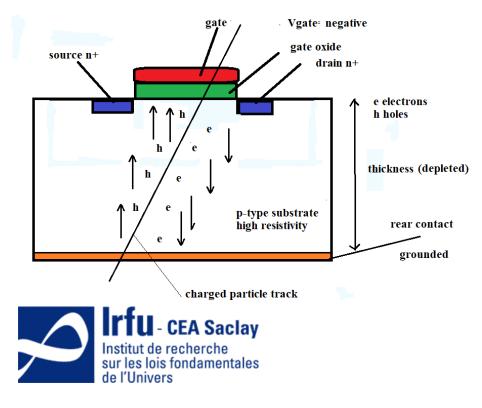

- A charged particle make a track in the silicon bulk along the vertical or inclined

- We start from a MOS structure, which can be reduced to a MOS capacitor

- The thickness of the depleted zone 5  $\mu$ m to a fen tens of  $\mu$ m : need for thinning or implanted zone

- With a negative bias on the gate the holes accumulate under the gate oxide and the electrons are evacuated into ground

- This operation is close to that of a CCD

- Source and drain may be floating during this operation phase

- There is no permanent leakage because of the insulated upper gate only a displacement current during charge migration which should be fast :  $v_h = 10^7 cm s^{-1}$  for thickness : *thickness* =  $10^{-3} cm$ , drift time is  $\tau = 0.1$  ns

- No use at this stage, but we can introduce a buried control gate.

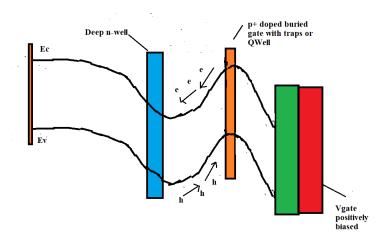

# II. How a buried gate can act as collecting electrode

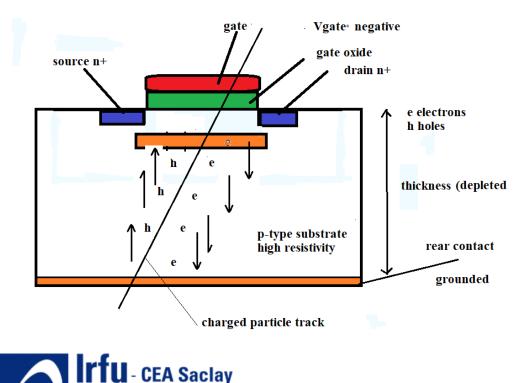

- A buried gate is introduced below the channel

- With a negative bias on the upper gate the holes accumulate in the buried gate , whereas the electrons are evacuated

- The buried gate should act as a potential well for the hole and not for the electrons

- The buried gate should also retain the holes during a long enough time

- The same holds for the collection time and the permanent leakage current

- Source and drain may be floating during this operation phase

Institut de recherche sur les lois fondamentales

de l'Univers

# II. How a buried gate can act as collecting electrode

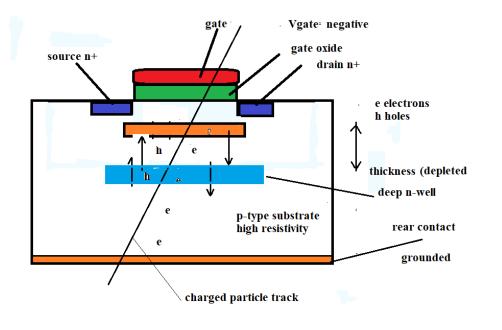

- Alternative design with a deep-n-well used for electron/hole separation

- The MOS structure can be operated with a slightly positive bias on the upper gate

- The buried gate is made of a high density of holes traps

- A deep impurity can be used for creating the trap zone

- The thickness in which the useful electron-hole pairs are created is limited (1micrometer), transition region of the buried gate/ deep n-well region

- Source and drain can be bias during this phase

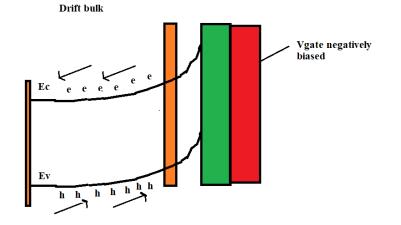

- This is the first version of the TRAMOS (2010)

## **II.** How a buried gate can act as collecting electrode

1. The zone between the deep-n-well and the buried gate enable the drift of holes towards the buried gate

2. In the absence of deep n-well the holes drift towards the buried gate. This impose that the upper gate should be negatively biased. High resistivity p-type substrate.

3. We could use the version 2 with a p-channel MOSFET operating permanently with a negative upper gate bias

E-mail: <u>nicolas.fourches@cea.fr</u>

## II. How a buried gate can act as collecting electrode

27/11/2018

Nicolas T. Fourches (IRFU) ,RD50 33rd Workshop , CERN 2018

Nicolas T. Fourches, IRFU/CEA Saclay, 91191 GIF/YVETTE, France

E-mail: <u>nicolas.fourches@cea.fr</u>

# III. How it can operate as a memory

- We need a buried gate that act as a control gate for the channel current with the ability to retain its hole charge sufficiently long to enable readout. This means the device should act as a memory.

- 1) First use a shallow doped p-type buried with a high concentration of deep impurities (such as Zn) which selectively trap hole and not electrons. Substitutional Zn is double hole trap. Problem how to get a high peak substitutional Zn concentration with no contamination ? Implant +RTP.

- 2) Second use a Quantum Well for holes, not for electrons.

- In the first solution the thermal emission rate for holes trapped on impurity sites determines the retention time for holes.

- In the second solution, hole emission to the VB of silicon and other mechanism set the retention time.

- In any case device simulation is the way to evaluate the functionality of the proposed devices as a way to make a proof of principle.

Nicolas T. Fourches, IRFU/CEA Saclay, 91191 GIF/YVETTE, France E-mail: nicolas.fourches@cea.fr

# IV. Designing and fabricating the buried gate

- Zn can be implanted in the bulk silicon during the process of the n-channel MOS transistor

- High energy ion implantation can be used but beware of contamination (1MeV energy)

- But disappointing DLTS results , concentration do not match>> Fermi level pinning

- Substitutional Zn acts as a deep double hole trap

= p-Si-SD

sigma = 2.71E-15 cm

= 4.42E+12 c

8.00E-03

= 2.00E+13 cm

- Needs stabilizing the buried layer (annealing)

- Needs a sharper profile

54.2

53.8

53.4

Zn SIMS profile in silicon

1 500

DEPTH (nm)

690 nm peak

Oxygen incident ion

Gaussian adjustment

2 000

2 500

3 000

1.0x101

Z 1,0x10<sup>17</sup>

1,0x1016

1,0x1015

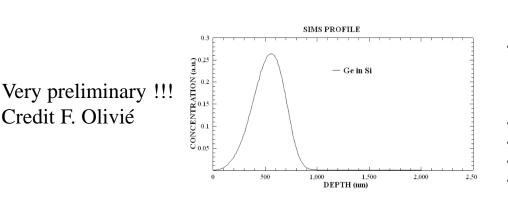

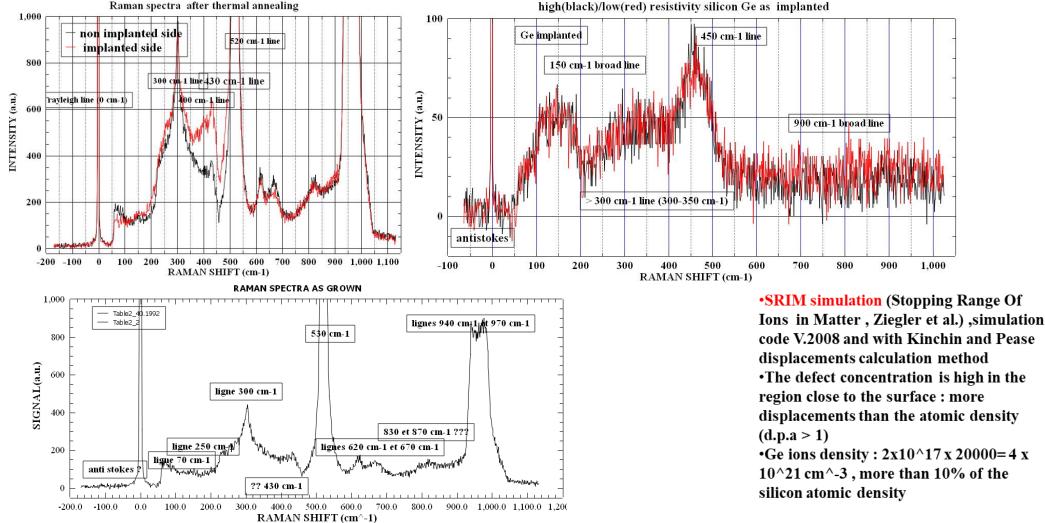

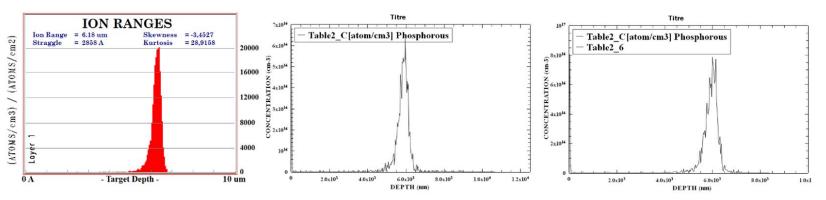

- Ge has been implanted at 1MeV with high doses, the maximum concentration obtained in the samples is 25% with a lot of scatter (down to 6%), the concentration profile is not sharp but in accord with SRIM simulations

- No thermal anneal, was performed after implantation

- High dose implantations are take to much time !!!

- Could be used however

3 000,0

SIMS Zn profile

2 000.0

**DEPTH** (nm)

HR-cesium-incident-ion

**Gaussian Adjustement**

This is for high resistivity silicon, similar results are obtained on low resistivity silicon

2.90

1000/T [1/K] --

# Ion implantation : EMIR/Jannus Saclay (MeV range ) SIMS : GEMAC

A 1,0x101

ONCENTRATION NOT 1'021012 NOT 1'021012 NOT 1'021012 NOT 1'021012

1,0x101

0,0

705 nm peak

1 000,0

(cm-

Nicolas T. Fourches, IRFU/CEA Saclay, 91191 GIF/YVETTE, France

E-mail: nicolas.fourches@cea.fr

27/11/2018

Density gradient approximation (Quantum Moments Model) : transport properties for quantum level simulations Density Gradient (Quantum Moments Model);

See:

Andreas Wettstein, Andreas Schenk, and Wolfgang Fichtner, Fellow, IEEE, 'Quantum Device-Simulation with the Density-Gradient Model on Unstructured Grids', IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 2, FEBRUARY 2001, 279 and references herein: Transport equation from reference above  $\vec{J} = qD_n \nabla n - \mu_n n\nabla (\phi + n) + f(n)$

With  $\cap$  is a quantum correction potential which is a function of n and h and the carrier effective mass and f(n) a vector function of the electron density

What we must take into consideration by TCAD :

- Quantum channel confinement simulation

- Thin gate oxide MOS capacitors and transistors

- Small geometry heterojunction diodes (QW are this case)

- Confinement of carriers / electron wave functions extension

- This model is based on the moments of the Wigner function equations-of motion (perturbation approximation, in a way semi-classical) which consists of quantum correction to an hydrodynamic model

- No need to determine stationary solution to Schrödinger equation as with Poisson-Schrödinger method, hence better for transient behavior.

- Both holes and electrons are considered in the transport process : very important with the DotPix !!!

- Purely classical simulations were made showing that quantum simulations introduce only limited corrections

V. Simulation results

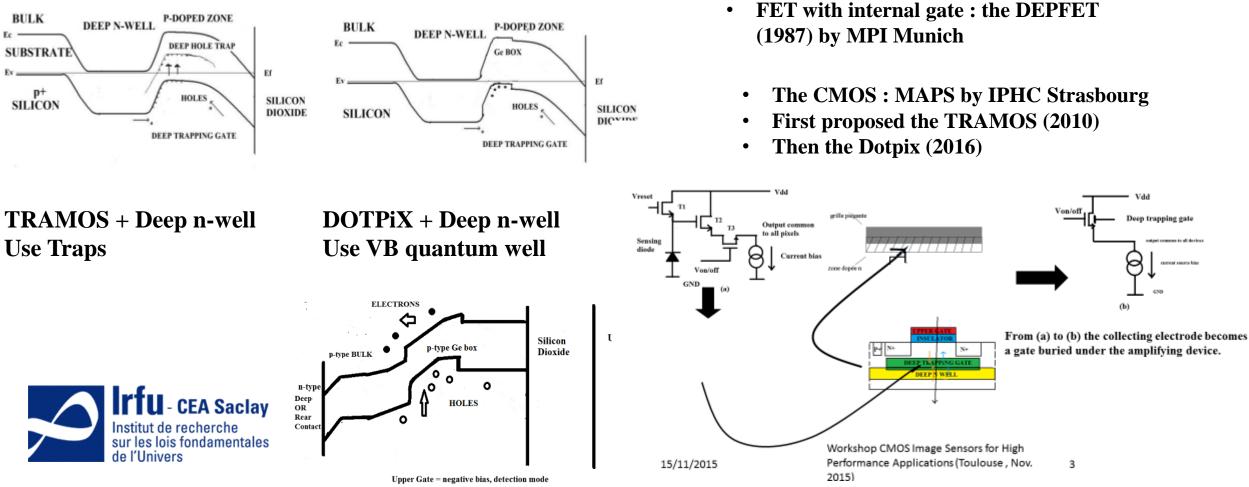

Focus on the Quantum Well design (results have been published) Germanium layer in the first figure, the thickness of the structure is set to 10 mm in the simulation file. Quantum density gradient simulations

27/11/2018

E-mail: nicolas.fourches@cea.fr

# V. Simulation results

| Pixel Size (μm²) X<br>Thickness (μm) | E <sub>avg</sub> (keV) | E <sub>MPV</sub> (keV) | Ratio avg (%)<br>(E <sub>N</sub> /E <sub>p</sub> ) <sup>*</sup> | Efficiency (E <sub>Th</sub> =<br>500eV) |

|--------------------------------------|------------------------|------------------------|-----------------------------------------------------------------|-----------------------------------------|

| 1*1*10                               | 3.28                   | 2.17                   | 4.74                                                            | 99.3                                    |

| 1*1*20                               | 6.76                   | 4.89                   | 4.9                                                             | 99.82                                   |

| 1*1*30                               | 10.86                  | 7.84                   | -                                                               | >99                                     |

| 1*1*40                               | 14.36                  | 9.68                   | -                                                               | >99                                     |

| 1*1*50                               | 17.98                  | 13.21                  | -                                                               | >99                                     |

| 10 * 10 * 10                         | 3.26                   | 2.15                   | 0.994 1                                                         | 99.9                                    |

| 10 * 10 * 50                         | 16.68                  | 13.17                  | 2.08                                                            | >99                                     |

| 10 * 10 * 100                        | 34.76                  | 24.3                   | 2.35                                                            | >99                                     |

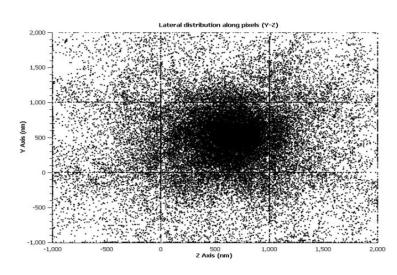

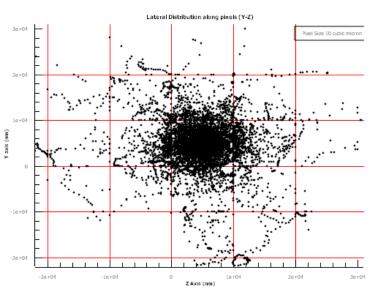

GEANT4 on a 1µm x 1µm x 10µm structure, Scattered Hits on the Silicon Layer : 130 GeV pions (credit to V. Kumar, Saclay, 2016, M2 report)

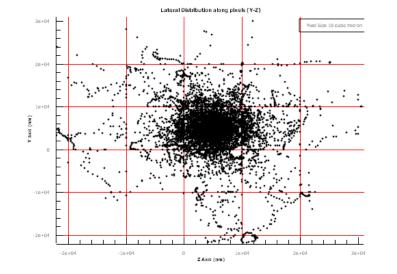

The same on Pixel Size 10 µm \*10 µm, Thickness 10 µm:

Wafer Thinning is necessary, detection efficiency remains good enough for thicknesses of 10 micrometers

Nicolas T. Fourches, IRFU/CEA Saclay, 91191 GIF/YVETTE, France

E-mail: <u>nicolas.fourches@cea.fr</u>

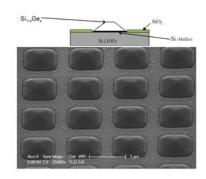

# VI. Technological progress

- Alternative to ion-implantation

- UHV/CVD of SiGe on a silicon substrate grown on the whole wafer surface

- Si/ grey and Ge/blue

- Pseudomorphic layer (4%, lattice mismatch between Ge and Si)

- Ge lattice constant : 0.565 nm and Si : 0.5431 nm

- Normally Ge/Si compressively strained

- Ge >> 20 nm metastable or relaxed

- C2N equipement

Selectively etched and grown

**SRIM** (Stopping and Range of Ions In

(Secondary Ion Mass Spectroscopy,

energy (14 MeV in silicon ) for Deep-

n-well, at 5  $\mu$ m below the surface, no

equipement)

implanted

and

SIMS

at high

for

simulations

Matter)

GEMAC

**Phosphorous**

need for high doses.

(a)-(b) : Ge ( % ? ) épaisseur ?? (b)-(c) : Si buffer layer épaisseur ??

# VII.Summary and further work

- Device simulations have been extended to the case of p-channel device and are encouraging

- Characterisation of Si/Ge/Si epi layers are under way. These were made at C2N by Charles Renard and coworkers

- Work is under way to make a MOS process with reduced thermal budget, to limit inter diffusion

- Participating institutes are welcome, and people too, for simulation, modelling , characterisation and technology

- The project is open, some collaboration with DEPFETor CMOS researchers would be particularly appreciated

- ILC and FCC would benefit from this R&D , joint R&D ?

- Work with facilities or laboratories with material characterisation competences is sought: ion implantation, SIMS, RBS, electrical measurements such DLTS, epitaxial growth and CMOS processing, this would contribute to accelerate the developments along with irradiation facilities

Contributions from : Charles Renard (C2N) and G. Hallais, Francois Jomard (GEMAC), Francois Olivie and coworkers (LAAS), the EMIR network (Jannus/Saclay) with G.Gutierrez Jannus: Joint Accelerators for Nano and Nuclear Science); C2N Centre de Nano Science et de Nanotechnologies Laboratoire d'Analyse et d'Architecture des Systèmes; GEMAC (Groupe d'Etude de la Matière Condensée)

# • Work published up to now:

- N. Fourches, Y. Degerli, M.Besançon, A.Besson, G. Claus, G. Deptuch, W. Dulinski, M. Goffe, A. Himmi, Y. Li, P. Lutz, F.Orsini, M. Szelezniak.. (2005, October). "Performance of a fast programmable active pixel sensor chip designed for charged particle detection". In *IEEE Nuclear Science Symposium Conference Record*, 2005 (Vol. 1, pp. 93-97). IEEE. <u>http://dx.doi.org/10.1109/NSSMIC.2005.1596214</u>

- NT. Fourches, "Device simulation of Monolithic Active Pixel Sensors: Radiation damage effects", Nuclear Science Symposium Record, Pages 2523-2529, IEEE Transactions On Nuclear Science, Vol. 56, No.6, December 2009, Pages 3743-3751, <u>http://doi.org/10.1109/TNS.2009.2031540</u>

- Nicolas T. Fourches, "Ultimate Pixel Based on a Single Transistor With Deep Trapping Gate", IEEE Transactions On Electron Devices", Volume 64, Issue 4, (2017) 1619-1623 <a href="http://doi.org/10.1109/TED.2017.2670681">http://doi.org/10.1109/TED.2017.2670681</a>

- N. Fourches, E. Orsier, J du Port de Pontcharra, R. Truche, "Design and test of elementary digital circuits based on monolithic SOI JFETs", IEEE Transactions on Nuclear Science Vol 45 N° 1 February 1998, <u>http://dx.doi.org/10.1109/23.659553</u>

- Nicolas T. Fourches, "A novel CMOS detector based on a deep trapping gate", Nuclear Science Symposium Conference Record (NSS/MIC, 2010), p 655-658, 2010, Knoxville, Tennessee: <u>http://dx.doi.org/10.1109/NSSMIC.2010.5873840</u>, Nicolas Fourches, "Semiconductor device ", U.S. Patent No. 7,936,018. 3 May 2011

- Vishant Kumar, Master II, Thesis, Ecole des Mines de Nantes, defended September 2016, available on request at IRFU

- N. T. Fourches, & W. Vervisch, (2016). "Simulations of a silicon pixel based on MOS Deep Trapping Gate Principle, arXiv preprint arXiv: 1602.00263. http://arxiv.org/abs/1602.00263

$$e\vec{j} = -\mu k_B T \nabla n - \mu n \nabla (\Phi + \Lambda)$$

$$\Lambda = \frac{\hbar^2 \beta}{12m} \left[ \nabla^2 \Phi - \frac{\beta}{2} (\nabla \Phi)^2 \right]$$

$$e\vec{j} = -\mu k_B T \nabla n - \mu n \nabla \Phi - \mu \left( \nabla \frac{\hbar^2 n}{4mk_B T} \cdot \nabla \right) \nabla \Phi_q, \quad (1)$$

M. G. Ancona and H. F. Tiersten, "Macroscopic physics of the silicon inversion layer," Phys. Rev. B, vol. 35, pp. 7959–7965, May 1987.

M. G. Ancona and G. J. Iafrate, "Quantum correction to the equation of state of an electron gas in a semiconductor," Phys. Rev. B, vol. 39, no. 13, pp. 9536–9540, May 1989.

# **EXTRA SLIDES**

## Pixel Size 10 μm \*10 μm, Thickness 10 μm:

Appl. Phys. A 50, 151-156 (1990) Applied so,,,,

Physics A S"u'rf aces

© Springer-Verlag 1990

The Electrical Properties of Zinc in Silicon

S. Weiss, R. Beckmann, and R. Kassing

Institut fiir Technische Physik, Universit/it, D-3500 Kassel, Fed. Rep. Germany

Received 25 May 1989/Accepted 7 September 1989

Abstract. Electrically active deep levels related to zinc in silicon are investigated in n- and p-type silicon using Deep-Level Transient Fourier Spectroscopy (DLTFS) measurements. While in n-type silicon a level at Ec-0.49 eV is observed, the main zinc-related levels in p-type silicon are determined to be E v + 0.27 eV and Ev + 0.60 eV. The latter are associated with zinc situated on regular silicon lattice sites. The emission rate of these centers exhibits a field dependence which cannot be quantitatively explained with the Poole-Frenkel model. On the other hand, a shallow level at E v + 0.09 eV is observed only in boron-doped silicon which may be related to a zinc-boron complex. Other zinc-related levels are found at E v + 0.23 eV and Ev+ 0.33 eV, their concentration depending on that of zinc on substitutional sites. In addition, the evaluation of depth profiles and the analysis of the field dependence of the emission rate based on the DLTFS method is presented