# **Overview of design and evaluation of depleted CMOS sensors within RD50**

<u>E. Vilella</u><sup>a\*</sup>, O. Alonso<sup>b</sup>, T. Bergauer<sup>c</sup>, R. Casanova<sup>d</sup>, G. Casse<sup>a,e</sup>, A. Diéguez<sup>b</sup>, M. Franks<sup>a,e</sup>,

S. Grinstein<sup>d</sup>, C. Irmler<sup>c</sup>, R. Marco-Hernandez<sup>f</sup>, J. M. Hinojo<sup>g</sup>, N. Massari<sup>e</sup>, S. Moreno<sup>b</sup>,

F. Muñoz<sup>g</sup>, R. Palomo<sup>g</sup>, S. Powell<sup>a</sup>, H. Steininger<sup>c</sup>, J. Vossebeld<sup>a</sup>, C. Zhang<sup>a,e</sup>

<sup>a</sup>University of Liverpool <sup>b</sup>University of Barcelona <sup>c</sup>HEPHY <sup>d</sup>IFAE <sup>e</sup>FBK <sup>f</sup>IFIC <sup>g</sup>University of Seville

\*<u>vilella@hep.ph.liv.ac.uk</u>

## **RD50-MPW1 – Overview**

## **General details**

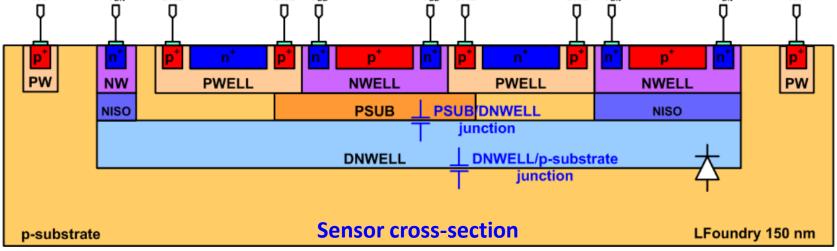

- MPW in the 150 nm HV-CMOS process from LFoundry

- To test the technology aspects of this process and novel designs

- Submitted in November 2017, received in April 2018

- Fabricated on wafers with 2 different substrate resistivities

→ 500 Ω·cm (40 samples) and 1.9k Ω·cm (80 samples)

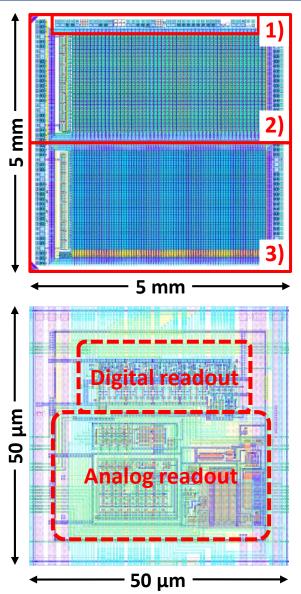

## **MPW contents**

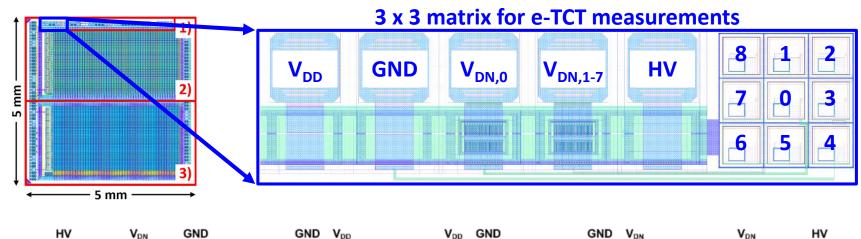

- **1)** Tests structures for e-TCT and sensor capacitance measurements

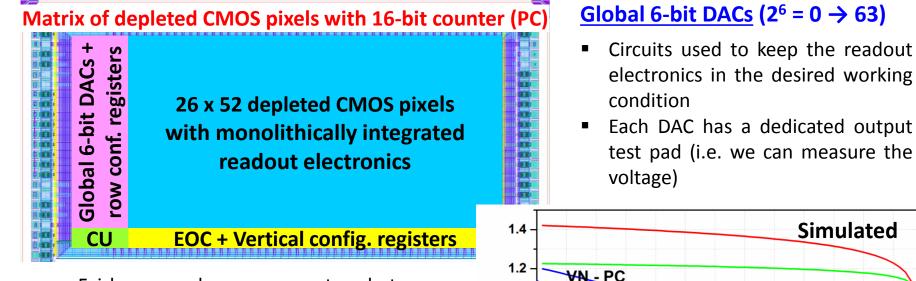

- 2) Matrix of depleted CMOS pixels with 16-bit counter

- ➔ 26 x 52 pixels

- → 75 µm x 75 µm pixel area

- 3) Matrix of depleted CMOS pixels with FE-I3 style readout

- → 40 x 78 pixels

- ightarrow 50  $\mu$ m x 50  $\mu$ m pixel area

- Analog and digital readout embedded in the sensing area

- Completely independent matrices

- Careful design with LF15A V1.2.0, the first design kit to include

- ➔ Models to simulate the sensing diodes

- ➔ Proper verification

## **RD50-MPW1 – Test structures**

- Pixel size is 50 μm x 50 μm

- No readout electronics

## **RD50-MPW1 – I-V**

- I-V of <u>central pixel</u> of test structure for e-TCT

- Measurement done using a probe station with sensor in complete darkness

- V<sub>BD</sub>~55-60 V as expected from design, but I<sub>LEAK</sub> is too high

- Doing TCAD simulations and getting support from the foundry to understand this problem

- The sensors are fully functional (see presentation by I. Mandic in this RD50 WS)

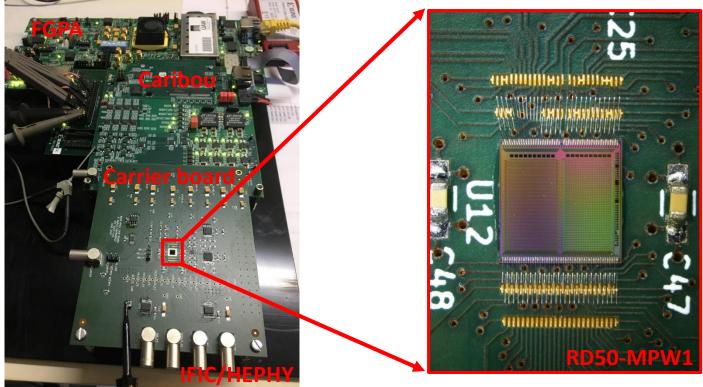

## RD50-MPW1 – DAQs

## 2 sets of DAQs

- 1 developed by IFAE (available from a previous design), for more details see presentation by S. Terzo in TWEPP 2018

- 1 developed by IFIC/HEPHY (developed within the CERN-RD50 collaboration, in progress)

- For more details about the IFIC/HEPHY DAQ, see presentation by R. Marco-Hernandez in 32nd RD50 WS

## **RD50-MPW1 – Measurements**

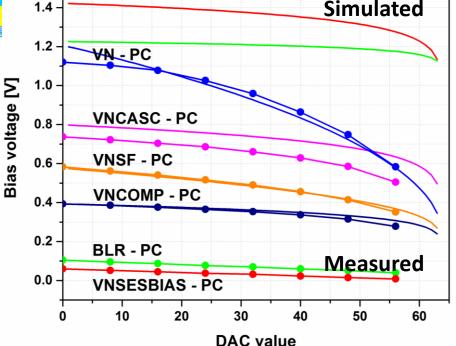

- Fairly good agreement between measured and simulated results

- Larger mismatch in those DACs that carry smaller currents (probe with 1M Ω input resistance takes current away and modifies the measurement)

- Measurements done with IFAE DAQ

- With IFAE DAQ, I<sub>LEAK</sub> of matrix is also large at very small voltages (I<sub>LEAK</sub> = 25 mA @ HV = 2 V)

#### <u>Aims</u>

- Replicate the breakdown voltage and leakage current measured with RD50-MPW1

- Understand what is causing the large leakage current

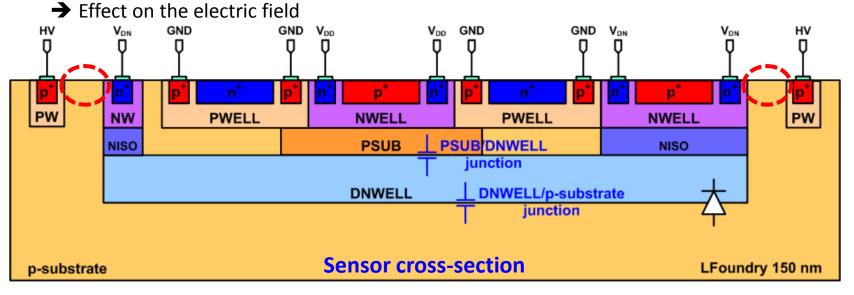

### We are doing TCAD simulations to

- Study the effect of increasing the spacing between PWELL (cathode @ HV) and NWELL (anode)

- → Simulation of a range of PWELL/NWELL spacings

- Study the effect of pixel corners (90 degrees, 45 degrees and rounded) on electric field strength

- Study the effect of chip guard ring configuration on breakdown voltage and leakage current

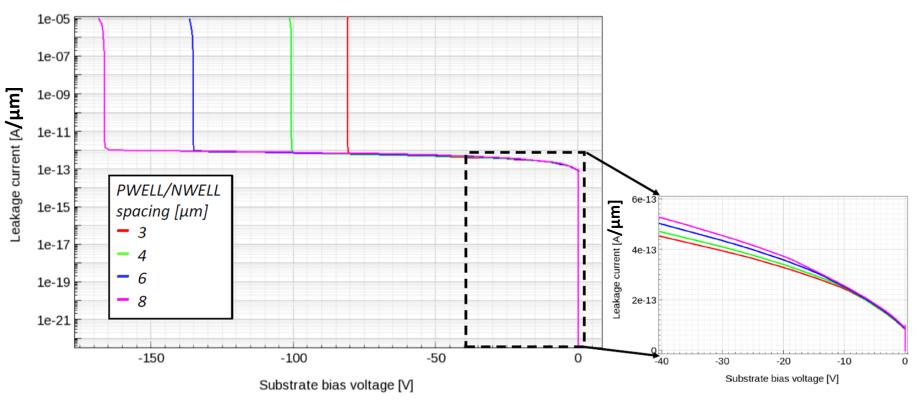

#### Simulation of a range of PWELL/NWELL spacings

- Increasing the spacing between the PWELL (cathode @ HV) and NWELL (anode @ V<sub>DN</sub>)

- ➔ Magnitude of electric field decreases

- ➔ Breakdown voltage increases as expected

- We also think there is some lateral diffusion

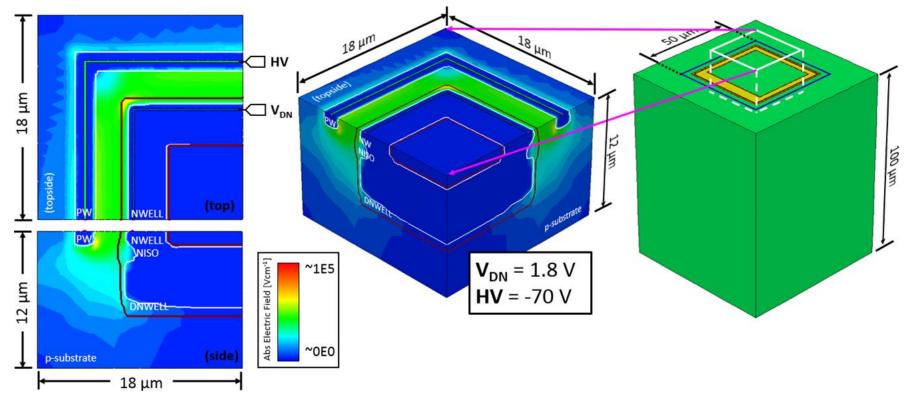

#### **3D simulation of electric field at pixel corners**

- Left: Top-down and front views of the electric field of a pixel with square corners

- <u>Right</u>: Simulation area (~ 1/4 of the pixel) chosen to minimize simulation time (> 1 week)

- Red lines are junction interfaces; white lines are depletion region limits

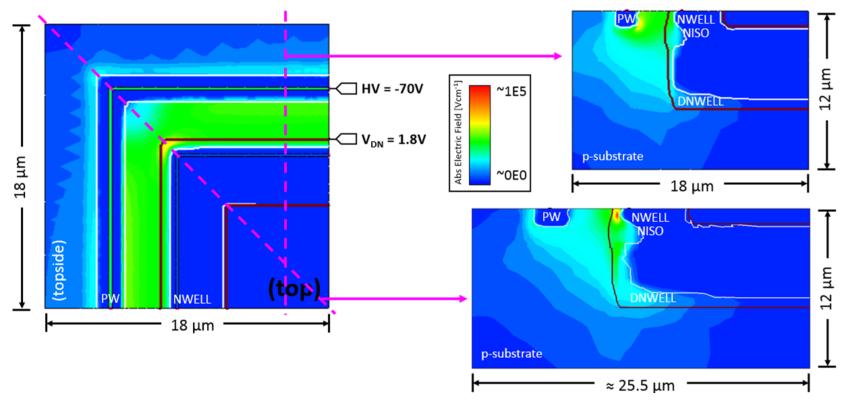

#### **3D simulation of electric field at pixel corners**

- Left: Top-down view of the electric field of a pixel with square corners

- → Pink dashed lines represent cut lines for front-views

- <u>Right</u>: Front-views of non-corner and square corner slices of the pixel

- → High electric field at square corners, which generates premature breakdown voltage

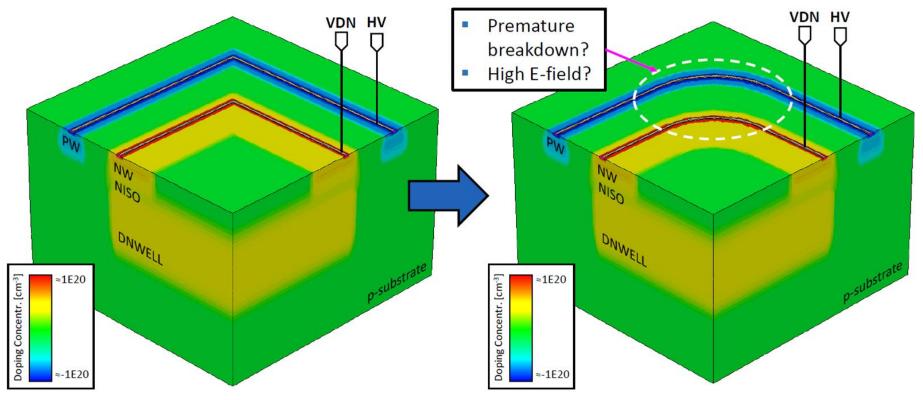

#### **3D simulation of electric field at pixel corners**

- Left: Pixel with square corners

- Right: Pixel with rounded corners

- → Running simulation of electric field of a pixel with rounded corners at the moment

- Colour of the simulations represents the doping concentration

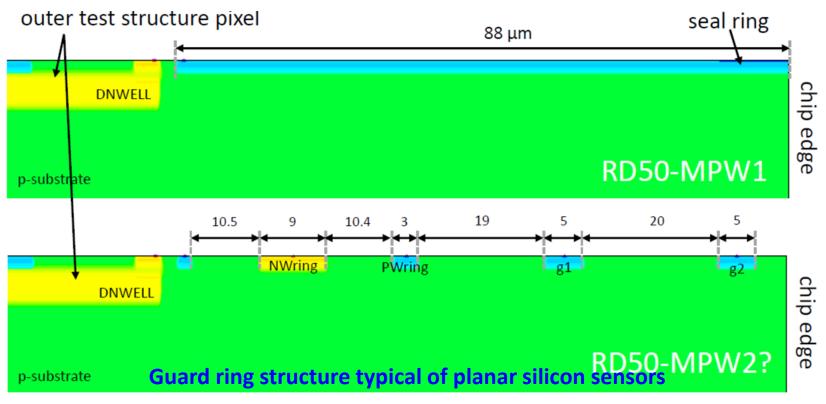

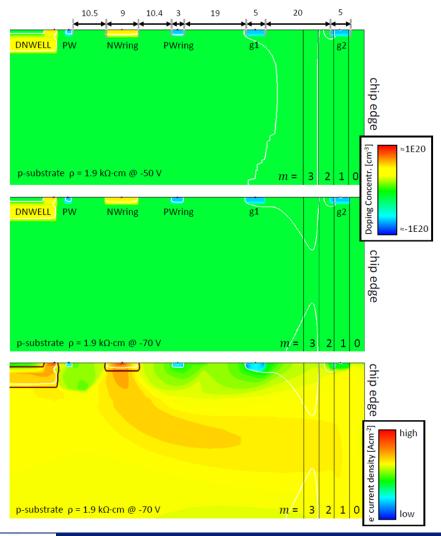

#### **Simulation of guard rings**

- <u>Top</u>: Chip edge of RD50-MPW1 contains a large bias ring

- Bottom: Chip edge of a future RD50-MPW2 with a possible improved guard ring

- → Guard rings typically stop the pixel depletion region from coming into contact with the chip edge

- Colour of the simulations represents the doping concentration

#### Simulation of guard rings with edge defects

- Edge defects introduced during dicing

- Noschis model (4 trapping levels): edge defects form a depletion region that can contribute to the leakage current

- <u>Top</u>: Simulation of guard rings with edge defects at -50 V

- → Pixel/edge depletion regions do not merge

- <u>Centre</u>: Simulation of guard rings with edge defects at -70 V

- → Pixel and edge depletion regions merge

- ➔ Pixel depletion region touches the edge of the chip and can increase the leakage current

- <u>Bottom</u>: Same simulation as in centre, but plotting the electron current density instead of the doping concentration

- NWring 'collects' leakage current when the pixel/edge depletion regions merge

250

#### **Comparison of TCAD simulated values with measured leakage current**

- In RD50-MPW1, we have:

- 1) Pixels with PWELL (cathode @ HV) and NWELL (anode @  $V_{\text{DN}})\,$  spacing of 3  $\mu m$

- 2) Pixels with 90 degrees corners

- 3) A large PWELL bias ring around the sensors instead of multiple NWELL and PWELL guard rings, as typically done in planar silicon sensors

- 1), 2) and 3) contribute to the leakage current, <u>but do not explain the large measured values</u>

- The foundry is aware of this situation. We are getting support from them.

- We suspect the biggest contribution to the large leakage current comes from <u>filling layers</u> added during the post-processing stage

- The filling layers generate conductive paths with a significant electron current density that contributes to the sensor leakage current. We are running TCAD simulations to fully understand this problem.

- The filling layers can be prevented at the design stage with blocking layers

#### Need to submit a test MPW

- We think it is too risky to submit the planned, large and expensive RD50-ENGRUN1 as our next step

- We think it is a lot safer to submit a small and cheap test MPW (RD50-MPW2) before submitting RD50-ENGRUN1

- TCAD simulations and chip design for RD50-MPW2 are quite advanced

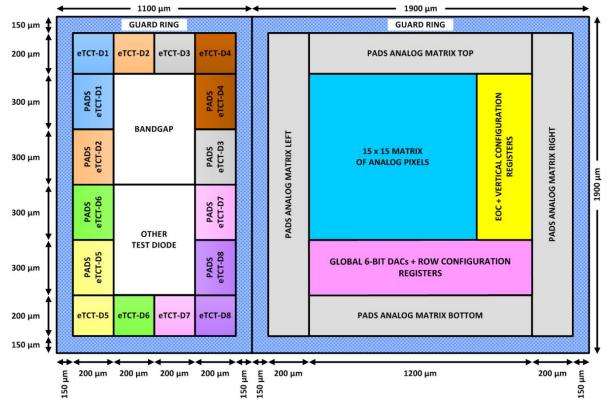

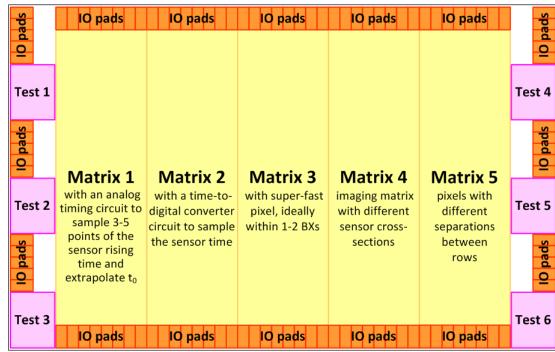

# RD50-MPW2 – Floorplan and pricing (1)

#### **Pricing condition:**

- a) MPW pricing condition

- Charged area: 6 mm<sup>2</sup> (minimum area)

F

0

S

- Price: 900 €/mm<sup>2</sup>

- b) Pricing for 2 customer specific substrates

- 1000 € (80 dies in total)

#### TOTAL PRICE for a) and b) is 6,400 € (before VAT)

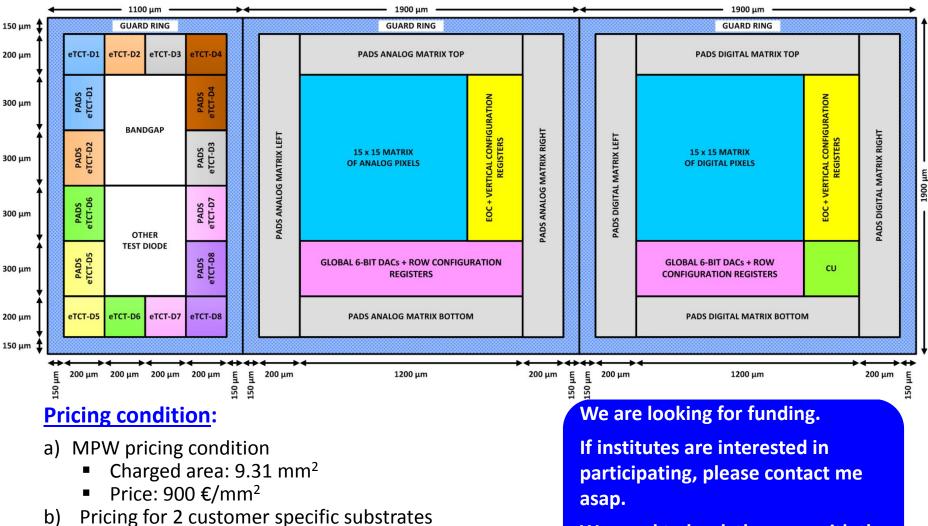

## RD50-MPW2 – Floorplan and pricing (2)

1000 € (80 dies in total)

#### TOTAL PRICE for a) and b) is 9,400 € (before VAT)

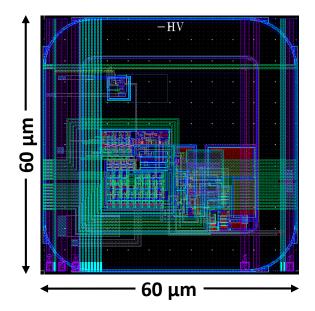

## **RD50-MPW2 – Design**

#### **MPW contents**

- 1) Tests structures for e-TCT

- 2) Matrix of depleted CMOS pixels with analog readout

- ➔ 15 x 15 pixels

- ightarrow 60  $\mu$ m x 60  $\mu$ m pixel area

- ➔ 2 different flavours of fast pixels

- 3) Matrix of depleted CMOS pixels with FE-I3 style readout

- ➔ Same as 2), but with digital readout

- Analog and digital readout embedded in the sensing area

- Completely independent matrices

- For more details about the pixels, see presentation by C.

Zhang in 32nd RD50 WS

## **Motivation**

Fabricate each step of the detector separately (sensors, analog readout and digital readout) to measure and study each part independently.

## **RD50-ENGRUN1**

#### <u>Aims</u>

- Improve the current time resolution of depleted CMOS sensors by a factor 10 with dedicated RO circuits

- Implement new sensor cross-sections

- Study pre-stitching options to increase the device area beyond the reticle size limitation

- Improve the current radiation tolerance with careful sensor design and backside processing

- All the work we are doing with RD50-MPW2 is a preparation for submitting RD50-ENGRUN1

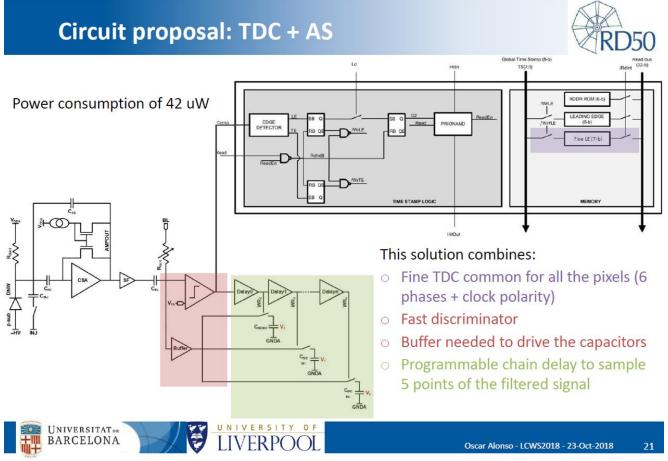

## **RD50-ENGRUN1 – Matrix 1**

- The design of the sampling pixel is quite advanced

- The design of a new control unit is also progressing well

- We can achieve timing resolutions of around 2 ns (simulated)

- For more details about the sampling matrix, see presentation by O. Alonso in LCWS2018

- We have started a project to develop depleted CMOS sensors within CERN-RD50

- We have designed and fabricated a first test MPW (RD50-MPW1):

- RD50-MPW1 is under test at the moment

- I-V measurements show a V<sub>BD</sub> around 55-60 V as expected from design, but I<sub>LEAK</sub> is too high

- We are doing TCAD simulations to understand this problem and study how we can improve the design of the sensor

- We stress the need to submit a small and cheap test MPW (RD50-MPW2) before submitting the planned, large and expensive RD50-ENGRUN1:

- Design and TCAD simulations for RD50-MPW2 are quite advanced

- RD50-MPW2 will contain passive diodes and 1 or 2 small matrices with analog or analog and digital readout electronics

- Before submitting RD50-MPW2, we need to find the funding to cover the prototyping costs

- The design of the large RD50-ENGRUN1 is running in parallel

## Thank you for your attention !