# **HERD** Collaboration meeting

# Fiber Tracker (FIT) Mechanics and Electronics Designs

Philipp Azzarello, Franck Cadoux, Yannick Favre, Daniel La Marra, Chiara Perrina, Junjing Wang, Xin Wu

Nov. 06-07 , 2018

HERD meeting (CERN)

- FIT Design overview (6 TRAYS design)

- Latest version of FEB

- FEA on TRAY assembly

- FIT weight status

### Franck Cadoux

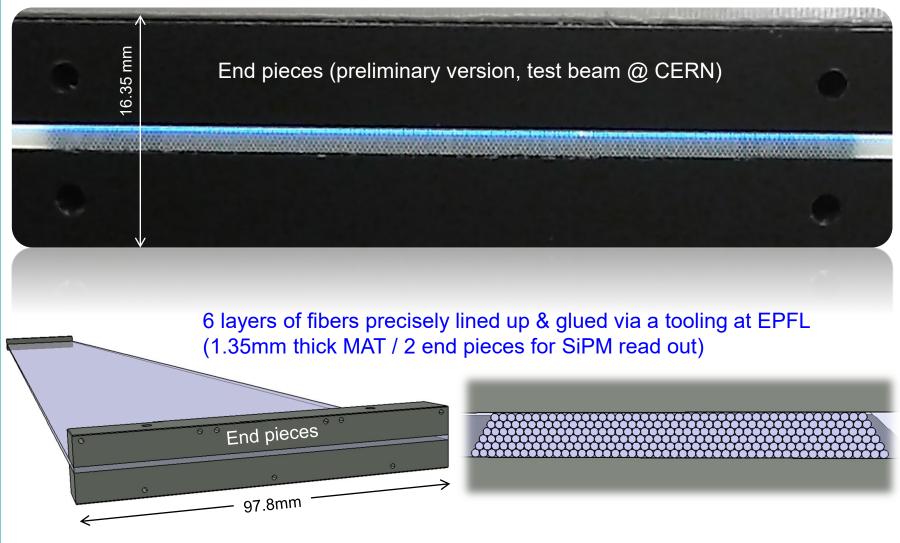

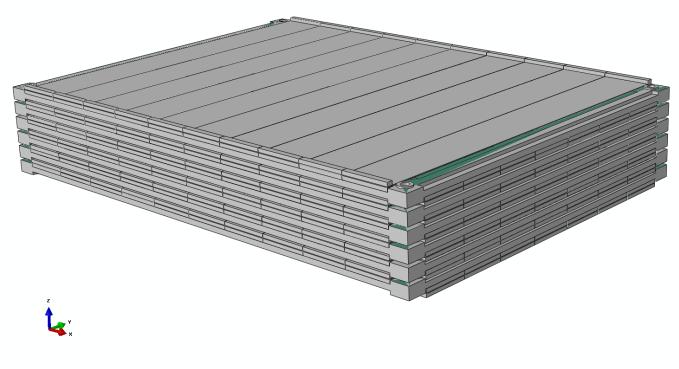

The Fiber MAT (stacking of 6 layers of 0.25mm diameter fibers)

Nov. 06-07 , 2018

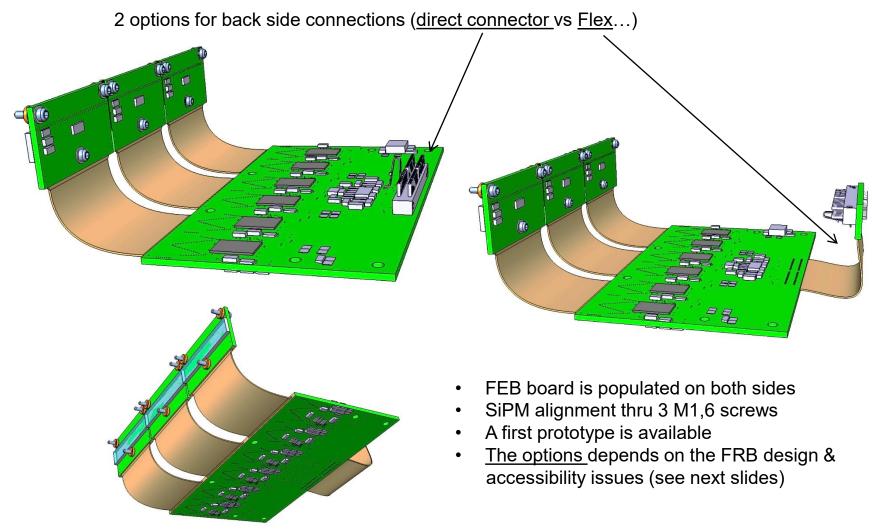

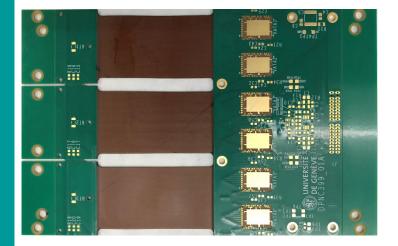

#### FEB Latest design (from the electronics designers @UNIGE)

Nov. 06-07 , 2018

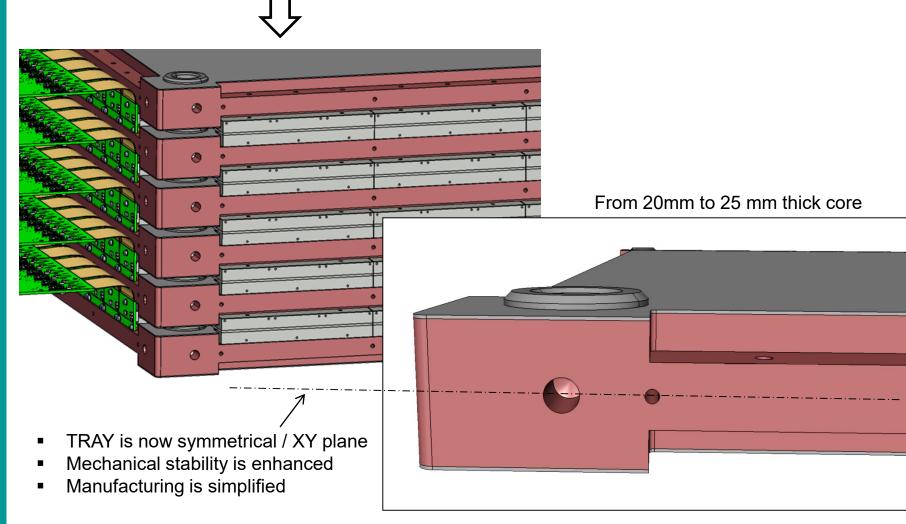

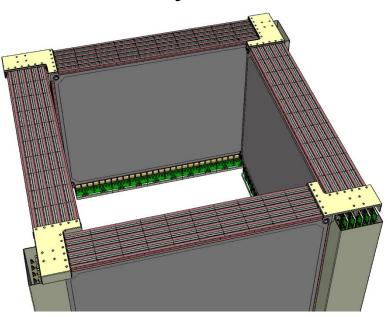

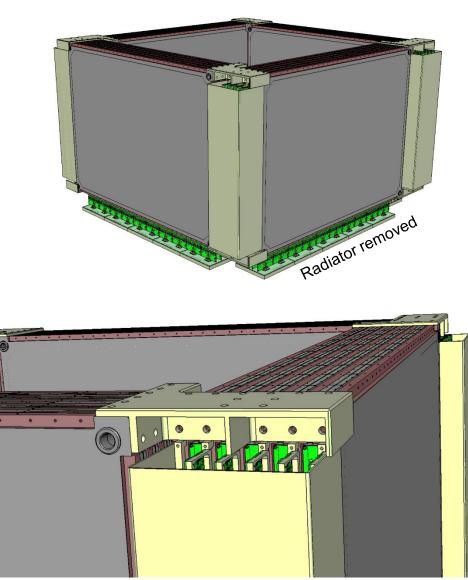

#### New Design: 6 TRAYS (5X / 5Y active planes... single READ OUT)

Nov. 06-07 , 2018

HERD meeting (CERN)

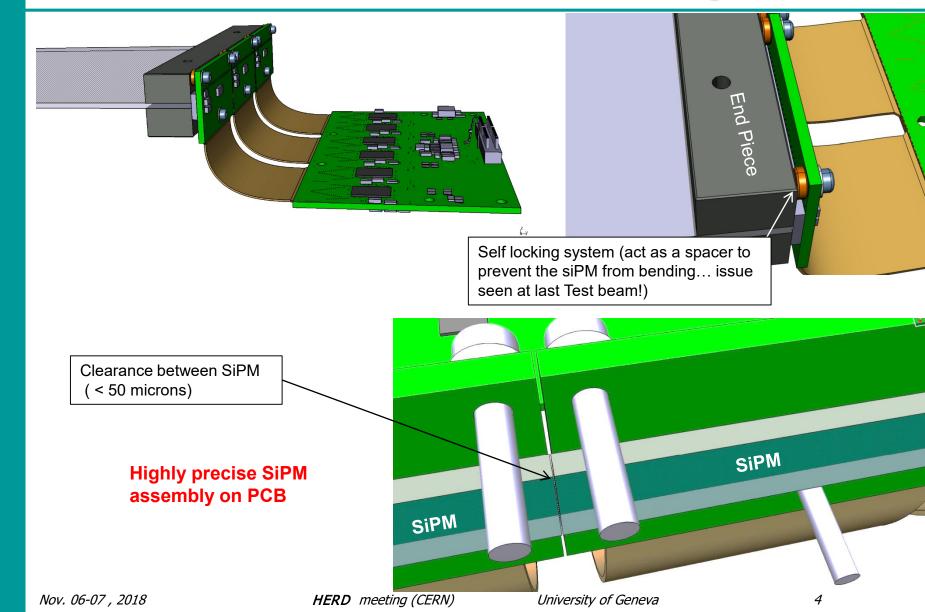

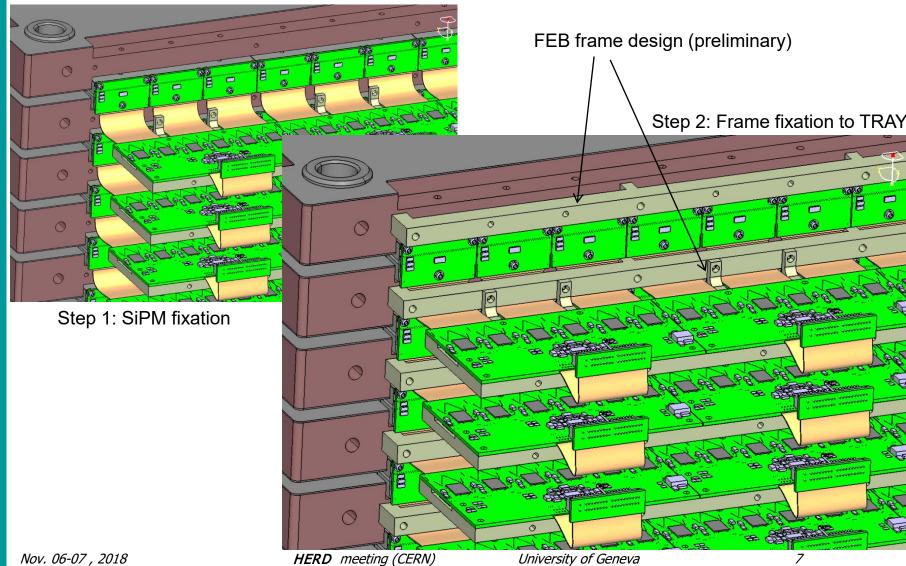

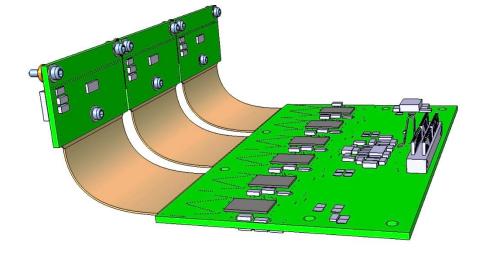

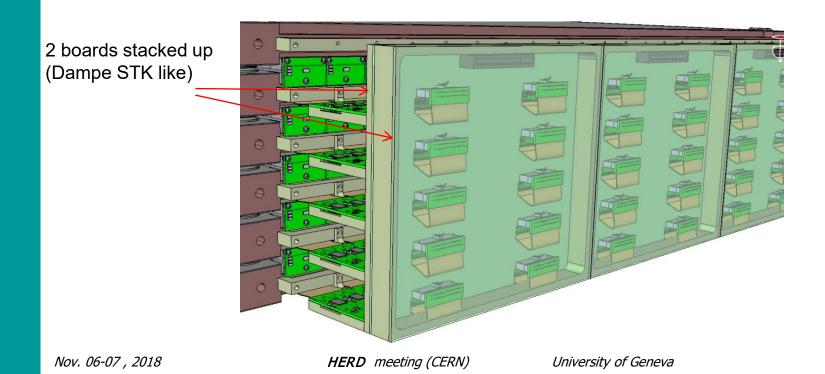

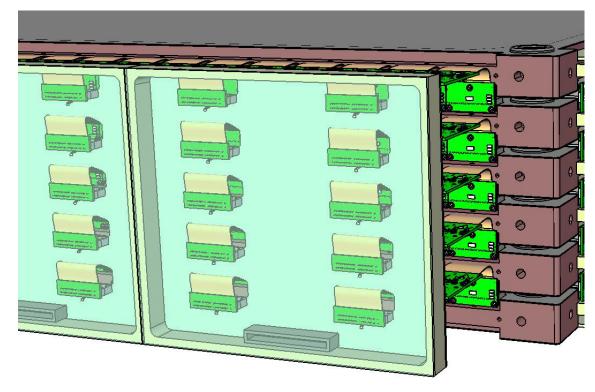

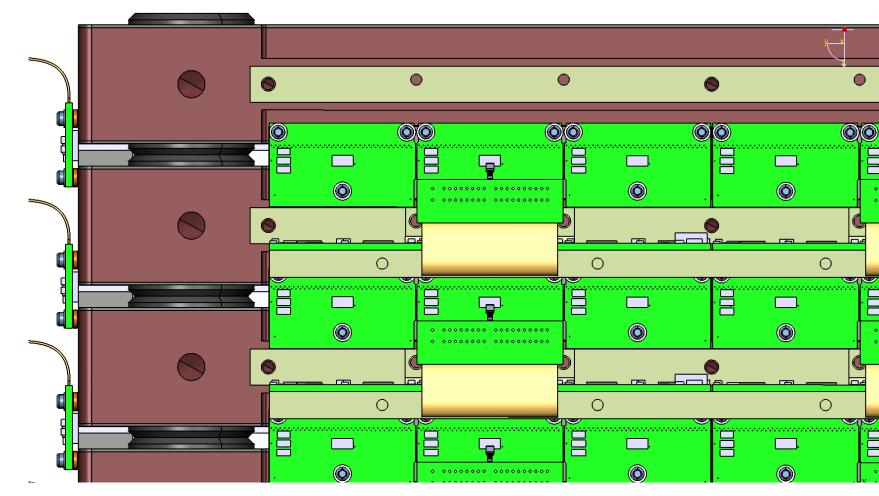

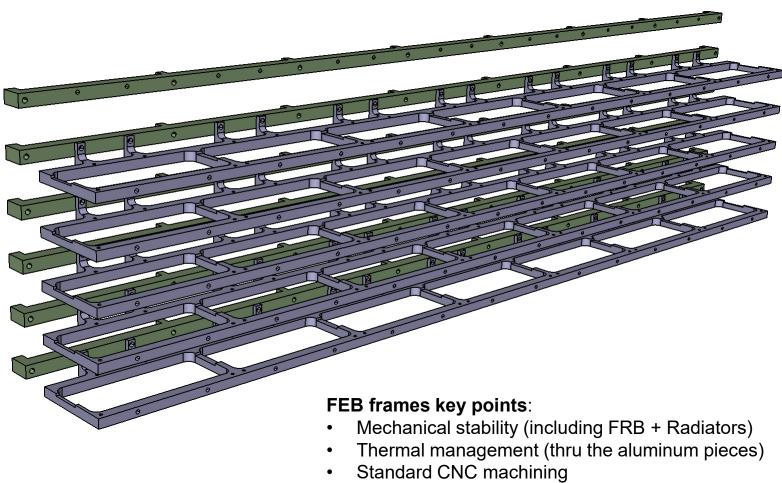

#### FEB Latest design (Mechanical assembly onto TRAYS)

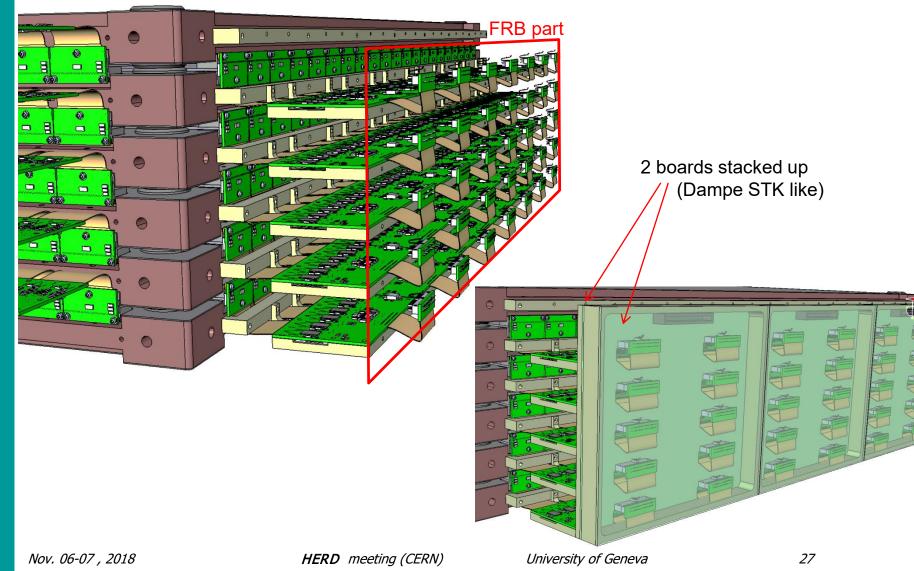

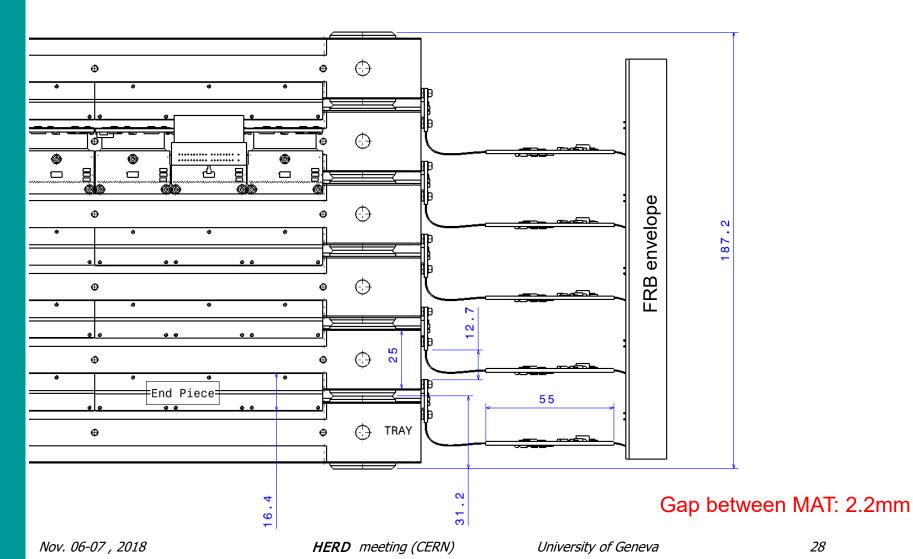

#### FRB very first design ...

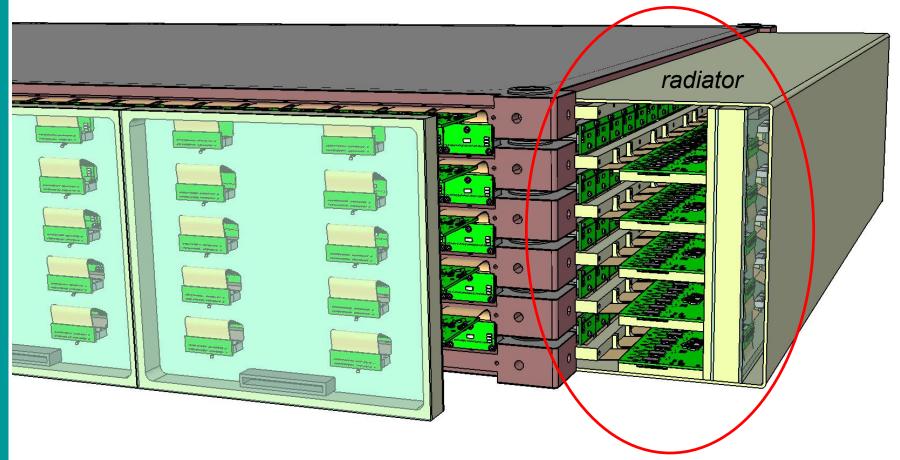

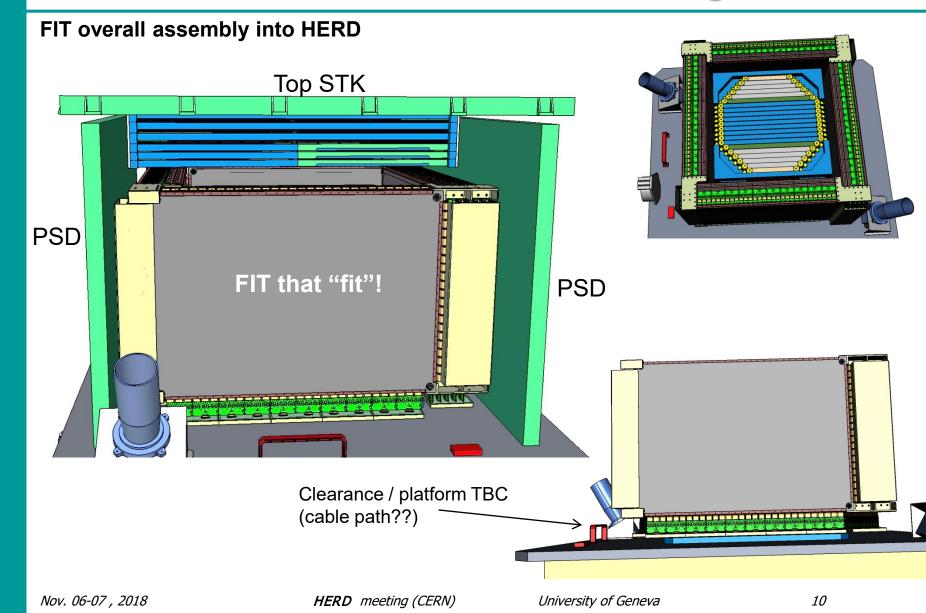

#### FIT overall assembly into HERD

## FIT Design overview

- Smaller corner feet (less material)

- Direct Interconnection between blocks

- Interfaces to HERD / Top STK

- May not need additional interface frame to STK (FEA to be done for validation)

Nov. 06-07 , 2018

HERD meeting (CERN)

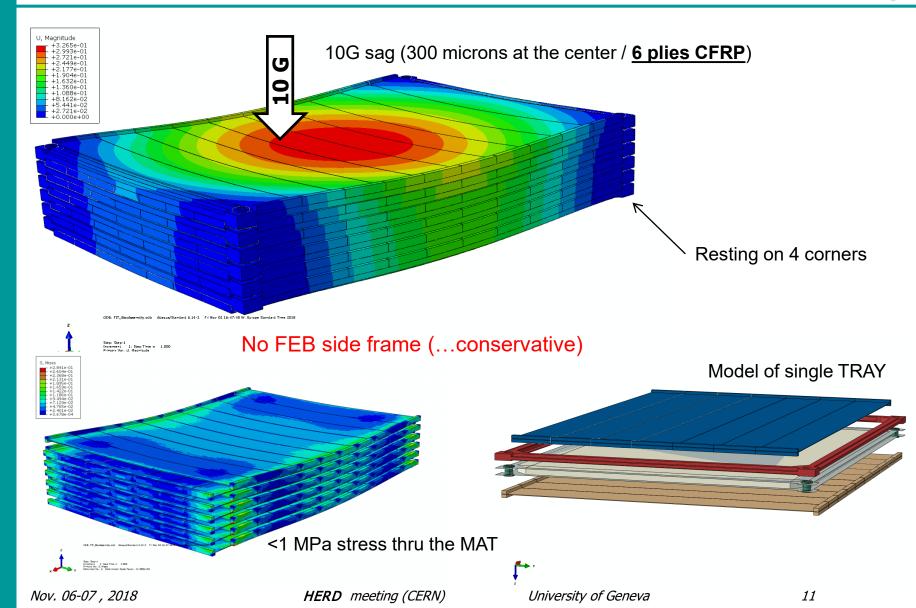

### FEA on TRAY assembly

### FIT TRAY Weight status

| Qty    | ITEM                     | Material (density)        | Weight (Kg)   |

|--------|--------------------------|---------------------------|---------------|

| 1 TRAY | Double Skins (6 plies)   | CFRP M55J (d=1.6)         | 1.48          |

|        | Double Skins (4 plies)   | CFRP M55J (d=1.6)         | 0.99          |

|        | Core 1 (20mm)            | AIREX foam (d=0.06)       | 0.85          |

|        | Core 3 (25mm)            | AIREX foam (d=0.06)       | 1.06          |

|        | Core 2 (16mm)            | AIREX foam (d=0.06)       | 0.68          |

|        | Frame (core 1)           | CFRP T300 (d=1.6)         | 1.83          |

|        | Frame (core 3)           | CFRP T300 (d=1.6)         | 2.41*         |

|        | Frame (core 2)           | CFRP T300 (d=1.6)         | 1.20          |

|        | Inserts                  | Aluminum 7075 (d=2.8)     | 0.06          |

| 7      | Fiber MAT X (long)       | Plastic and epoxy (d=1.2) | 1.47          |

| 10     | Fiber MAT Y (short)      | Plastic and epoxy (d=1.2) | 1.70          |

|        |                          |                           | 7.7 Kg / TRAY |

|        |                          |                           |               |

|        | 46.2 Kg max<br>+ FRB/FEB |                           |               |

|        |                          |                           |               |

- Front-end electronics board

- Front-end DAQ board

- Fit Readout Board (FRB)

### Yannick Favre, Daniel La Marra

Nov. 06-07 , 2018

HERD meeting (CERN)

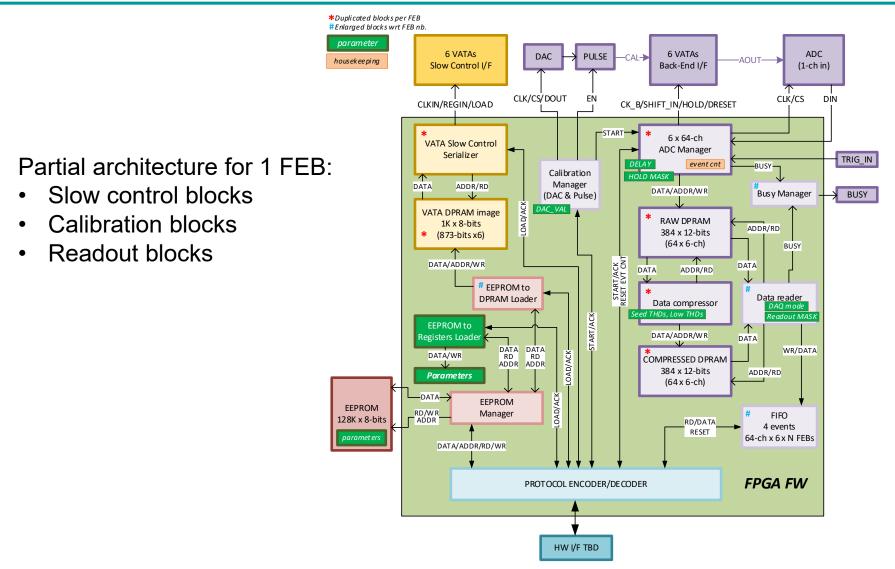

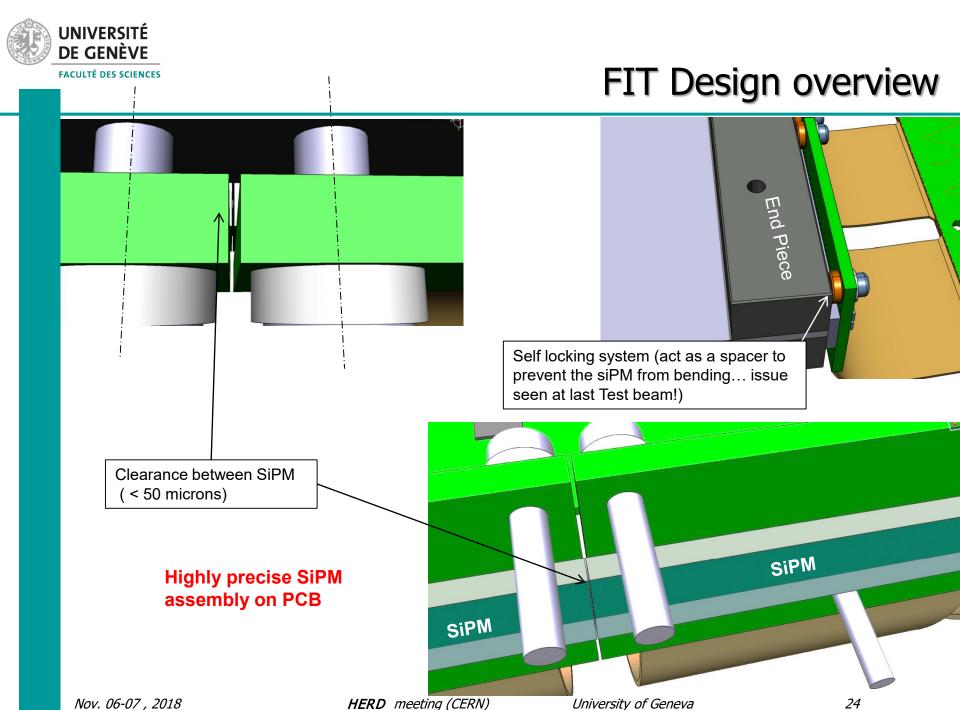

- Designed to read out three SiPM arrays.

- The present design uses six VATA ASICS.

- Another ASIC will be chosen for the flight model (next talk).

- The boards have been delivered, mounting of the first board will start in two weeks.

- A preliminary study will be done to define the precision of the SiPM positioning and alignment.

- Then, all the components will be mounted on the board.

Nov. 06-07 , 2018

- The DAQ board is compatible with the old FEB design (2-VATA board).

- Firmware to readout the 2-VATA board is ready.

- The new DAQ boards will be used for the first time at the DAMPE beam test next week.

- The firmware will then be adapted for the FEB with 6 VATAs.

- Four DAQ boards have been assembled.

Nov. 06-07 , 2018

HERD meeting (CERN)

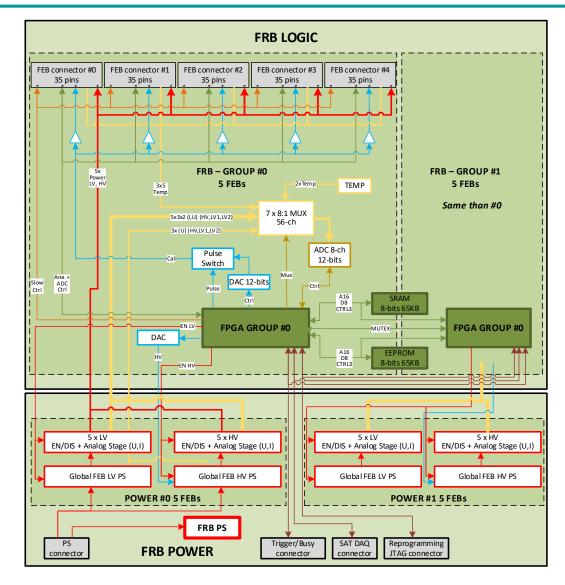

- Dimension of a single board: 198 x 200 mm

- In the present design the FRB shall read out 10 FEBs.

- The FRB circuit will actually be composed of a stack of boards:

- One hosting the FPGAs for DAQ control and communication.

- One hosting the power supply.

- This is a similar approach to the one chosen for the STK of DAMPE.

### The FIT Readout Board (FRB)

The TRB specifications are being written. Two versions are documented:

- The Engineering Model (EM) will read out max. 4 FEBs (with VATA ASIC).

- The Flight Model (FM), will read out 10 FEBs, with the final ASIC.

- One FIT side tracker will have 9 FRBs, reading out 85 FEBs.

- The total FIT tracker will have 36 FRBs, reading out 340 FEBs.

Nov. 06-07 , 2018

### FPGA firmware architecture (1)

Nov. 06-07 , 2018

HERD meeting (CERN)

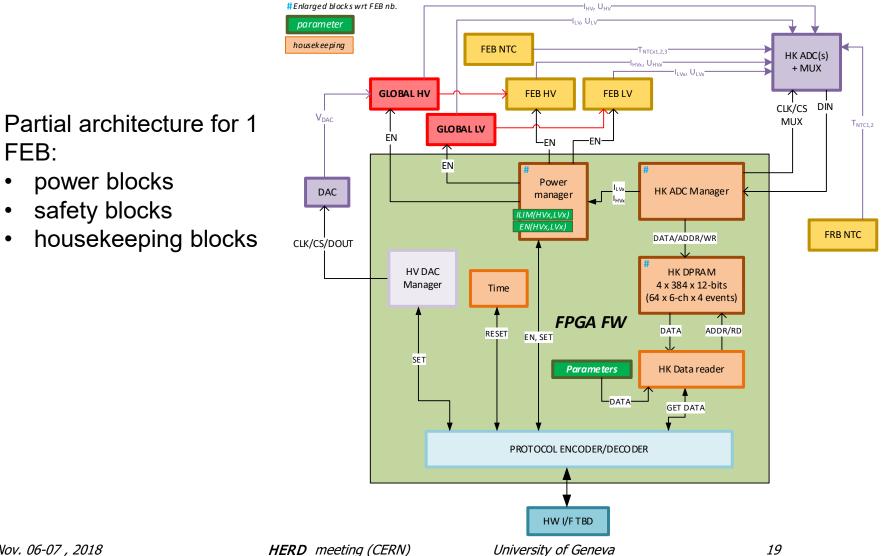

### FPGA firmware architecture (2)

Nov. 06-07, 2018

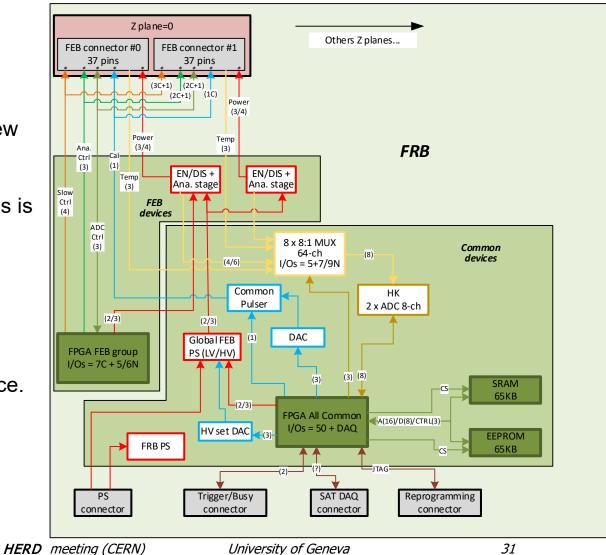

### FRB architecture overview

Nov. 06-07 , 2018

HERD meeting (CERN)

- Microsemi FPGAs are a natural choice for space application.

- The RT ProASIC3 FPGAs are reprogrammable, nonvolatile and rad-hard flash-based FPGA. Triple-chip redundancy is not required.

- For prototyping, the RT3PE3000L (600L) uses the same silicon than A3PE1000L (600L) so migration is very easy. The space packages available are CQFP, CGA or LGA.

- As the FPGA is reprogrammable, it would be good to keep the possibility to reprogram the FPGA during the mission.

- This means having JTAG lines connected to main DAQ computer.

To go further with the development of the FIT, there are some open questions, listed here:

- Is there a documentation about the qualification levels / qualification test specifications for the subdetectors of HERD (vibration, shock, thermal, thermal vacuum, EMC/EMI) ?

- What are Radiation hardness and SEU specifications for the electronics of HERD ?

- What are the thermal constraints ? (e.g. radiator temperature)

- What is the foreseen communication protocol between the subdetector DAQ systems and the HERD DAQ ?

- We are considering working with a re-programmable FPGA, in a way that possibly the code can evolve during the mission. For this, we would need the main DAQ computer to have the ability to do the reprogramming, having the JTAG lines connected to the main computer. Is this approach feasible ?

Nov. 06-07 , 2018

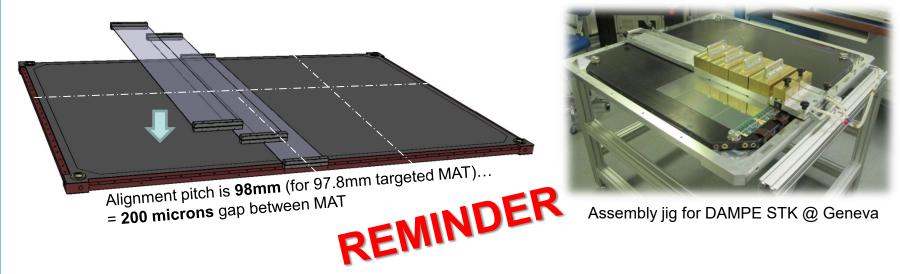

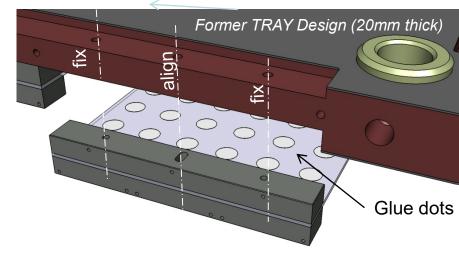

#### Fiber MAT "loading" process (as compared to DAMPE STK's)

#### Advantages (comparing to STK loading)

- No need of dedicated long jigs (ref. on TRAY)

- Fiber MAT not fragile... easy handling

- 2 levels of fiber MAT fixation (screw + glue)

- No corrosion issues (easy storage)

- SiPM can be fixed later on TRAYS

#### Leading to time saving for TRAY loading

Nov. 06-07 , 2018

#### FEB Latest design (Mechanical assembly onto TRAYS)

Every screw accessible from "outside"... by playing with flexes!

Nov. 06-07 , 2018

HERD meeting (CERN)

#### FRB very first design ...

#### New Design: 6 TRAYS (overall size)

## Preliminary FEA (simulations) From single TRAY to full assembly

Two FPGAs will be required. There are two possible approaches on the FPGA task division:

- Per FEB: i.e. having 5 FEB per FPGA and the same firmware for both of them:

- Drawback: The SRAM & EEPROM memories should be duplicated, 1 for each of the FPGA (assuming we need external SRAM memory).

- Advantage : safer approach, we should be able to handle all the SiPM channels with 2 FPGAs (1920 channels per FPGA, memory and registers resources divided by 2)

### • Per functional block:

1st FPGA: SiPM ADC channels handling

2<sup>nd</sup> FPGA: HK, PS enable, counting, synchronization, calibration

- Drawback: To be sure to handle all 3840 SiPM channels in 1 single FPGA. 2 different firmware required.

- Advantage: To be able to handle more advance control for HK & eventual HV compensation

The "per FEB" task division has been chosen.

### FPGA partial functional architecture

\* = con nector redundancy, nb of pins x2 C = com mon x/y = x PS for SIPHRA / y for VATA

- Preliminary functional view of the FPAG I/Os

- Only one group of 2 FEBs is shown, for the 4 others FEBs groups, the 'FEB devices' block should be duplicated.

- The 'Common devices' block is required only once.

Nov. 06-07 , 2018

#### FEB Latest design (Mechanical assembly onto TRAYS)

- Ease the mounting / dismounting (maintenance on SiPM)

- Interface to the FRB (see next slide)

Nov. 06-07 , 2018

#### Wrap up & Discussions

| Simu Type                    | 6 plies M55J<br>/ 20mm core | 4 plies M55J/<br>20mm core | 6 plies M55J/<br>16mm core | 4 plies /<br>16mm core  | 6 plies M55J /<br>25mm core |  |

|------------------------------|-----------------------------|----------------------------|----------------------------|-------------------------|-----------------------------|--|

|                              | SINGLE TRAY                 |                            |                            |                         |                             |  |

| Acc. 10G<br>(Def)            | 0.47mm                      | 0.51mm                     | 0.68mm                     | 0.73mm                  |                             |  |

| Frequencies<br>(First modes) | 91Hz / 157Hz /<br>170Hz     | 88Hz / 149Hz /<br>170Hz    | 75Hz / 132Hz /<br>142Hz    | 72Hz / 126Hz /<br>142Hz |                             |  |

|                              |                             |                            |                            |                         |                             |  |

| Acc. 10 G<br>(Def)           |                             |                            |                            |                         | 0.32mm                      |  |

|                              |                             |                            |                            |                         |                             |  |

#### In theory

following the single TRAY FEA, "4 plies + 25mm core" will lead to a deflection < 0.4mm