### **SAMPA frontend for SRS**

A Short Overview of SAMPA chip

Specification & Functionalities

Planning for a SAMPA frontend in the SRS ecosystem

Marco Bregant IFUSP – São Paulo

RD51 miniweek, 6<sup>th</sup> December, 2018

### The SAMPA ASIC, where it came from

During Run3 ALICE needs to operate at higher rate, recording all MB events Goal: 50kHz in Pb-Pb (~10nb<sup>-1</sup> in Run3 and Run4)

Upgrade detectors and electronics during Long Shutdown 2 ("now"-2020)

- ➤ Time Projection Chamber (TPC)

- GEM readout plane, high rate capability, continuous readout.

TPC electronics used till "past week" was not made to amplify negative charge input (as GEMs provides) and cannot cope with the higher rate and with the continuous readout operation planned

- ➤ Muon Chamber (Forward muon spectrometer)

- Higher rate capability, new acquisition electronics chain in ALICE new electronics needed, too

TPC required a new readout, MCH too.

A common project to design a new ASIC: <u>SAMPA</u>

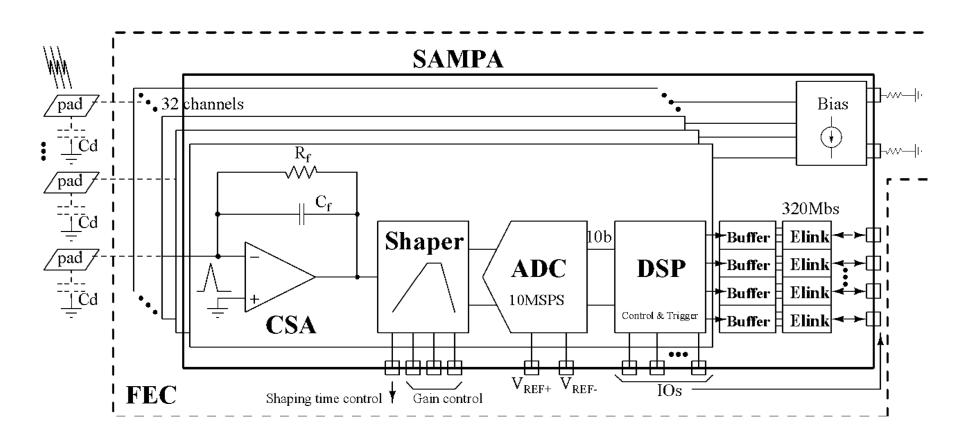

### **SAMPA Design Specifications Summary**

- TSMC CMOS 130 nm, 1.25V technology

- 32 channels, Front-end + ADC + DSP

- package size ≤15x15mm² (total footprint)

- ADC: 10-bit resolution, 10MS/s, ENOB>9.2 (Alice TPC is eventually using: 5MS/s, to keep BW requirement in the readout chain lower)

- DSP functions: pedestal removal, baseline shift corrections, zero-suppression

- Data transmission: up to 11 e-link at 320 Mbps to GBTx, SLVS I/O

- Power < 32 mW/channel (Front End + ADC)</li>

| TPC Mode                                                                                                                                                                                                                                           | MCH Mode                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Negative Input charge</li> <li>Sensor capacitance: 12 – 25 pF</li> <li>Sensitivity: 20mV/fC &amp; 30mV/fC</li> <li>Noise: ENC ≤ 580 e<sup>-</sup> @ 18.5pF</li> <li>Peaking time: ~160 ns</li> <li>Baseline return: &lt;500 ns</li> </ul> | <ul> <li>Positive input charge</li> <li>Sensor capacitance: 40–80 pF</li> <li>Sensitivity: 4mV/fC</li> <li>Noise: ENC ≤ 950 e- @ 40pF         <ul> <li>1600 e- @80pF</li> </ul> </li> <li>Peaking time: ~300 ns</li> <li>Baseline return: &lt;550 ns</li> </ul> |

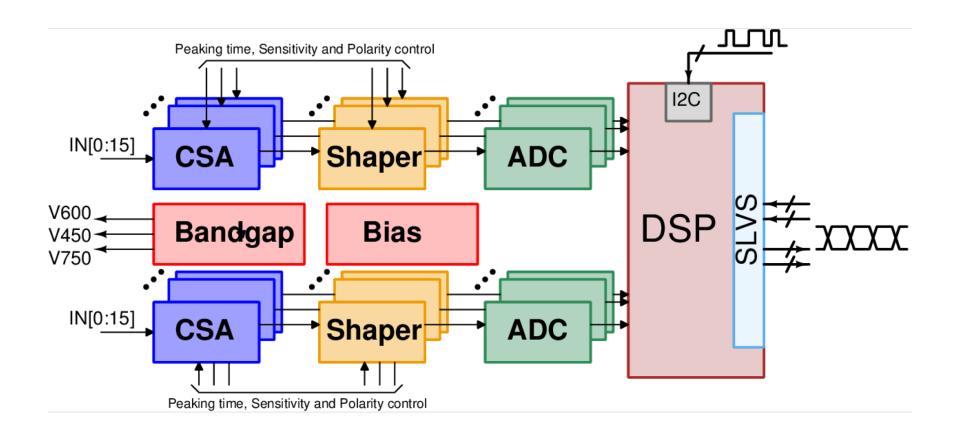

### **SAMPA Block Diagram**

### **SAMPA Block Diagram**

Functionalities overview

### **Top Level Functionality**

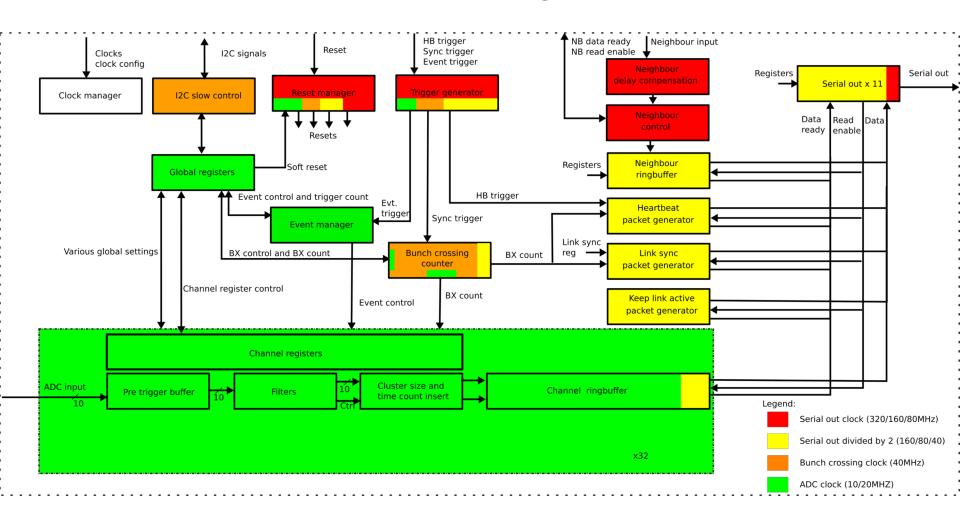

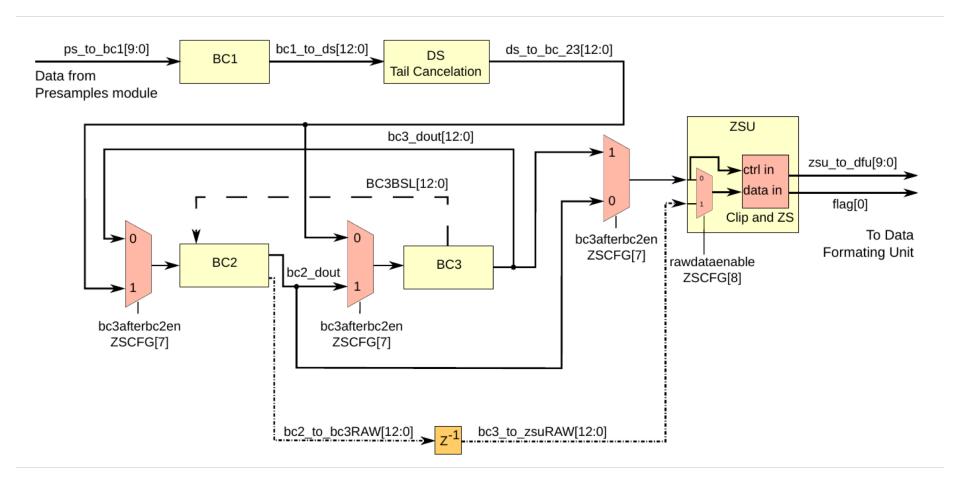

### 4 primary filter blocks

- -Individual correction per channel

- –Baseline correction

- 1 FIR filter

- 1 Slope based filter

- 1 IIR filter

- Lookup table correction(Pedestal Memory) f(t);f(din)

- Conversion f(din)

- Fixed correction

- -Tail cancellation

- •1 IIR filter

### **SAMPA Digital Block Diagram**

#### SAMPA block diagram

### **SAMPA Digital Filters Block Diagram**

### **Top Level Functionality**

### Compression

- Zero suppression with run length encoding

- Forward linked list for easier decoding

- -Cluster sum

- Uses zero suppression with run length encoding, but sums cluster into 20bit word

- -Huffman

- Differential encoded data

- Programmable table of codes for +17 to -17

- Values outside table have special Huffman code prepended to raw 10bit value

### **Top Level Functionality**

### Configuration

- -Configurable through I2C

- -1 global register unit, 32 sets of channel registers

### Design for test

- –JTAG boundary scan

- —Built in memory tester

- –Scan chain (on >98% of digital block flops)

#### Radiation tolerant

- -TMR on almost all flip-flops

- except on part of data path

- —Hamming protected headers

### Readout

- Selectable number of serial links up to 11

- -320/160/80Mbps

- -Channels divided among links, no load sharing

- Which channel goes to which link and in which order can be selected

- —Data is packet based (header + payload)

- One packet per channel per event

#### Event modes

- —Triggered

- -Continuous

- -Selectable event length up to 1024 samples

- -192 pre-trigger samples

### Readout

### Event buffer per channel

- -6144(6K) words of compressed samples

- -256 words of headers

- -Header still created if data memory goes full

### Daisy chain

- -Multiple devices can share a single serial link to readout unit

- -2K word buffer in the receiving side

### Readout

#### Direct ADC serialization

- —Data serialized directly from ADC at 32xADC speed over 10 links

- —Raw data, no filtering, no headers

- —Sync pattern on startup, receiver should maintain sync after that

- -2 modes

- •10 bits is sent consecutively for channel 0-31 each 32xADC cycle

- •5 lower bits, then 5 higher bits consecutively for channel 0-15 is sent on link 0-4 and for channel 16-31 on link 5-9

- —Clockgate the rest of the system to save power

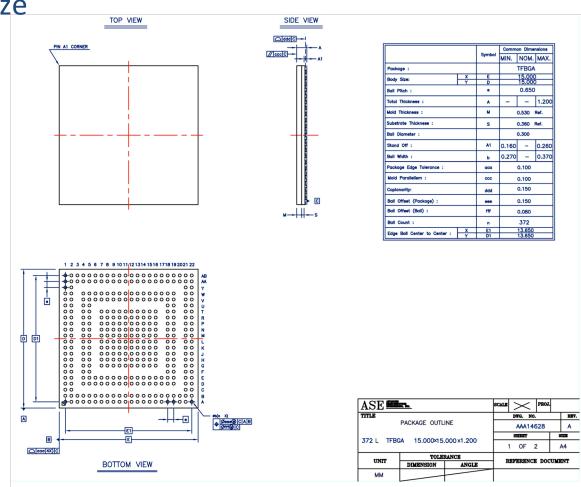

### **SAMPA Package**

TFBGA package

15 mm x 15 mm body size

- 1.2 mm thickness

- 0.65 mm ball pitch.

- 372 balls

- 4-substrate layers

Performance

# Some results from SAMPA qualification

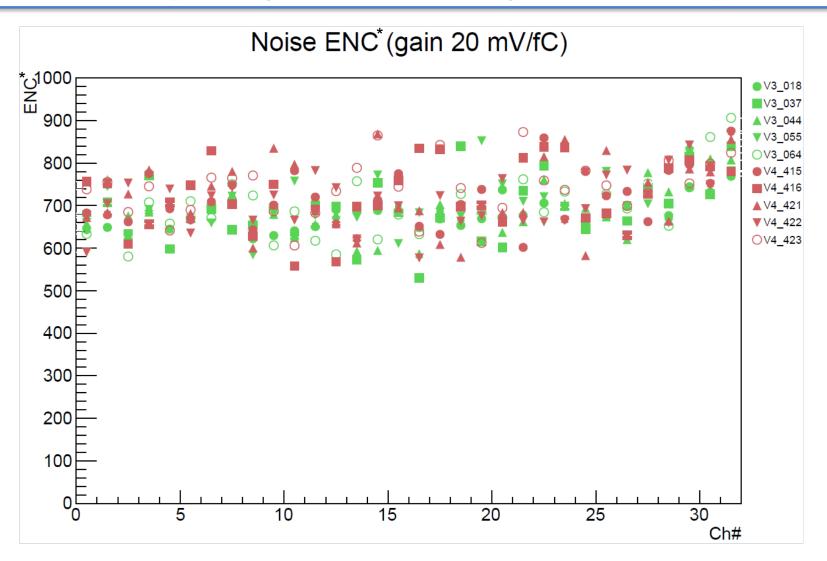

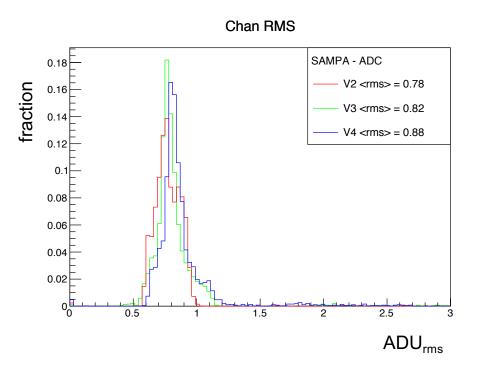

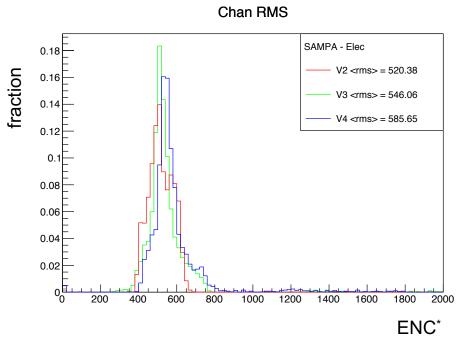

### Noise

### **Noise**

### (example of inside chip distribution)

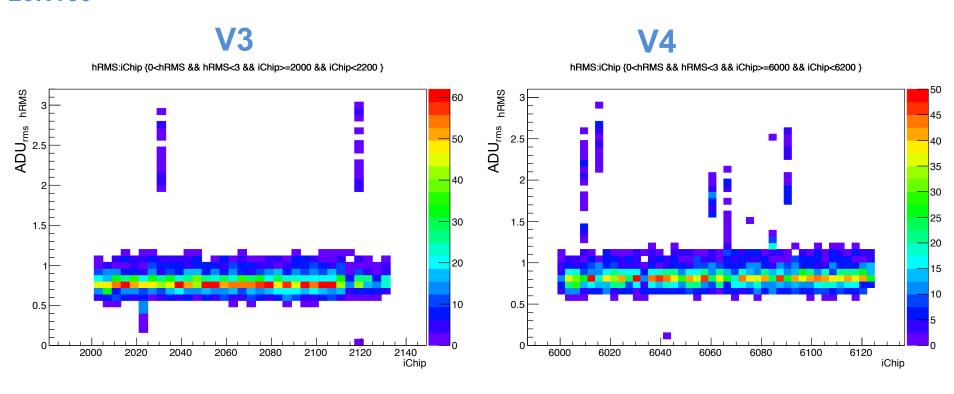

### Noise (many chips)

#### Experimental conditions:

C<sub>det</sub>=0 (no added capacitance on the CSA input) R<sub>s</sub>=0 (external ESD-protection series resistor not present)

#### 20N160

\*) ENC calculated using nominal FE gain (20mV/fC) and nominal ADC conversion factor (2.15 mV/ADU)

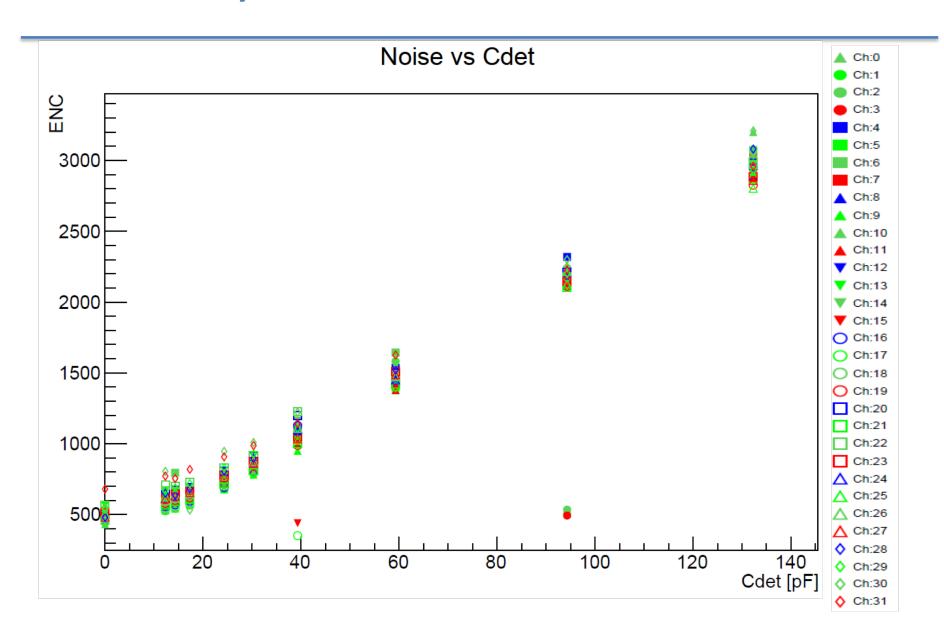

### Noise (many chips)

#### 20N160

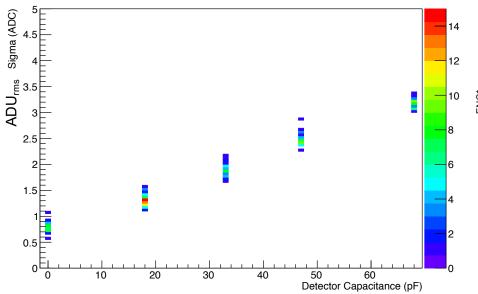

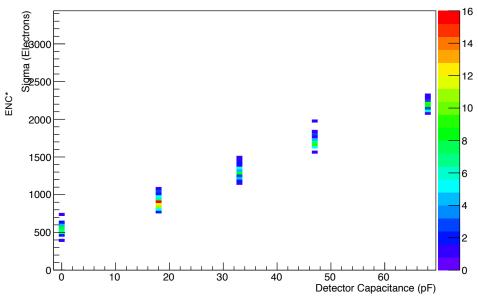

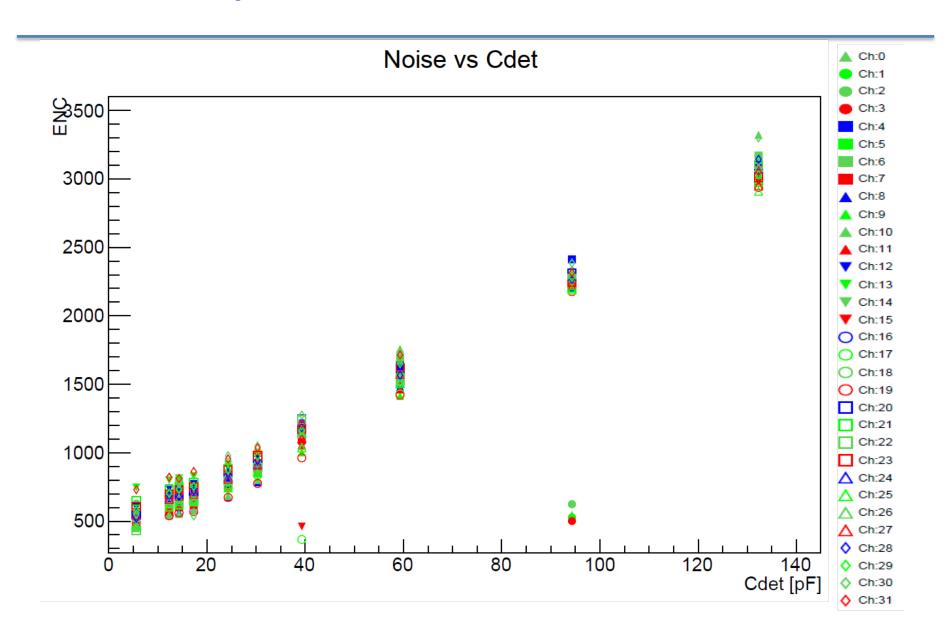

### Noise vs $C_{det}$ (v3, 20N160)

#### Experimental conditions:

$C_{det}$  scan  $R_s$ =100 $\Omega$

#### 20N160, chip V3 #2128

#### Noise (Electrons) vs Cap: 2128\_100ohm\_20mV\_10mhz

<sup>\*)</sup> ENC calculated using nominal FE gain (20mV/fC) and nominal ADC conversion factor (2.15 mV/ADU)

### Sensitivity (gain)

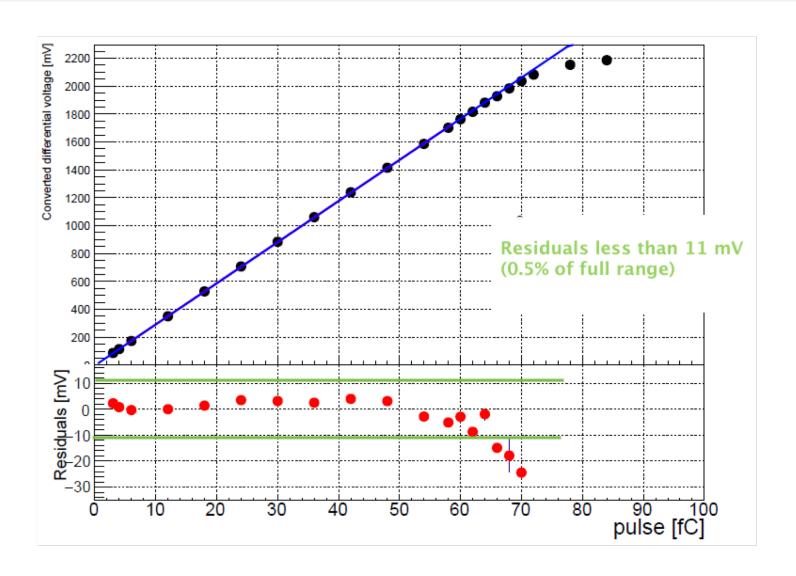

### Linearity and Residual – an example

30N160

### Linearity range, overview

- A calibration curve was performed for all channels of several chips

- The residuals\* are very small (<10mV), for all channels, for a consistent part of the operational range:

- 20N160: until ~95 fC  $\Leftrightarrow$  1900 mV (>85% of the full range)

- 30N160: until ~63 fC  $\Leftrightarrow$  1900 mV (>85% of the full range)

- 4P300: until ~480 fC  $\Leftrightarrow$  1900mV (>85% of the full range)

<sup>\*</sup> The curve used to calculate the residuals is the result of a linear fit in the central range (~15%-75%)

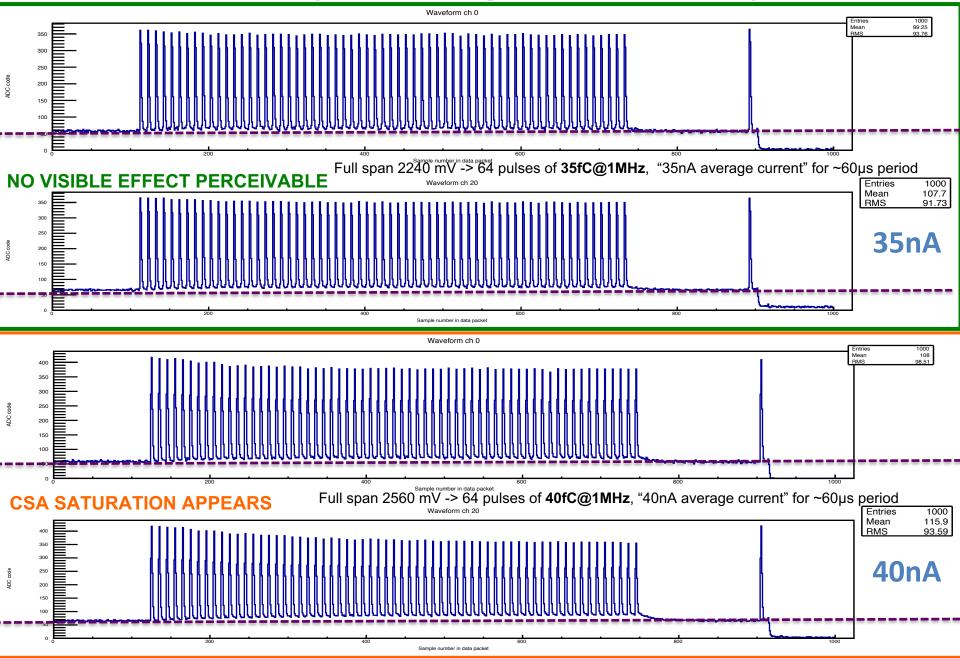

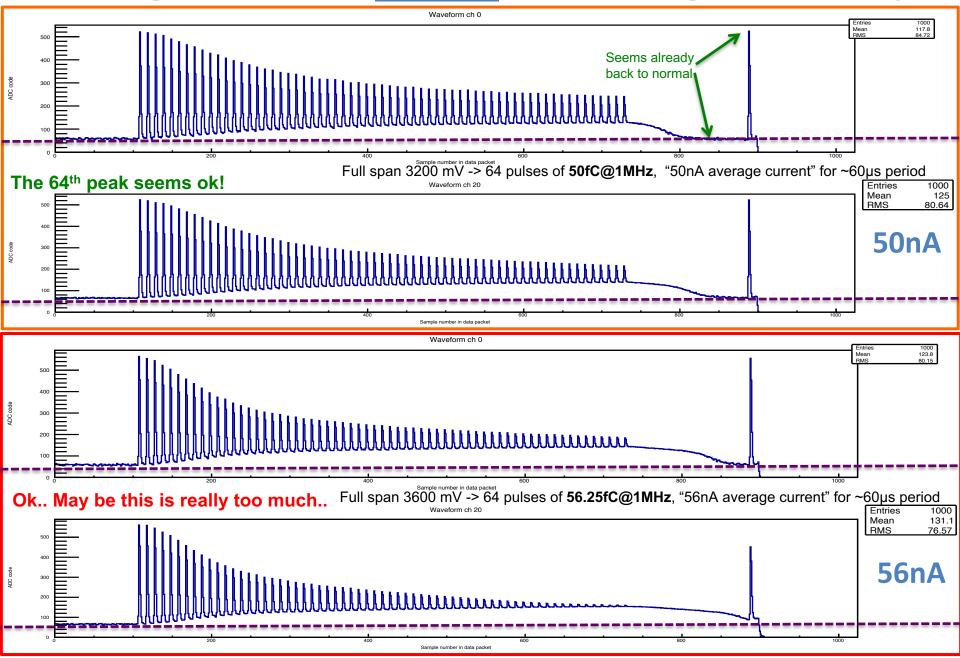

## CSA robustness against Pile Up in SAMPA V4

### Pile-up testing of a V4 chip

### Going on: now really stressing a V4 chip

### SAMPA chip overview summary

- SAMPA design was ALICE TPC/MCH driven, nevertheless design quite general:

- ASIC for gas detector readout (either "GEM-like", electron collection) or "MWPC-like" (induced charge collection)

- 4/20/30 mV/fC gain (500/100/66 fC range) provided

- Digitalization @10MS/s [improved version @20MS/s under study]

- Several readout options available by the embedded DSP:

- "raw data" (DSP-bypassed, no trigger, continuous read-out)

- Continuous or triggered readout, framed data (DSP)

- Filters available for baseline correction

- Either ZeroSuppression or Huffman coding for data reduction

- Possibility of Cluster\_sum output and DaisyChain

- I/O via I2C (settings) and up to eleven 320Mbps LVDS links

### Why SAMPA frontend for SRS

- SAMPA design was ALICE TPC/MCH driven, nevertheless design quite general:

- Several readout options available by the embedded DSP:

- I/O via I2C (settings) and up to eleven 320Mbps LVDS links

SAMPA ASIC is working and available.

It was designed for gaseous (GEM / MWPC) detector readout

Likely of interest also outside ALICE/LHC community

We feel that it does make sense to integrate it on SRS

Our group directly interested in having such a system working to be used in local activities

### Our Planning for a SRS frontend

- SAMPA designed locally, good knowledge, quick and full access to the original designers (important here, the digital ones)

- Two mains challenges

- 1. Firmware for the FPGA linking SAMPA to SRS backend

- 2. Design of high density, multilayer, low crosstalk (analog & analog-digital), etc., board to host 4 SAMPAs (to provide 128chs hybrid)

- First steps

- Study both in simulations and with an assembly "SAMPA\_testboard" <-> "FPGA developing board" the coupling and the comunication btw SAMPA and target FPGA (w/o hybrid)

- Start already design of hybrid board

FPGA firmware engineer already contracted;

Board design specialist candidate being evaluated right now.

# QUESTIONS? COMMENTS? SUGGESTIONS?

More informations

### **BackUp Slides**

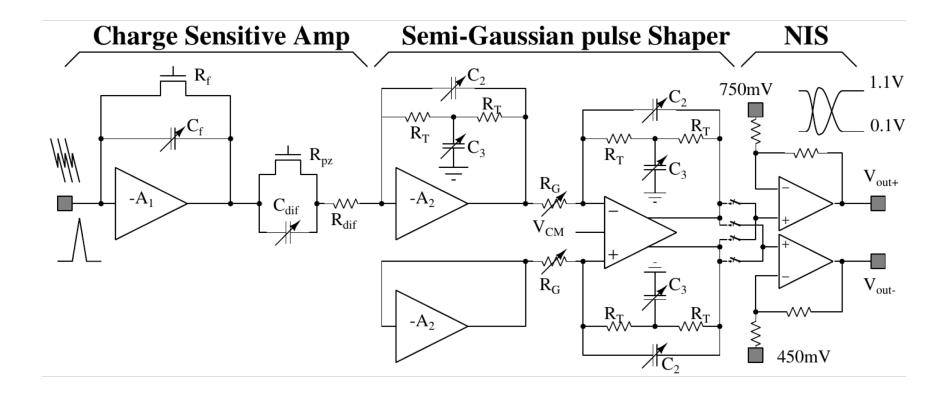

### SAMPA V3: CSA + Shaper

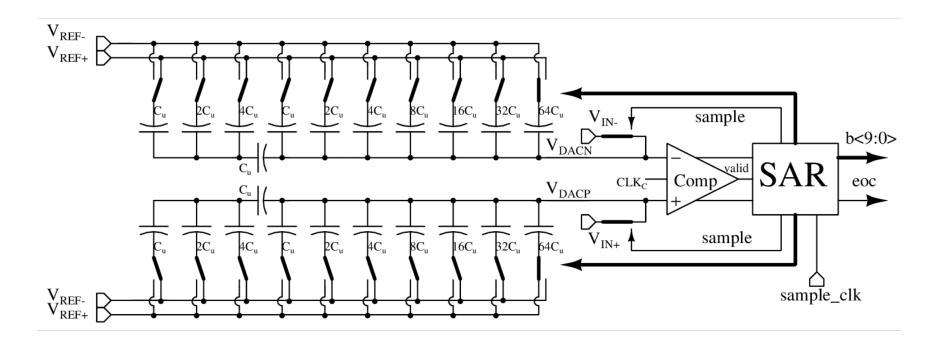

### SAMPA: ADC

• SAR ADC: 80MHZ (Conversion clock) and 10MHz (Sampling Clock)

### **Noise, TPC 20N160 - SAMPLE 057**

### **Noise, TPC 30N160 - SAMPLE 057**

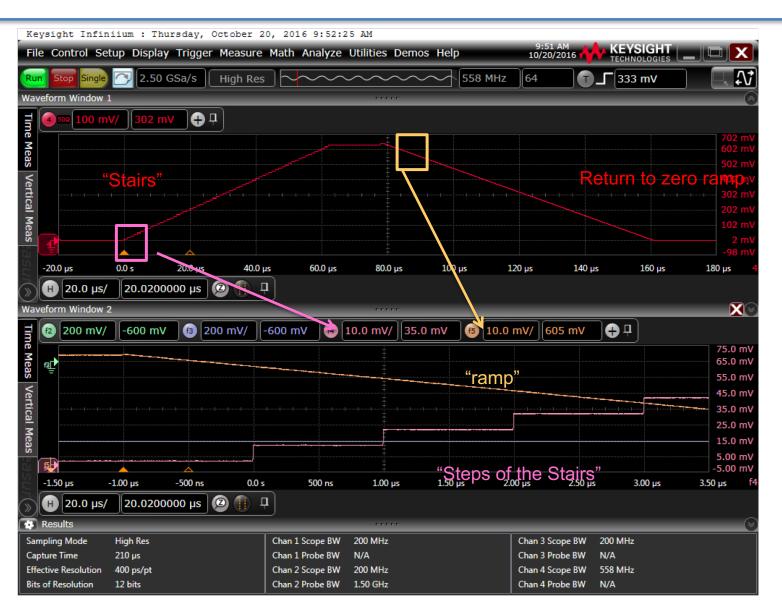

### How to emulate a burst of charge pulses

"stairs-shaped waveform", 63 steps, 1µs apart, + a last one after ~16µs, applied via series C<sub>inj</sub>