# Dedicated front-end chip for BeamCal

34<sup>th</sup> FCAL Collaboration Meeting, March 26-27 2019 @CERN

Matias Henriquez – mjhenriquez@uc.cl

Angel Abusleme – <u>angel@uc.cl</u>

#### BeamCal front-end chip V3 specifications

| Specification        | Value                |

|----------------------|----------------------|

| Q <sub>in</sub>      | > 2.8 fC             |

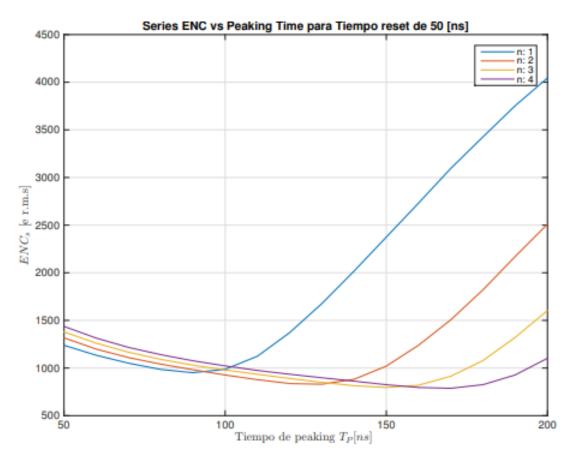

| ENC                  | < 1000 - 1500 e⁻ rms |

| Number of channels   | 8                    |

| Maximum input rate   | 1 / 554ns            |

| Baseline restoration | 1%                   |

- These specs are intended for **testbeam** purposes only

- Specs for calibration and data taking will be defined when the sensors are fully defined

- This ASIC will be a preliminary proof-of-concept

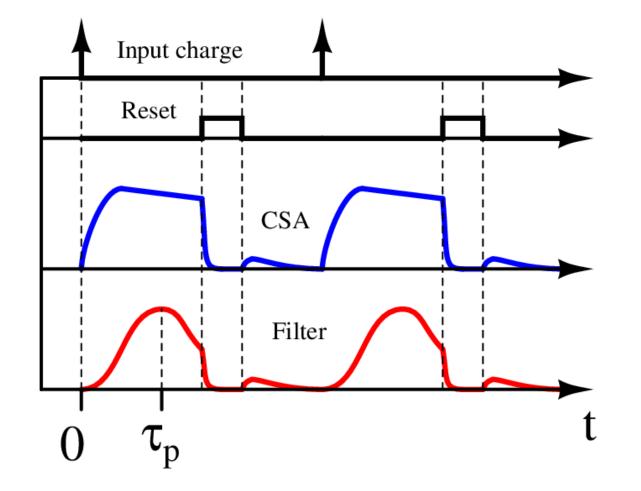

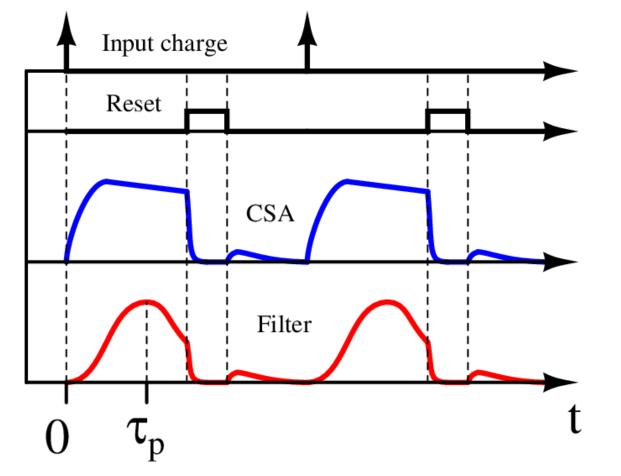

#### Data taking timing diagram – a reminder

- 1. CSA gets input charge

- 2. CSA integrates charge

- 3. Filter produces semi-gaussian shape

- 4. After peaking time, both filter and CSA are reset

- a. CSA returns to baseline instantaneously

- b. Filter returns to zero output instantaneously

- 5. Reset is released

- a. Noise charge is produced and decays due to CSA time constant

- b. Filtered noise charge decays before next input due to filter time constant

#### Testbeam timing diagram - TBD

- Asynchronous scheme

- Several options:

- External trigger may require some work to compensate for trigger delay

- Fast, external ADC and continuous monitoring

- Reset still possible to speed up things

- Deconvolution technique

- ADC rate requirements are relaxed

- Peak detector challenging for such a small (<1-mV) signals

#### Pulse shaper: why an RC implementation?

- Suitable for VLSI process

- Better than discrete-time filters for higher bandwidth applications

- No sampling

- Smooth weighting function

- No extra noi

- Lower power than Gm-C option for same specifications

- Tunability will be done in discrete steps

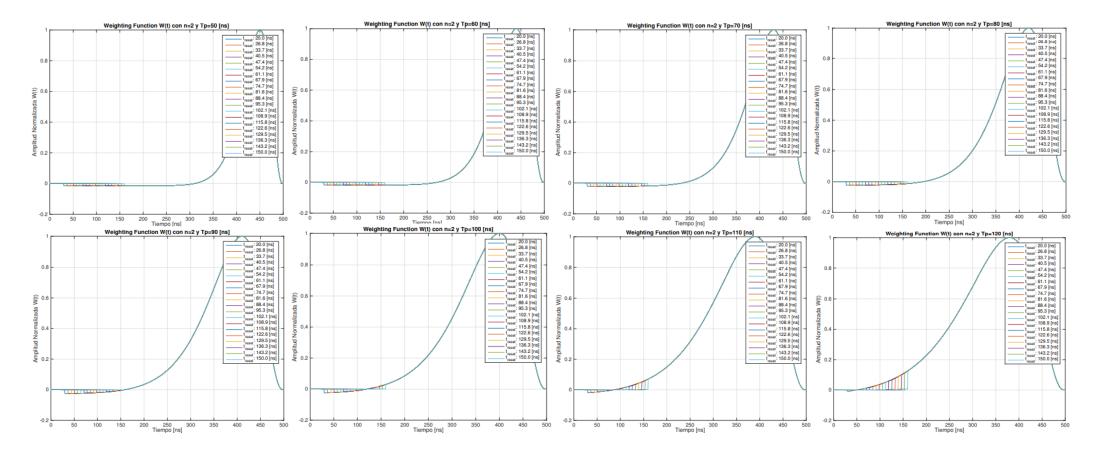

# Several behavioral simulations – different filter order (here n=2) and peaking time

#### Pulse shaper specs (from previous analysis)

- Fully-differential architecture

- 1-V<sub>pp</sub> output for a 1-V<sub>pp</sub> input step

- Peaking time in the range 110 ns – 120 ns

- Output integrated noise less or equal than 244  $\mu V_{rms}$  for a capacitive load of C<sub>L</sub> = 0.4 pF

- Standard 180-nm CMOS process

Can reduce this further by increasing CSA current

#### Shaper transfer function

• The shaper transfer function is

$$H(s) = H_0 \cdot \frac{s\tau_d}{1 + s\tau_d} \cdot \frac{1}{(1 + s\tau_i)^2}$$

- High-pass time constant  $\tau_{d}$

- Low-pass time constant  $\tau_i$

- Passband gain H<sub>0</sub>

- We will use  $\tau_d = \tau_i = \tau = 50$  ns

- Some margin left for CSA settling

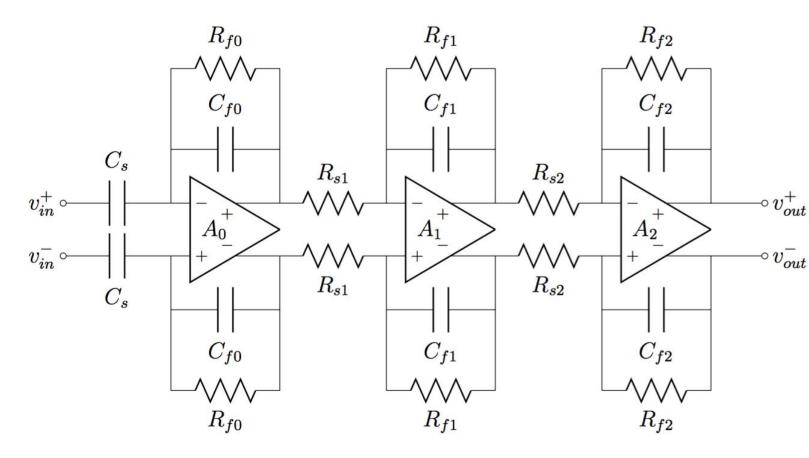

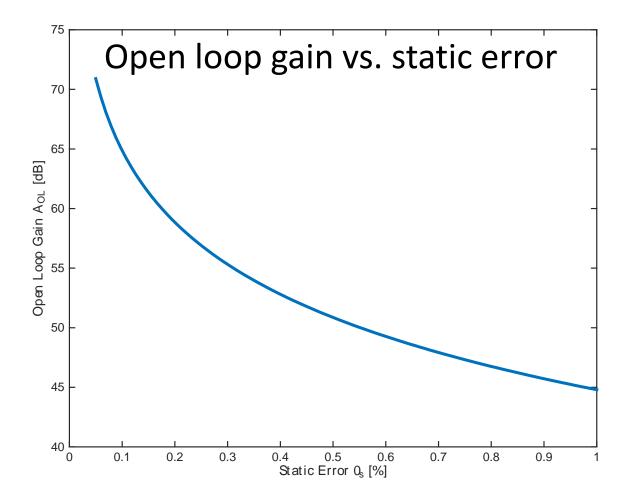

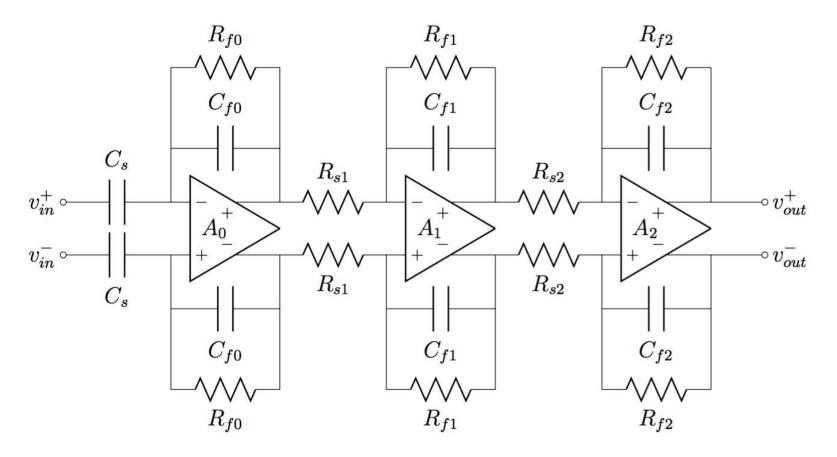

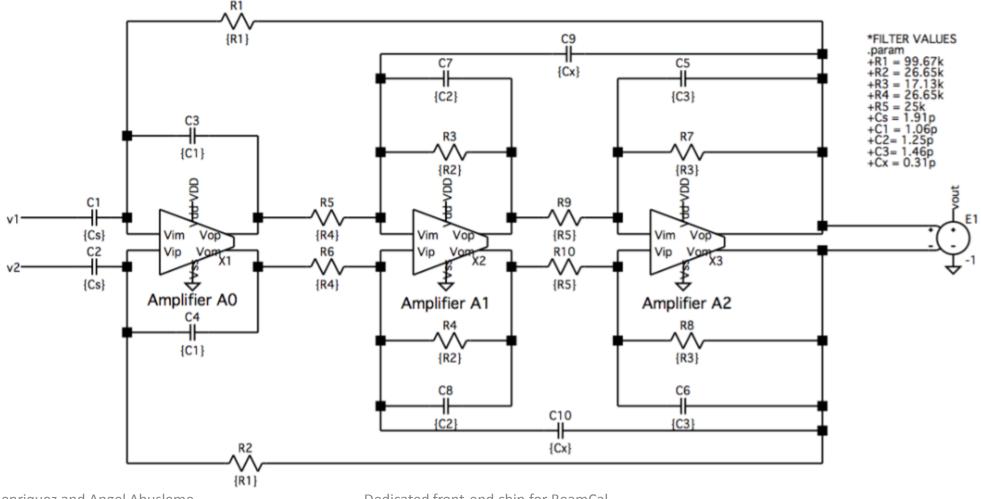

#### Filter architecture

- Fully differential

- SNR, PSRR...

- High-pass on input stage

- Capacitive input impedance

- Filter input common mode becomes independent of the CSA baseline

#### Initial Optimization Procedure

- Resistors and capacitors are carefully chosen – noise considerations

- Amplifier noise can be neglected

- Their contribution can be reduced by increasing the current

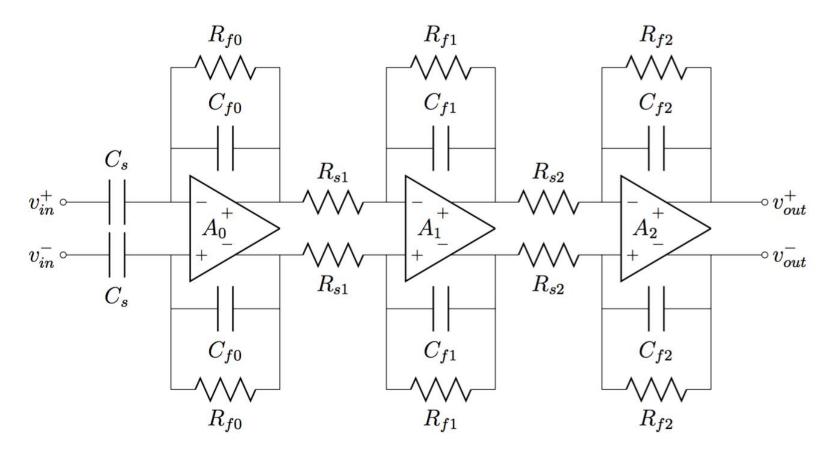

#### Amplifier optimization formulation

mín<sub>x</sub> subject to

- $v_{no,R}^2(\mathbf{x}) \leftarrow C_{total}^m(\mathbf{x}) \leq C_{total}^m$

- $C_{total}(\mathbf{x}) \leq C_{total}^{max},$  $G_0(\mathbf{x}) \leq G_0^{max},$

- $\mathbf{x}_{lb} \leq \mathbf{x} \leq \mathbf{x}_{ub}$ .

- Filter total integrated noise

- Max cap per channel

- Max gain of 1<sup>st</sup> stage, set for rail-to-rail output swing to maximize DR (deGeronimo 2011)

- x is a vector that includes the amplifier closed-loop gains and resistor values

#### Noise as function of $C_{total}^{max}$ and $G_0^{max}$

#### Opamp or OTA?

- In principle, Opamp deals with resistive loading... but increased power consumption

- Does not matter as long as effective transconductance is large enough (Tsividis, 1994)

- So we go for an OTA (Miller 2-stage)

|                                                   | I <sub>TOT</sub><br>mA | dv <sub>in,eq</sub> <sup>2</sup><br><u>8/3 kT df</u><br>g <sub>m1</sub> | Swing    |

|---------------------------------------------------|------------------------|-------------------------------------------------------------------------|----------|

| Volt. OTA (4 Ts)                                  | 0.25                   | 4                                                                       | avg.     |

| Symmetrical (B= 3)                                | 0.33                   | 16                                                                      | max.     |

| Telescopic                                        | 0.25                   | 4                                                                       | small    |

| Folded casc.                                      | 0.5                    | 4                                                                       | avg.     |

| Miller 2-stage (C <sub>L</sub> /C <sub>c</sub> =2 | 2.5) 1.1               | 4 Be                                                                    | est max. |

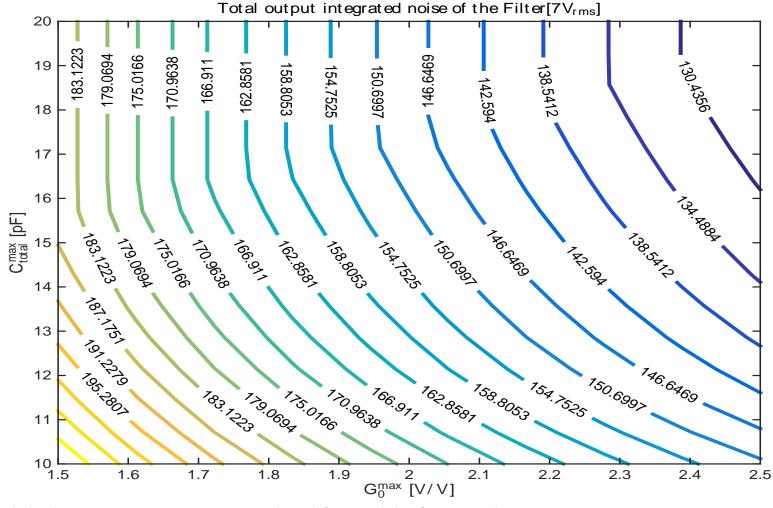

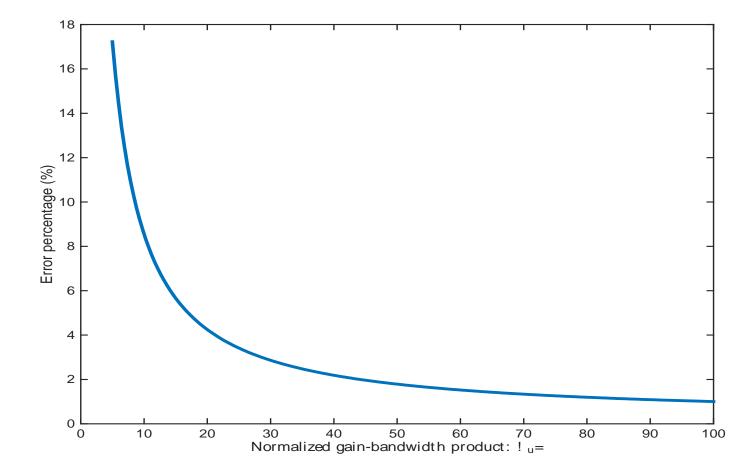

#### Effect of finite open-loop gain of OTA

#### Effect of finite OTA bandwidth on 3<sup>rd</sup> stage

#### Third stage design is critical

- Final filtering stage

- Therefore, highfrequency poles and zeroes do matter

- This amplifier noise contribution is dominant

- Can be reduced by increasing Cc

$$A_2 \text{ Input-referred noise}$$

$$\overline{v_{in,Amp}^2}(s) \approx \overline{v_{n1}^2} + \left(\frac{g_{m3}}{g_{m1}}\right)^2 \overline{v_{n3}^2} + \frac{(1+s/z_1)^2}{A_1^2} \cdot \left(\overline{v_{n2}^2} + \left(\frac{g_{m4}}{g_{m2}}\right)^2 \overline{v_{n4}^2}\right)$$

- Valid for frequencies below GBW

- $z_1 < GBW$  in output impedance expression due to  $C_1 + C_c$

- Noise contribution becomes significant

- z<sub>1</sub> should be pushed towards the GBW by reducing C<sub>1</sub>

- Min-length transistor in 2<sup>nd</sup> stage transconductor to reduce C<sub>1</sub>

- 1<sup>st</sup> stage in moderate inversion to ensure high gain

- $C_c$  as large as possible here fixed to 2.5 pF

#### A<sub>2</sub> amplifier design

| Specification          | Expected value (MATLAB) | LTSpice             |

|------------------------|-------------------------|---------------------|

| A <sub>OL</sub>        | >60dB                   | 62.78dB             |

| GBW                    | 112.65MHz               | 100MHz              |

| <i>I</i> <sub>D1</sub> | 148.81µA                | $151.12\mu A$       |

| I <sub>D2</sub>        | 274.42µA                | 277.06µA            |

| PM                     | 70°                     | 73°                 |

| au                     | 52.5 ns                 | 52.53 ns            |

| $v_{no,Amp}^2$         | $102.79 \mu V_{rms}$    | 142.5 $\mu V_{rms}$ |

Comparative table between simulation results and expected values from MATLAB, for designed amplifier  $A_2$ .

Matias Henriquez and Angel Abusleme

#### A<sub>1</sub> amplifier design

| Specification          | Expected value (MATLAB) | LTSpice      |

|------------------------|-------------------------|--------------|

| A <sub>OL</sub>        | $\geq$ 62dB             | 61.99dB      |

| GBW                    | 112.65MHz               | 118.4MHz     |

| <i>I</i> <sub>D1</sub> | 25.62µA                 | 27.11µA      |

| <i>I</i> <sub>D2</sub> | 179.73µA                | $177.2\mu A$ |

| PM                     | $\geq 62^{\circ}$       | 66,26°       |

| au                     | 52.9 ns                 | 54.5 ns      |

Comparative table between simulation results and expected values from MATLAB, for designed amplifier  $A_1$ .

Matias Henriquez and Angel Abusleme

Dedicated front-end chip for BeamCal

$A_0$  amplifier design

In highpass configuration

- Maximize GBW

- Derivative function

- High slew rate

| Specification          | Expected value (MATLAB) | LTSpice         |

|------------------------|-------------------------|-----------------|

| A <sub>OL</sub>        | $\geq$ 65dB             | 64.17dB         |

| GBW                    | 160MHz                  | 146.1MHz        |

| <i>I</i> <sub>D1</sub> | 75µA                    | 76.04 <i>µA</i> |

| I <sub>D2</sub>        | 224.08µA                | 226.33µA        |

| PM                     | ≥ <b>70</b> °           | 87°             |

| au                     | 53.4 ns                 | 57 ns           |

| $\epsilon_s$           | 6.32 %                  | 7.14 %          |

Comparative table between simulation results and expected values from MATLAB, for designed amplifier  $A_0$ .

Matias Henriquez and Angel Abusleme

Dedicated front-end chip for BeamCal

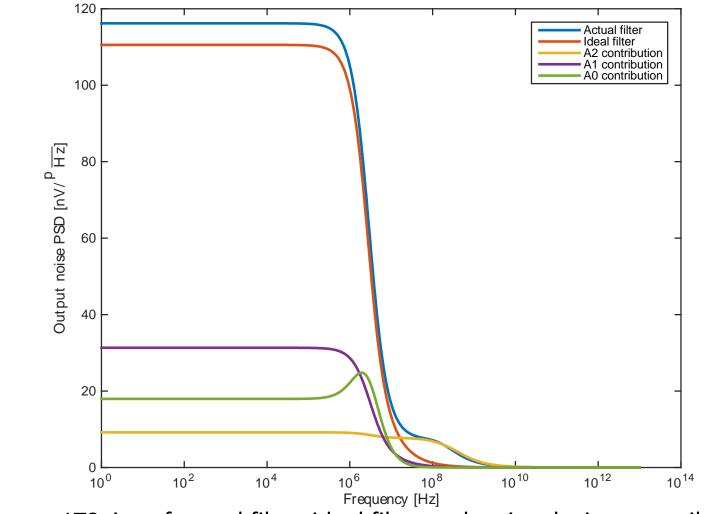

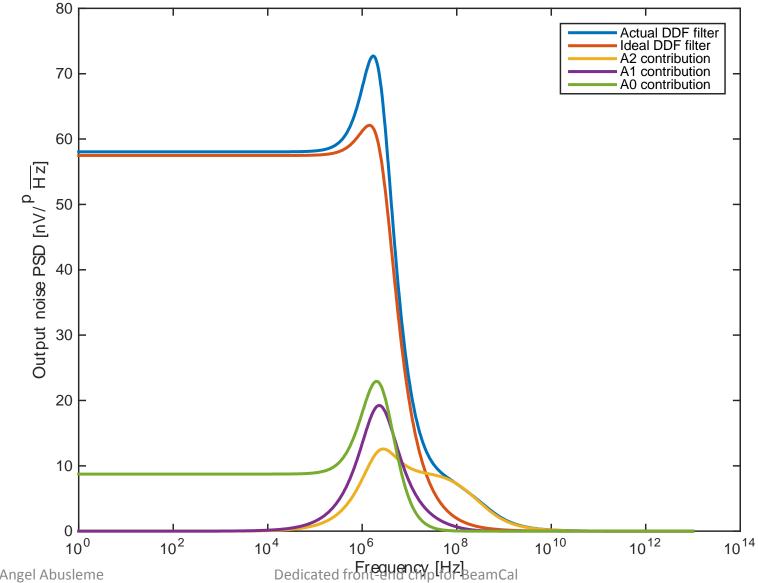

#### Amp noise contribution – simulation results

.noise simulation on LTSpice of actual filter, ideal filter and active devices contributions

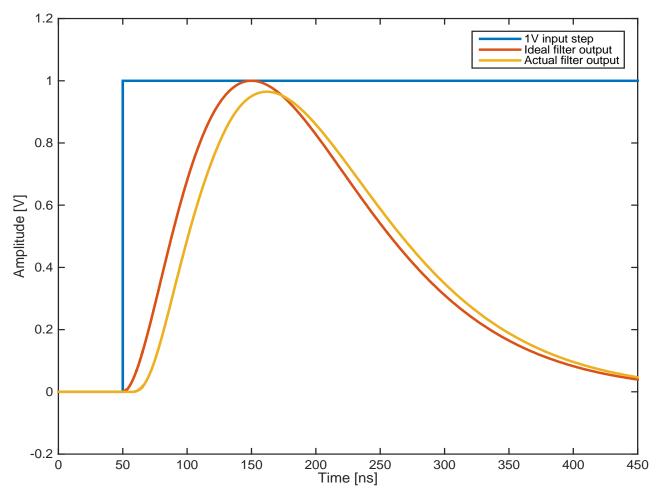

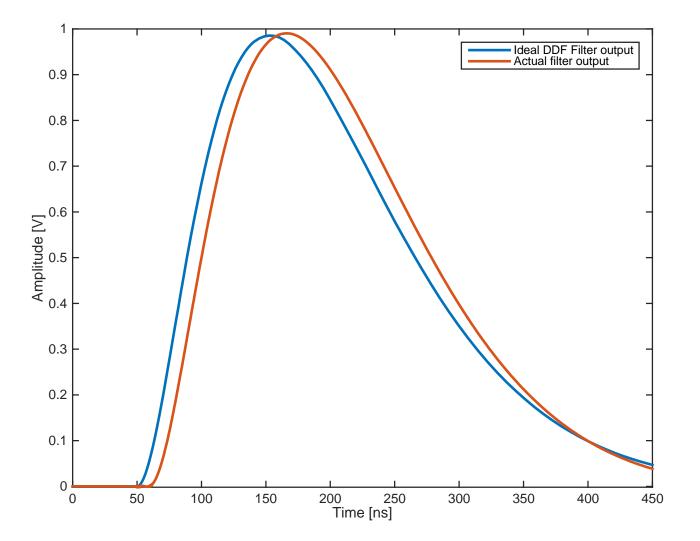

#### Transient simulation results

#### .tran simulation on LTSpice of actual filter, ideal filter and input step applied

Matias Henriquez and Angel Abusleme

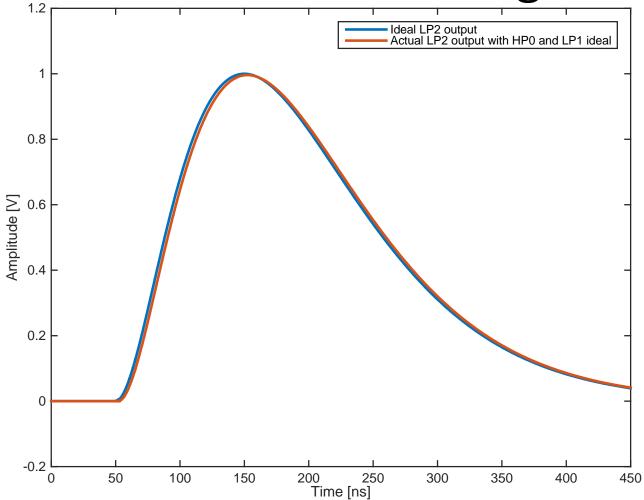

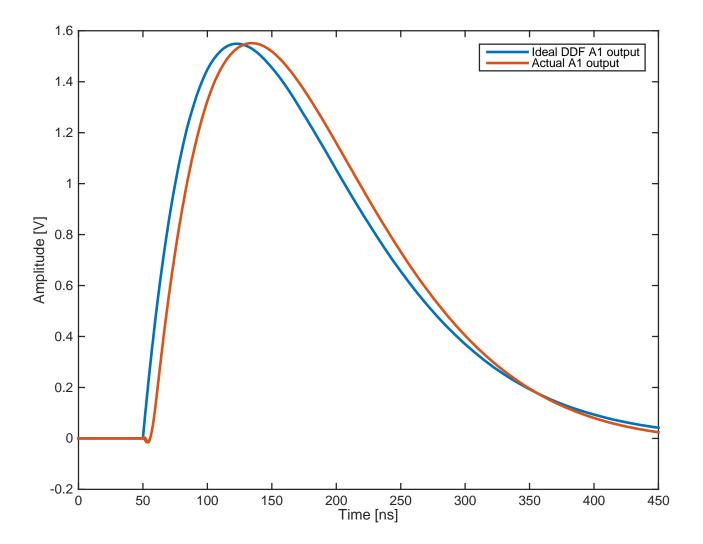

#### Transient simulation – third stage output

.tran simulation on LTSpice of third stage compared to ideal third stage when first and second stages are ideal

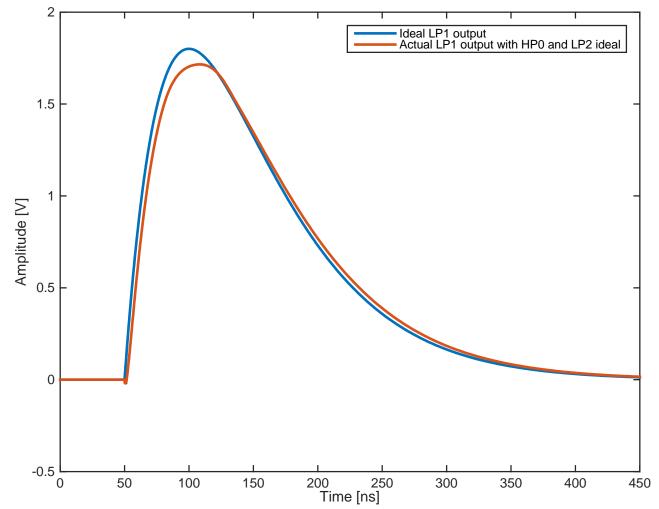

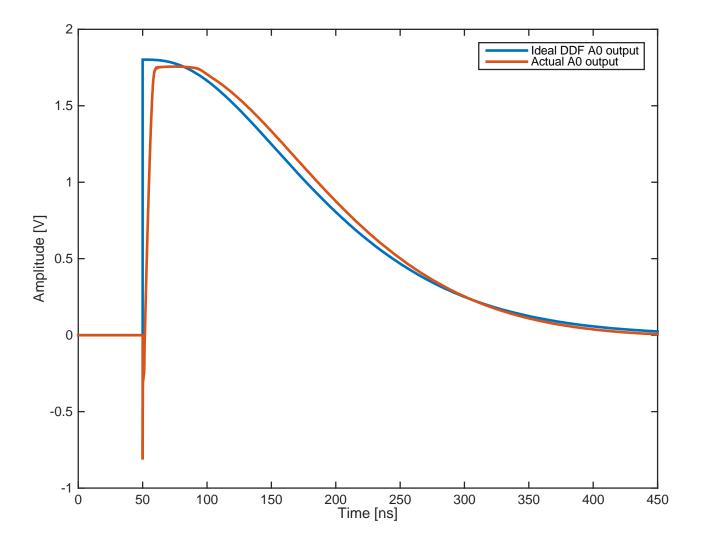

#### Transient simulation – second stage output

.tran simulation on LTSpice of second stage compared to ideal second stage when first and third stages are ideal

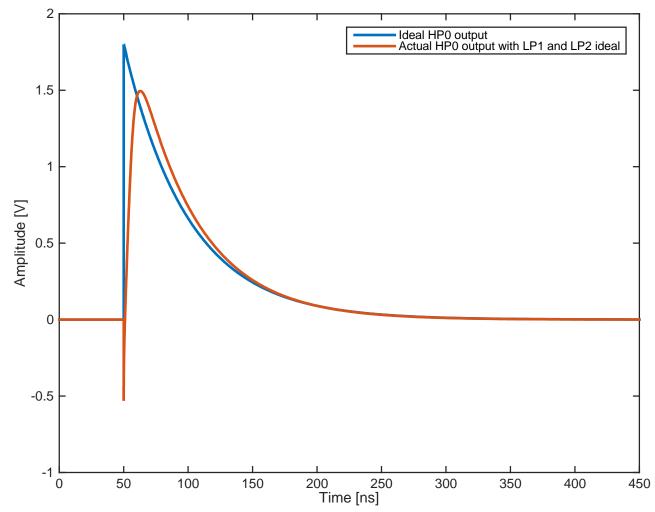

#### Transient simulation – first stage output

.tran simulation on LTSpice of first stage compared to ideal first stage when second and third stages are ideal

#### Current status and future milestones

- Filter circuit-level design is complete

- Several ideas were considered and discarded

- Gm-C filter, Dissipative delayed feedback, discrete time...

- Now fully working on layout

- Tapeout scheduled for May 29<sup>th</sup>

- Board design and testing in June-July

- Chip testing August-November

# Thanks for your attention

## DDF: Dissipative Delayed Feedback (DeGeronimo, 2011)

#### **DDF:** Noise simulations

#### DDF - Transient Simulations – Filter's output

#### DDF - Transient Simulations – A1's output

#### DDF - Transient Simulations – A0's output

### References

- (DeGeronimo, 2011) G. De Geronimo and S. Li, Shaper Design in CMOS for high Dynamic Range, IEEE Transactions on Nuclear Science 58 (2011), nº 5, 2382-2390.

- (Gray, 2009) P.R. Gray, Analysis and Design of Analog Integrated Circuits, 5<sup>th</sup> Edition, Wiley Global Education, 2009.

- (Sansen, 2006) W.M.C Sansen, Analog Design Essentials, The Springer International Series in Engineering and Computer Science, Springer US, 2006.

- (Tsividis, 1994) Y.P. Tsividis, Integrated Continuous-Time Filter Design – An Overview, IEEE Journal of Solid-State Circuits 29 (1994), nº 3, 166-176.

- (TSMC, 2019) TSMC 0.18-micron Technology, Tech. report, TSMC, 2019.

Matias Henriquez and Angel Abusleme