# EMBEDDING MICROFLUIDICS INTO MICROELECTRONICS

WP9: New support structures and micro-channel cooling

RICCARDO CALLEGARI, ROBERTO CARDELLA 02/04/2019

#### LAST YEAR

https://indico.cern.ch/event/677272/contributions/2976451/attachments/1638712/2615630/AIDA2020 status update.pdf

Microchannels etched on a 4" silicon wafer and sealed with a glass wafer through anodic bonding process (350 °C) (close collaboration with Center of Micronanotechnology at EPFL)

150 um

Microchannels etched on a 8" silicon wafer and sealed with another silicon wafer through direct bonding process (1050

°C) (external partners)

Silicon wafer

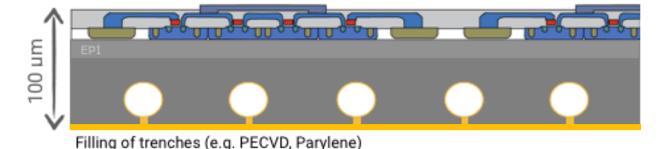

Microchannels without bonding process: buried channels (300 °C) (just mentioned last year)

M. Boscardin et al., *Silicon buried channels for pixel detector cooling*, Nuclear Instruments and Methods in Physics Research, Section A, 2013

C. Lipp, *Approaches for the fabrication of silicon buried channels for the thermal management of monolithic pixel detectors*, MSc Thesis, EPFL, 2017

200 x 70 μm

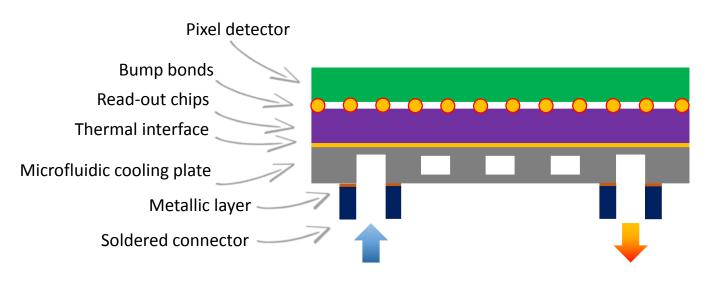

#### MICROFLUIDIC COOLING PLATES FOR NA62 AND LHCB (ON HYBRIDS)

2010: start of the R&D campaign

2014: first detector with cooling plates (NA62) 2021: integration of cooling plates in LHCb

#### On going research at CERN (on monolithics)

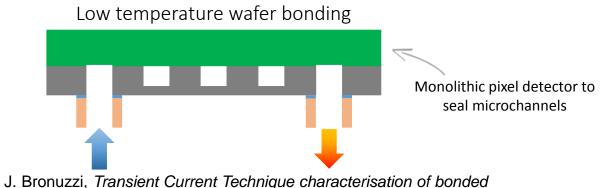

J. Bronuzzi, *Transient Current Technique characterisation of bonded interfaces for monolithic silicon detectors*, PhD Thesis, EPFL, 2018

R. Callegari, *Integration of a microfluidic circuitry in a CMOS device operating in HEP experiments*, MSc Thesis, Università di Genova, 2018

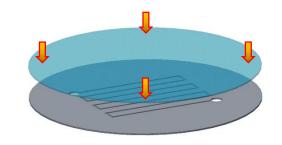

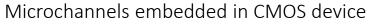

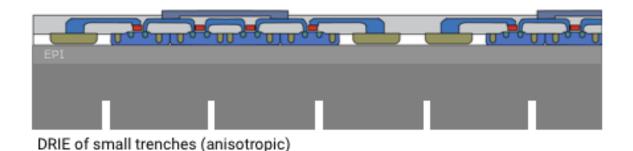

## Microchannels etched directly on the backside of a monolithic pixel detector (MALTA: Monolithic from ALice To Atlas)

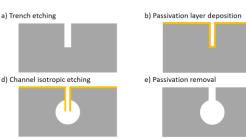

A pattern of small trenches (3 x 10  $\mu$ m) is etched on the backside of the pixel detector to a depth of 30  $\mu$ m

Ebi

Microchannels are etched isotropically with XeF2 from the bottom of the trenches.

Diameter of the microchannels = 40  $\mu$ m Overall depth of the microfluidic circuitry = 50  $\mu$ m

XeF<sub>2</sub> etching of microchannels (isotropic)

A thin film of parylene (5  $\mu$ m) seals the microchannels. It is finally cured by a thermal cycle.

I. Berdalovic et al., Monolithic pixel development in TowerJazz 180 nm CMOS for the outer pixel layers in the ATLAS experiment, JINST 13 C01023, 2018

#### MICROFLUIDIC CONNECTION

https://indico.cern.ch/event/677272/contributions/2976453/attachments/1638722/2615654/AIDA2020\_connectors.pdf

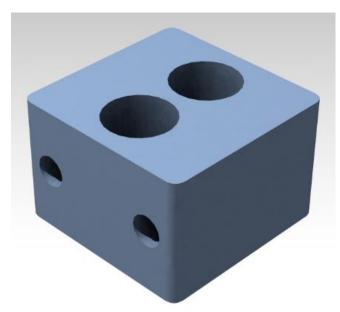

#### 3D printed with Formlabs SLA:

- Cheap

- Fast

- Easy

- Shapes difficult to achieve with conventional machining

#### But...

Lack of dimensional repeatability

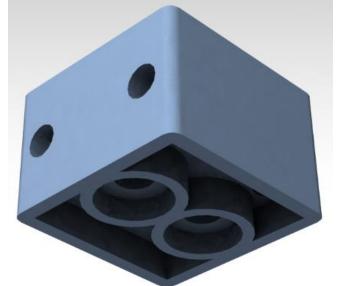

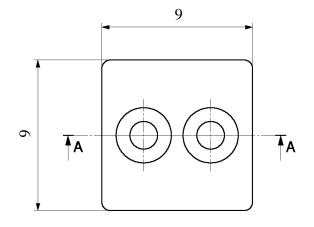

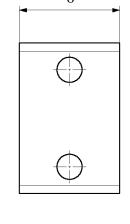

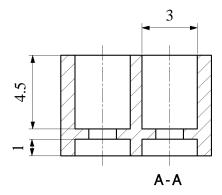

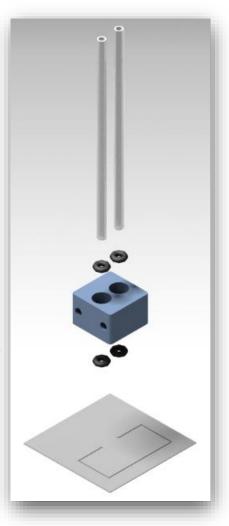

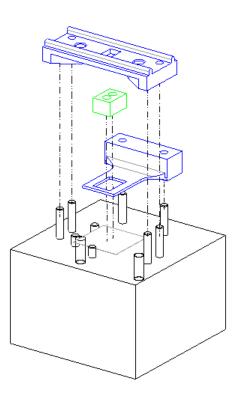

#### ASSEMBLY PROCEDURE

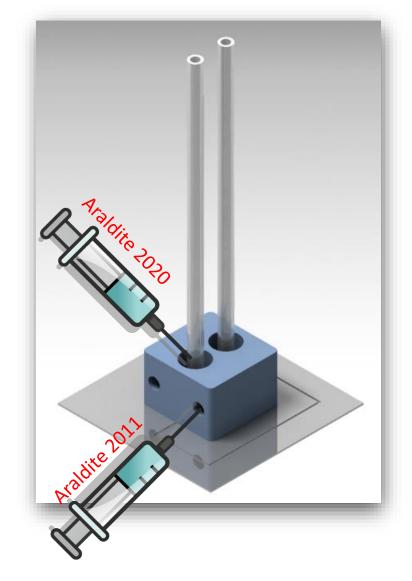

- The plastic capillaries are glued to the connector

- The connector is glued to the silicon chip

- Bottom o-rings prevent liquid leakages

- Top o-rings prevent glue infiltration

- Blue parts: 3D printed

- Black parts: machined

- Green part: connector (3D printed)

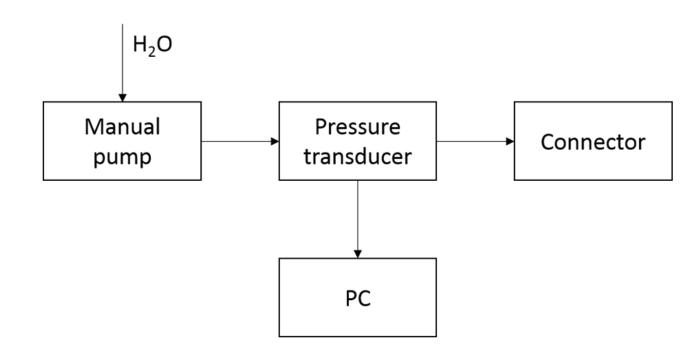

#### CONNECTOR CHARACTERIZATION

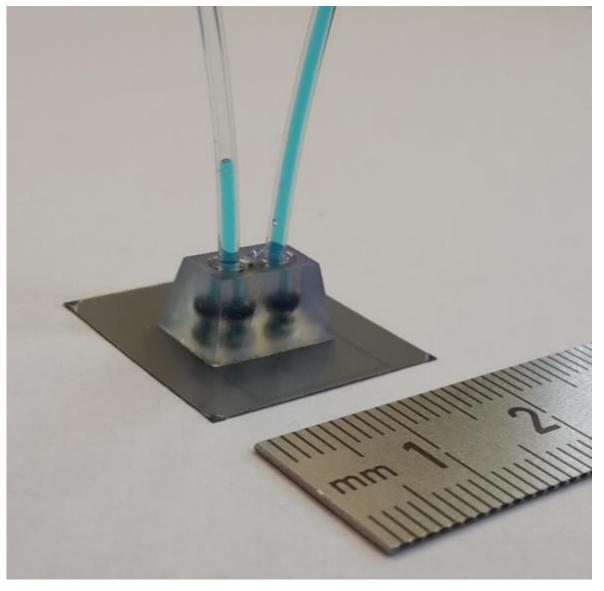

Connector glued on a blank piece of silicon:

Helium leak rate: L<sub>He</sub>≈10<sup>-8</sup> mbar · I / s

• Failure pressure: p<sub>max</sub>= 110 bar

#### CIRCULATION DEMONSTRATED

Microchannels and connector integrated into a 100  $\mu m$  thick CMOS device

A fully CMOS-compatible microfabrication process to embed microchannels has been validated

- As a post-process

- At a die level

- In an extremely thin substrate

- In an operating device

## INTEGRATION WITH THE PCB (ONGOING)

#### First line of investigation:

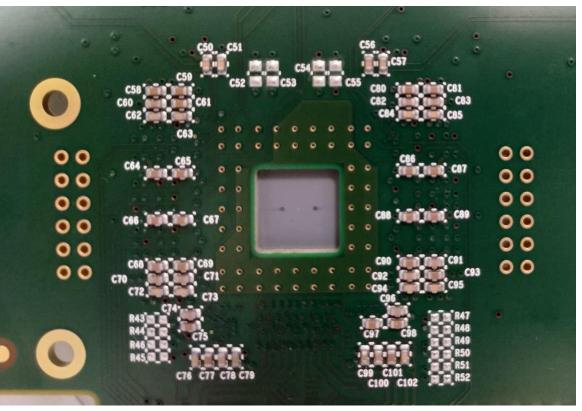

Characterisation of a fully functional MALTA pixel chip with embedded micro channels to study possible effects of the post-processing

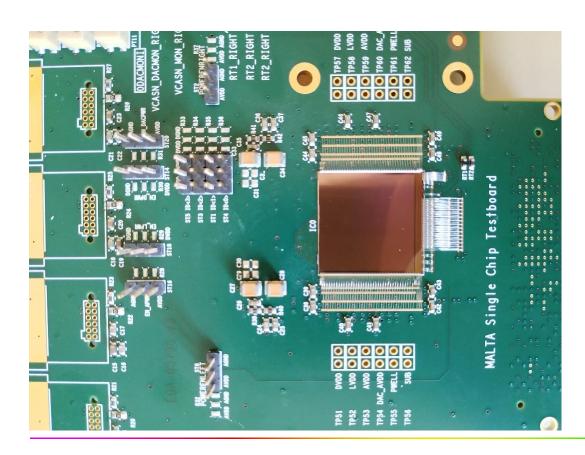

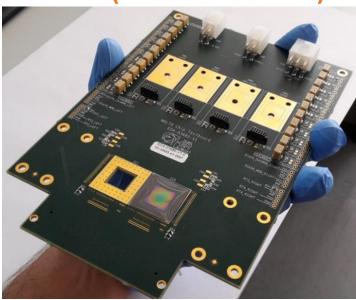

The first MALTA chip with embedded micro channels (without connectors) has been mounted on a PCB and wire bonded

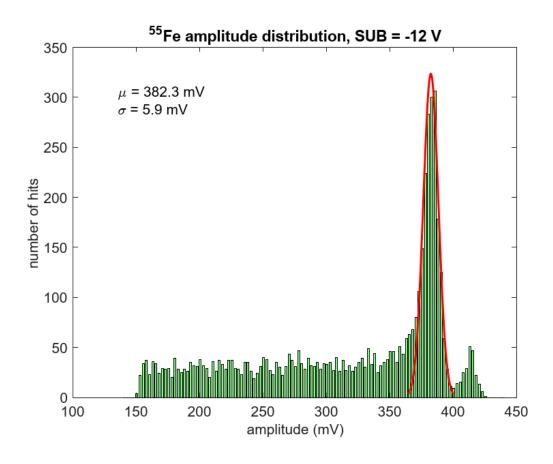

## IRON SOURCE SCAN (PRELIMINARY)

Preliminary electrical tests and source scans using a 55Fe source show a similar behaviour as in standard MALTA chips. Further tests are planned in the near future including measurements in a testbeam

## INTEGRATION WITH THE PCB (ONGOING)

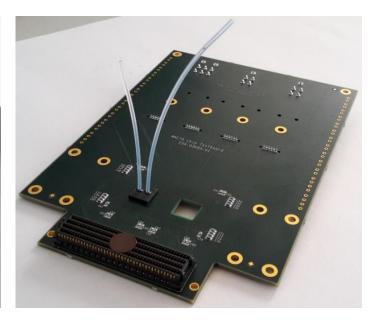

Next step:

Thermo-fluidic measurements for on-detector cooling

Helium leak rate:  $L_{He} \approx 10^{-7} \text{ mbar} \cdot \text{l/s}$

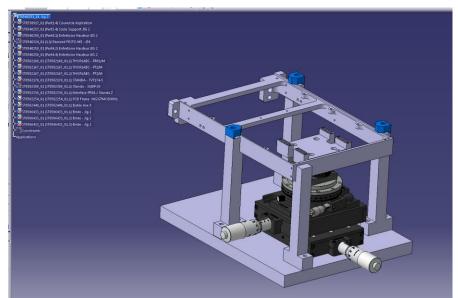

Alignment jig of the GTK for NA62

To be able to perform the wire bonding over an assembled chip a jig is required (under development).

Three axis translation stages + rotation

A tailor-made clamp for the connector has to be designed

#### CONCLUSIONS

A CMOS-compatible microfabrication process to embed microchannels into microelectronics has been developed. It allows to minimize more and more the overall thickness, getting rid of any thermal interface between the electronics and the cooling system.

A 3D printed microconnector, with the purpose of a test vehicle, has been validated. Optimization is required to reduce the amount of material.

Electrical, thermal and fluidic characterizations are ongoing.