# Development of a pixelated readout ASIC for CZT detectors for spectral X-ray photon-counting imaging applications

Tsinghua University

Xuezhi Wang<sup>1,2</sup>,Wei Liu<sup>1,2</sup>, Zhi Deng<sup>1,2</sup>, Yinong,Liu<sup>1,2</sup> <sup>1</sup> Department of Engineering Physics, Tsinghua University, Beijing, China <sup>2</sup>Key Laboratory of Particle & Radiation Imaging, Ministry of Education, Beijing, China

### Introduction

- Spectral X-ray Photon-counting imaging

- Noise suppression

- Image quality

- · Material discrimination

- Cadmium Zinc Telluride(CdZnTe)

- · High atomic number

- Proper band-gap energy

- Operational at room temperature

- · Ideal for hard X-ray and gamma-ray detection

- Pixelated readout ASIC

# Architecture and Specification

#### ■ Overall architecture

### ■ Main design specifications

| design specification | value                          |

|----------------------|--------------------------------|

| pixel size           | $100\mu m \times 100\mu m$     |

| array                | 32 ×32                         |

| power consumption    | $<100\mu W/pixel$              |

| gain                 | 70mV/fC                        |

| dynamic range        | 10fC                           |

| ENC                  | $<100e^{-}$ @ $C_{in} = 100fF$ |

| pulse width          | 200ns                          |

| energy window        | 2                              |

| counter              | 12bit                          |

| readout frame rate   | 1kHz                           |

- the pixel array makes the majority of the ASIC

- End-Of-Column(EOC) circuit is placed on the bottom

## ASIC Design

- Pixel circuit

- Block diagram

- One low-noise charge sensitive preamplifier

- One CR-RC shaper

- Two discriminators

- Two 12-bit counters

- Several registers

- EOC circuit

- Bias generation

- Slow control

- Data readout control

# Layout

- The analog part and the digital part are divided by slow control registers

- Mirror placement of two adjacent columns of pixels

### **Test Systems**

## **Contact Information**

Xuezhi Wang, PhD student, wang-xz18@mails.tsinghua.eud.cn Wei Liu, PhD Candidate, <a href="mailto:lwphysics@163.com">lwphysics@163.com</a> Zhi Deng , Associate Professor, dengz@mail.tsinghua.edu.cn

### Test Results

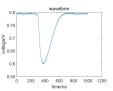

#### ■ Waveform

- Pulse width=200ns

- Power consumption

power consumption=38.9uW/pixel

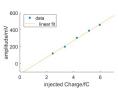

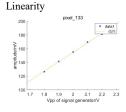

## ■ Gain

(Estimated ) gain =79.8mV/fC

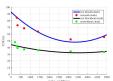

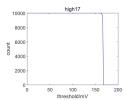

#### ■ Noise

ENC < 100 electron

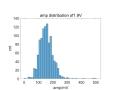

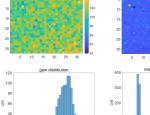

#### ■ S-curve fit

S-curve

- Measured with different amount of charge injection

- Fitted with Gaussian cumulative distribution

- Sigma: spread of the signal amplitude

- mu: average value of the signal amplitude

#### Average value distribution

- Each pixel: average value versus the amount of charge injection

- Fitted with linear functions

- slope: charge-amplitude gain

- intercept: uniformity of baseline

# Summary & Future Plan

- A pixelated photon-counting ASIC was developed. The prototype chip was evaluated. The power consumption was measured to be 38.9uW per pixel. The gain of the analog frontend was approximately 79mV/fC and the ENC was less than 100 electrons for different shaping times and the input capacitance of about 100 fF. The results showed that our chip worked well and agreed with our design specifications.

- Test of the new version prototype chip with larger pixel array and more functions.

- Test of the prototype chip bump bonded with CdZnTe detector.