# HMPID Trigger during Run3

HMPID Plenary Meeting 14/12/2018

J.L. Gauci University of Malta

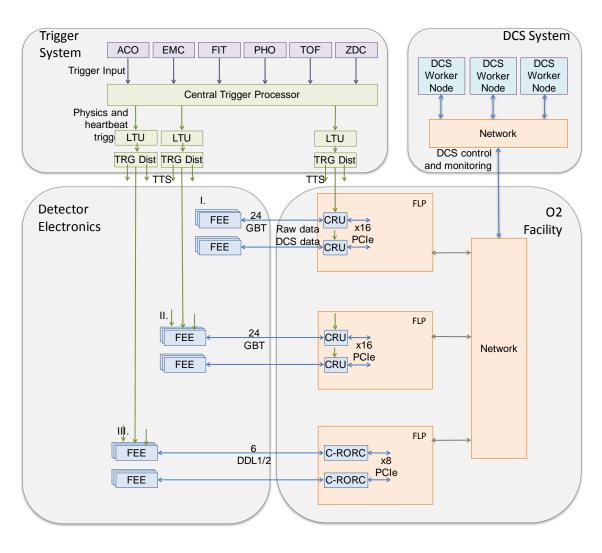

## Triggering in Run3

- CTP will produce trigger signals

- LM, L0, L1 with several latencies

- In addition CTP will produce the HB trigger and other software triggers.

- All trigger types are sent via LTU and TTS

### HMPID in Run3

#### • HMPID Requirements:

- LO signal at ~1.2 us after an event when charge on the pads is at its peak

- Message to be able to assemble header for data transfer

- Run3 triggering for detectors with TTC System

- One synchronous trigger via channel A, sent at LM, L0 or L1 time

- An asynchronous message in channel B, containing the trigger data sent from CTP at L1 time

- HMPID will also receive an LM trigger via LVDS cables

#### HMPID in Run3

#### Why LM?

- L0 signal arrives at CTP at 1200 us

- It arrives at our detector (over TTC) at ~1.7 us, which would be too late for us

- Solution is to use LM which arrives at the detector at ~835 ns

| Time             | Total Latency (ns) | Description                        |

|------------------|--------------------|------------------------------------|

| $425\mathrm{ns}$ | $425\mathrm{ns}$   | LM input to CTP board              |

| $100\mathrm{ns}$ | $525\mathrm{ns}$   | CTP Processing Time                |

| $125\mathrm{ns}$ | $650\mathrm{ns}$   | CTP-LTU Fan-Out Time               |

| $25\mathrm{ns}$  | $675\mathrm{ns}$   | LTU Processing Time                |

| $160\mathrm{ns}$ | $835\mathrm{ns}$   | Propagation Time from LTU to HMPID |

**Table:** Calculating the propagation time of LM via LVDS

#### HMPID in Run3

- Upgrades to HMPID are twofold:

- 1. New Fan-In/Fan-Out module for precise control on the delay, distribution of LM and fan-in of BUSY

- 2. Upgrades of Firmware to handle trigger message

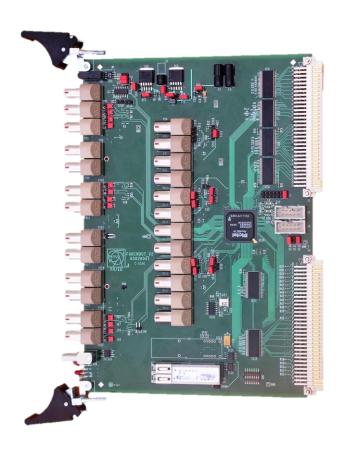

## Fan-In/Fan-Out Module

#### Current Module:

• Delay Range: 2.5 us

• Delay Resolution: 25 ns

#### Improved Module

• Delay Range: 525 ns

• Delay Resolution: 1 ns

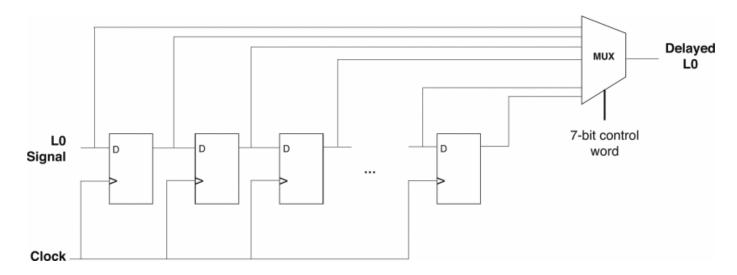

## Design and Implementation

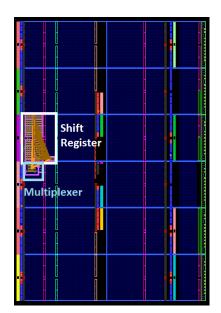

- Tapped Shift Register Based Architecture with a multiplexer.

- Implementation in Xilinx Virtex 5 FPGA

Figure: Implementation of Digital Delay Line

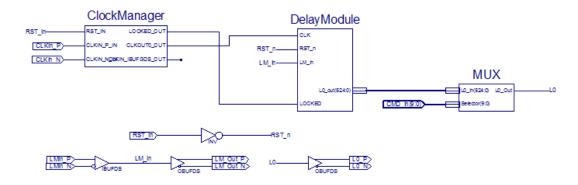

## Design and Implementation

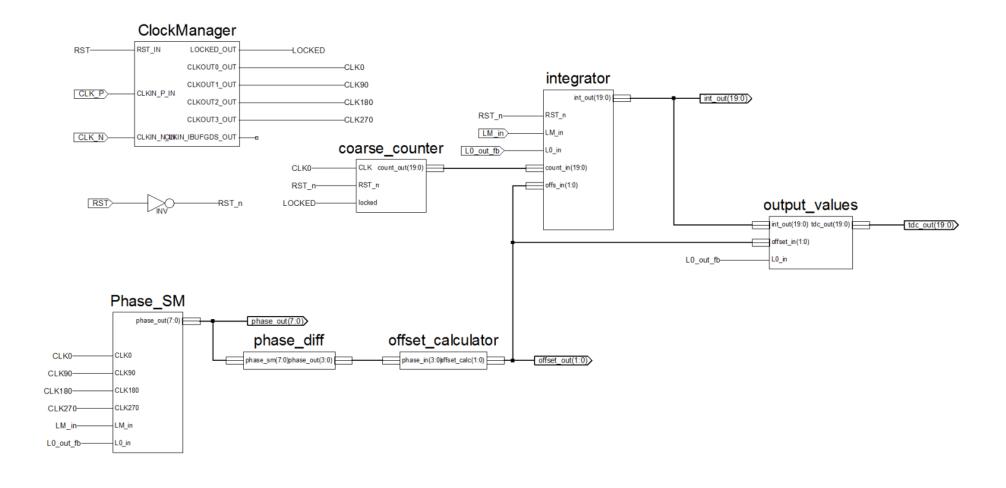

- ClockManager 1 GHz Clock Generator

- Delay Module Shift Register

- MUX Multiplexer

Floorplanning to constrain occupied area by the Shift Register

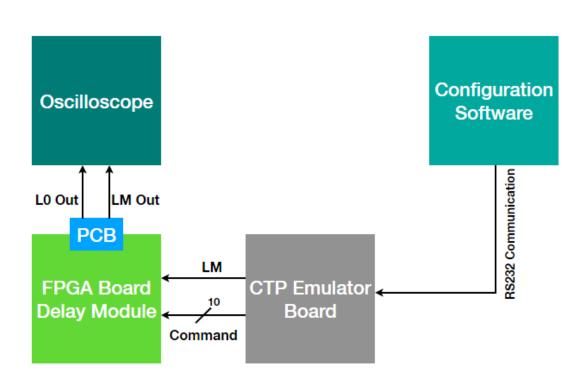

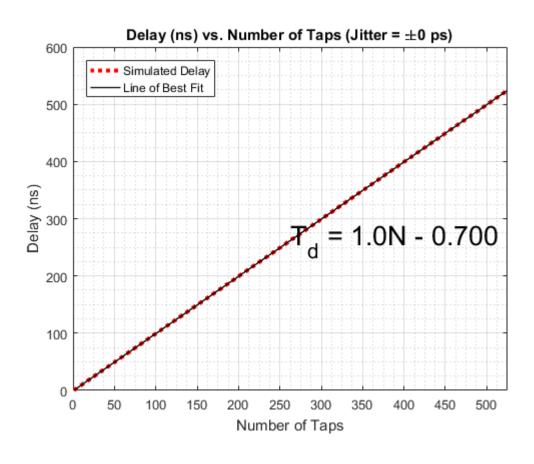

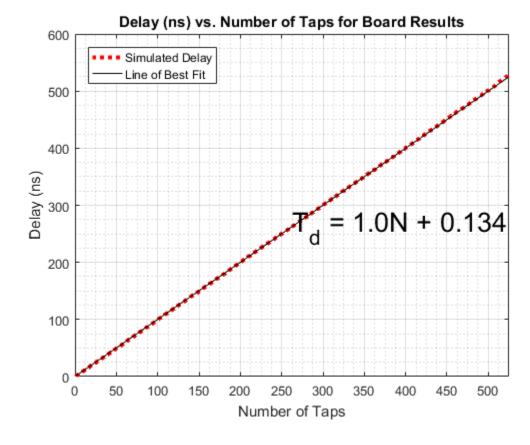

## Testing

### Results

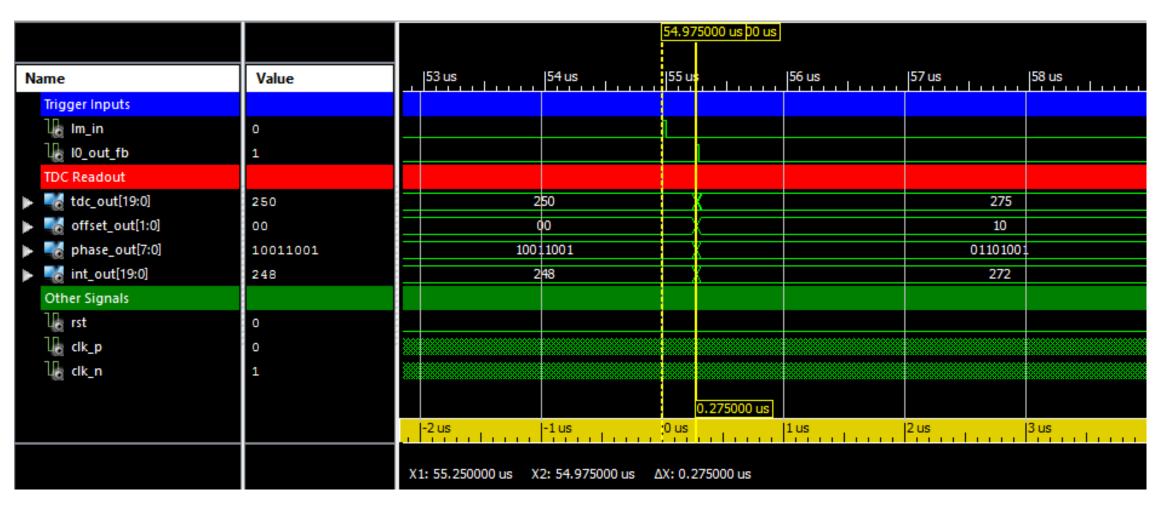

## Monitoring Module

- Problem with this delay line is that there is an unpredictable offset.

- Stems from the accumulation of jitter along the line

- One Solution is to use a control loop to monitor the delay and correct the multiplexer code, if the delay is more than +/- 1 ns

## Monitoring Module

## Monitoring Module - Results

## Firmware Upgrades

- Tests in Bld 581 on present Firmware were performed by Raul and myself

- Problem with v27 VHDL conversion of header module

- Solved by changing header block to AHDL

- No more corrupted header received

- Problem with errors in hardware?

- Yes and No. Most probably what is resulting in errors from TB is the fact that we are running firmware from P2

- New Firmware so far:

- Changed from unreliable reset module clock to one generated by PLL

- Started new TTC module

#### New TTC Module Run3

- Writing of new TTC module for Run3 underway

- Data Format for Run3

| Data  | Word Number | Payload     | Content      |

|-------|-------------|-------------|--------------|

| [015] | x           | TType[015]  | Trigger Type |

| [011] | x           | BCID[011]   | BCID         |

| [015] | x           | Orbit[015]  | Orbit Low    |

| [015] | x           | Orbit[1631] | Orbit High   |

$63\ 62\ 61\ 60\ 59\ 58\ 57\ 56\ 55\ 45\ 3\ 52\ 51\ 50\ 49\ 48\ 47\ 46\ 45\ 44\ 43\ 42\ 41\ 40\ 39\ 38\ 37\ 36\ 35\ 34\ 33\ 32\ 31\ 30\ 29\ 28\ 27\ 26\ 25\ 24\ 23\ 22\ 21\ 20\ 19\ 18\ 17\ 16\ 15\ 14\ 13\ 12\ 11\ 10\ 9\ 8\ 7\ 6\ 5\ 4\ 3\ 2\ 1\ 0$

HB or Physics trigger

#### New TTC Module for Run3

- Handles LO, L1 sequence

- Handles HB Trigger even when BUSY

- Header Builder by filling in respective values of the CDH

No way of testing this so far as I cannot build a fake trigger message using the CTP Emulator.

### Plans for 2019

#### January 2019

- We should have the new lab completed with Run3 LTU and C-RORC.

- In this way we can test the various functionalities of the new firmware.

- Tests at P2 of porting to VHDL (Run2 environment)

- Final Design and Prototype of Fan-In/Fan-Out Module

- Final Prototype of Run3 Firmware